This is NOT a Design Challenge. But it involves a challenge. So, what is the Path II Programmable? Here's the story...

Origins of the Project

About two years ago, the element14 team turned its attention to Programmable Logic Devices such as FPGAs and heterogeneous SoCs. We saw these devices as an area of electronics that deserved a lot more attention on the community. Thus, we began sponsoring discussions on designing with programmable logic devices, and with the help of Xilinx and Avnet, we sponsored RoadTests and hosted webinars. But it was really our members' comments about the challenges of developing with these devices that motivated us to launch this training project.

Through our member discussions, we learned that nearly all our members agreed that there is a significant learning curve needed to master the tools necessary to program these devices. It was this last discussion point—the learning curve challenge—that the element14 team found interesting, meriting a deeper exploration. The outcome of this exploration was the first Path to Programmable training project. Path II Programmable is a continuation of the challenge that was inspired by the first training program.

What Is the Goal of Path II Programmable?

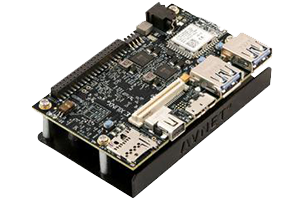

The Path II Programmable training project will train five element14 members by providing them with free FPGA/SoC training modules with lab exercises. Once the training has been completed, the trainees will build a project with the Avnet Ultra96-v2 development board.

In return for both the FREE training and the Ultra96-v2 development board, the five trainees will blog weekly to report on their progress, covering both the high points and the challenges of learning the Ultra96-v2.

Who Can Apply?

Any element14 member can apply to be a Path II Programmable trainee, but there are prerequisites, so please read the How to Apply section prior to submitting an application.

For any general questions about the Path II Programmable project, you can post a comment below.

The training project will cover three phases: (I) enrollment, (II) training with labs, and (III) project building. The important dates are:

| Enrollment Begins: | August 26, 2019 |

| Enrollment Ends: | September 16, 2019 |

| Trainees Selected: | September 27, 2019 |

| Training Begins: | October 11, 2019 |

| Training Ends: | November 11, 2019 |

| Project Building Begins: | November 12, 2019 |

| Project Building Ends: | December 19, 2019 |

One of the ways we can better understand the learning curve challenge of designing with the Ultra96-v2, featuring the Zynq UltraScale + MPSoC, is for our trainees to provide us feedback about their training experience. Hence, the official trainees will be REQUIRED to blog weekly. We want to learn about the high points and challenges of their experience.

Any element14 member can apply to be a Path II Programmable official trainee. But there are prerequisites and specific questions to be answered in the application.

Eligibility

You must be an element14 member to be eligible. Go here to register.

Application Form

All members must submit an application via the Design Challenge group before the end of enrollment on September 16, 2019. (Note: We are using the Design Challenge group because the application infrastructure is in place and easy for our members to use, but this is NOT a Design Challenge.)

Application Instructions

1. Please complete all required information (contact information, etc.)

In the Project Title field, fill in your “Member Name"

Please use the email address that is associated with your element14 profile.

2. Complete the open comments section of the form

Like a Design Challenge application, you will need to tell us why you want to be selected as an official trainee for the Path II Programmable training project. When you plan what you are writing, think about the following things:

- You are competing for free training. The most persuasive applications are the ones that attract the eye of the selection team.

- A single sentence application will never be selected as an official trainee. This project, like training projects, is not a game of chance.

- Be as detailed as possible, but don't write a book.

The five sponsored trainees will receive two training modules, with accompanying training videos, lab exercises, and an Ultra96v2 plus accessories to complete the labs.

Hardware

- The case for a System-on-Chip

- Zynq Processor Overview

- Peripherals

- The Power of Tcl

- Merging the Processing Subsystem (PS) and Programmable Logic (PL)

- Zynq DMa Controller

- Creating Custom IP

- Vivado's Hardware Manager

- Tcl Scripting

- Next Steps

Software

- Zynq MPSoC System Architecture Basics

- Xilinx SDK Overview

- Standalone Board Support Package

- Developing Applications

- Connecting Hardware and Debugging

- First Stage Boot Loader

- SD Card and Boot-up

- SDK Project Management

- Interrupts

- Xilinx Libraries

- Interfacing with Sensors

- Next Steps

Petalinux

- Minimal Ultra96 PetaLinux

- Updating Fully Featured PetaLinux

- Connect with Ultra96 Using Wi-Fi

- Creating PetaLinux Applications using Xilinx SDK

- IoT Application: Log Sensor Data to IBMTM Bluemix

- Embed an Application Using Ultra96 PetaLinux

The official trainees will receive an Avnet Ultra96-v2 Development Board to complete the lab exercises and build their graduation project.

If you are not an official trainee, you can purchase the board below if you simply are interested in following along with the trainees. Unofficial trainees will not be provided with the training modules at this time, however.

Buy NowBuy NowTech Specs

The following is a list of technical resources for the Ultra96-v2:

Design Center

Design Forum

Product Brief

Quick Start Guide

User Manual

The Mentor will assist the ten official trainees in mastering the course material and/or lab exercises, and will provide guidance during the project building phase of the training program.

Sponsor's Mentors

adamtaylorcengfiet

Adam is the Director of ADIUVO Engineering. He is a Chartered Engineer and Fellow of the Institute of Engineering and Technology. He is well known for his Microzed Chronicles. He writes the Exploring the Programmable World for element14. Adam has been instrumental in developing element14's FPGA/Programmable SoC Essentials.

Adam has been a member of the element14 Community since 2018.

As a thank you for participating in the training project, and completing the training and project building phases, we will offer the trainees these graduation awards:

Exploring Zynq MPSoC: With PYNQ and Machine Learning Applications

Product LinkProduct Link- Fluke 233 Remote Display Multimeter

Soldering station

Like most other projects on element14 that require an application, the Path II Programmable project has established rules that the applicants must follow.

Rules ensure fair play and prevent abuse, among other purposes. These rules are described in detail in the project's Terms and Conditions. You can read the Path II Programmable training project's terms by downloading the attached PDF.

Special Note

Path II Programmable is NOT a Design Challenge. It is a professional development project sponsored by Xilinx in conjunction with Avnet and the element14 community. element14 members who submit an application for Path II Programmable are competing to receive FPGA/SoC training on the Ultra96v2 only.

For any general questions about the Path II Programmable project, you can post a comment on this page.

To keep up-to-date with the Path II Programmable project, please bookmark this project.

The deadline for application submissions is Sept 16 2019.

Top Comments

-

Fred27

-

Cancel

-

Vote Up

+2

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Comment-

Fred27

-

Cancel

-

Vote Up

+2

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Children