Table of Contents

Wiring the platform

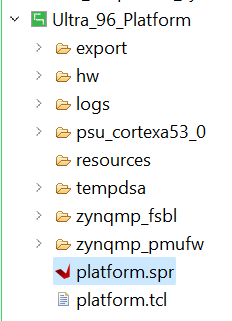

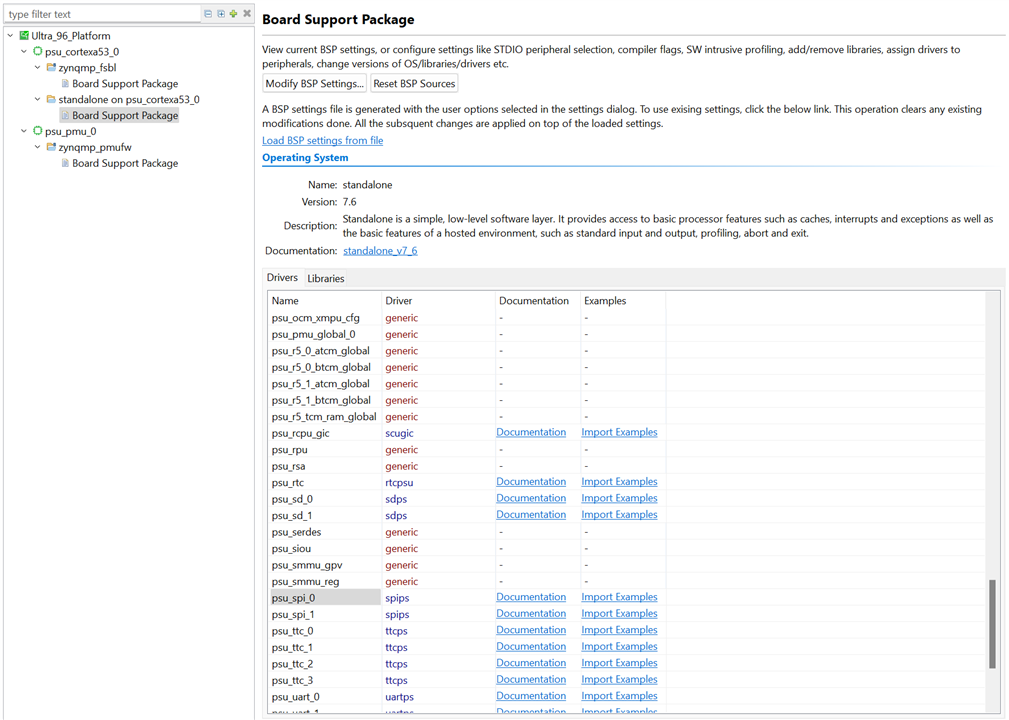

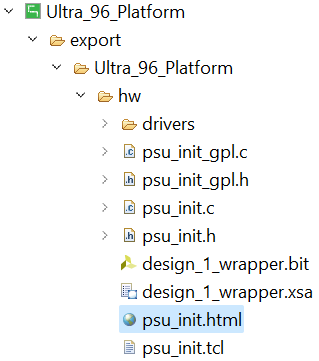

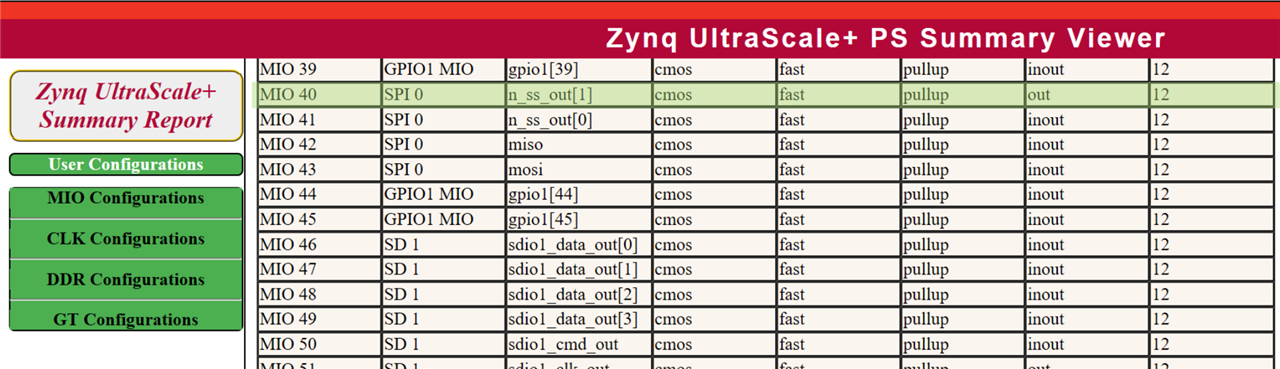

This time, I am using the content of the Software manuals. According to the learning curve, we have a pre-defined architecture in the design_1_wrapper.xsa with a lot of devices and physical connections. To check this information you are able to inspect the Ultra 96 Platform created. I have especial interest on the psu_spi_0 peripheral since the Click Mezzanine has its SPI connections on this peripheral.

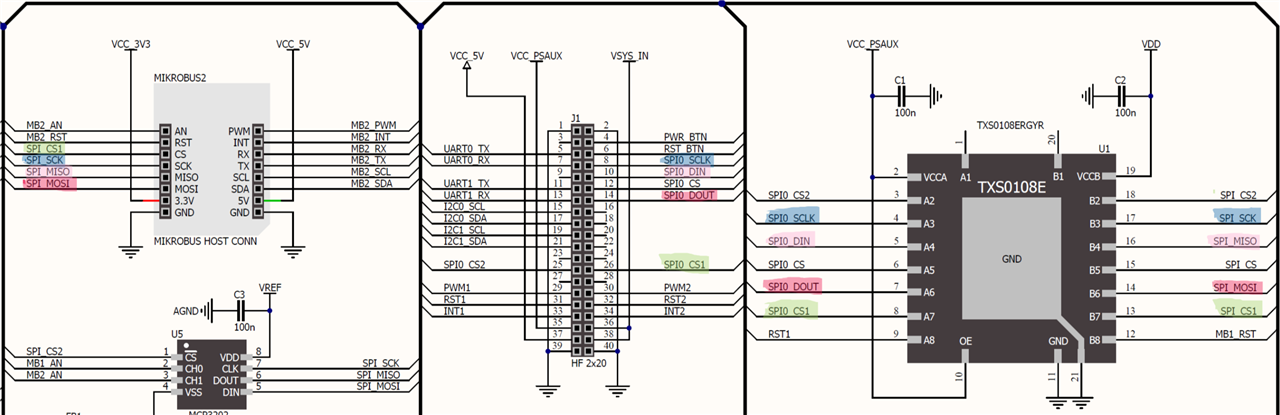

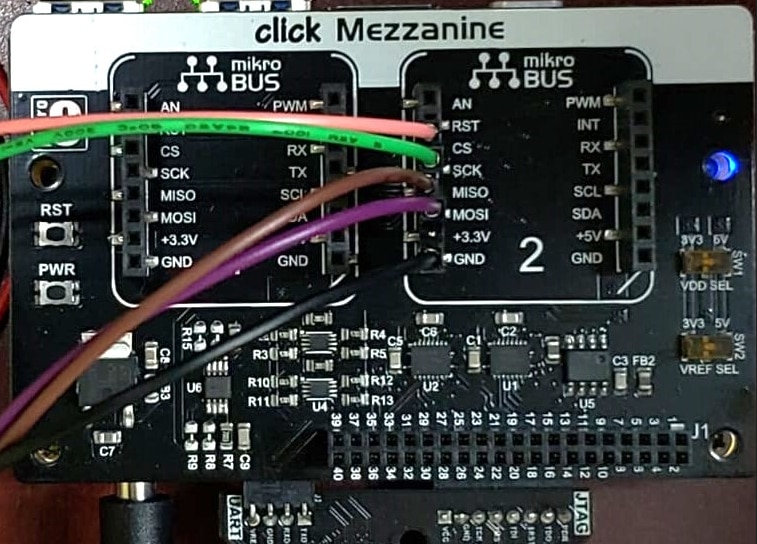

According to the schematic, I am using the MIKROBUS 2 to infer the path in order to debug with a logic analyzer and visualize if the processor send information through the SPI0 device.

Once the path is identified, It is required check the Hardware User Guide to get the physical connections. Using the diagram above and the Table 24, located on page 47 of the Hardware Manual, the user can observe that the Low Speed Expansion Connector (J5) of the ULtra 96 board is the counter part of the Click Mezzanine board, consequently, we can infer the following connections,

- The SPI_SCK wire is located on the C9 terminal at 1V8

- The SPI_CS1 wire is located on the D11 terminal at 1V8

- The SPI_MISO wire is located on the D12 terminal at 1V8

- The SPI_MOSI wire is located on the E13 terminal at 1V8

All this data were extracted from the same manual with Table 2 and Figure 2 located on pages 15 and 12 respectively. It is not necessary worry about the logic levels since the Mezzanine board has implemented bidirectional logic level converters using the TXS0108E IC.

The firmware

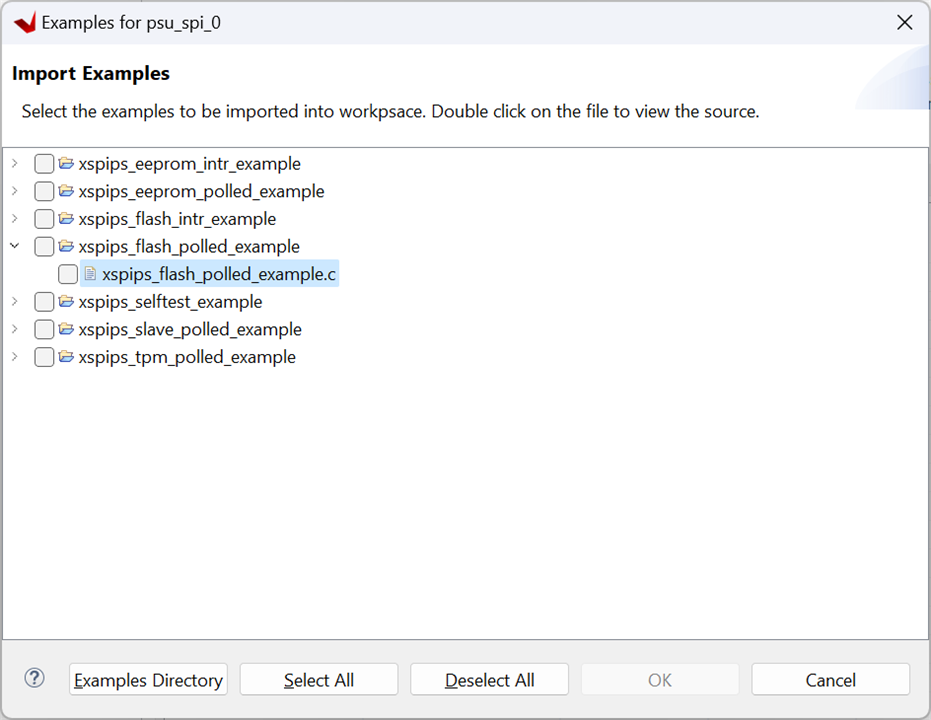

Using the examples provided by the Import Examples link located on the Board Support Package, we are able to construct a software unit like the following to use the SPI0 peripheral to test if the information is send to external devices.

/******************************************************************************

*

* Copyright (C) 2009 - 2014 Xilinx, Inc. All rights reserved.

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in

* all copies or substantial portions of the Software.

*

* Use of the Software is limited solely to applications:

* (a) running on a Xilinx device, or

* (b) that interact with a Xilinx device through a bus or interconnect.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL

* XILINX BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF

* OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

* Except as contained in this notice, the name of the Xilinx shall not be used

* in advertising or otherwise to promote the sale, use or other dealings in

* this Software without prior written authorization from Xilinx.

*

******************************************************************************/

/*

* helloworld.c: simple test application

*

* This application configures UART 16550 to baud rate 9600.

* PS7 UART (Zynq) is not initialized by this application, since

* bootrom/bsp configures it to baud rate 115200

*

* ------------------------------------------------

* | UART TYPE BAUD RATE |

* ------------------------------------------------

* uartns550 9600

* uartlite Configurable only in HW design

* ps7_uart 115200 (configured by bootrom/bsp)

*/

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xspips.h" /* SPI device driver */

#include <sleep.h>

#define SPI_DEVICE_ID XPAR_XSPIPS_0_DEVICE_ID

int SpiPsSelfTestExample(u16 DeviceId);

static XSpiPs Spi;

int main()

{

init_platform();

int Status;

print("Hello World\n\r");

print("SPI Selftest\r\n");

Status = SpiPsSelfTestExample(SPI_DEVICE_ID);

if (Status != XST_SUCCESS) {

xil_printf("SPI Selftest Example Failed\r\n");

return XST_FAILURE;

}

}

int SpiPsSelfTestExample(u16 DeviceId)

{

int Status;

XSpiPs_Config *SpiConfig;

/*

* Initialize the SPI device.

*/

SpiConfig = XSpiPs_LookupConfig(DeviceId);

if (NULL == SpiConfig) {

return XST_FAILURE;

}

Status = XSpiPs_CfgInitialize(&Spi, SpiConfig, SpiConfig->BaseAddress);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

/*

* Perform a self-test to check hardware build.

*/

Status = XSpiPs_SelfTest(&Spi);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

XSpiPs_SetOptions(&Spi, XSPIPS_MANUAL_START_OPTION | \

XSPIPS_MASTER_OPTION | XSPIPS_FORCE_SSELECT_OPTION);

XSpiPs_SetClkPrescaler(&Spi, XSPIPS_CLK_PRESCALE_8);

XSpiPs_SetSlaveSelect(&Spi, 2);

u8 OUT[2] = {0xA5, 0x50};

u8 IN[2] = {0, 0};

while(1){

XSpiPs_PolledTransfer(&Spi, OUT, IN, 2);

xil_printf("Data Sent: %2x %2x\t Data Receive: %2x %2x\r\n", OUT[0], OUT[1], IN[0], IN[1]);

sleep_A53(1);

}

return XST_SUCCESS;

}

Remember that all the APIs respect to the SPI IP are in the #include "xspips.h" and it simplifies the usage of the peripheral since we do not require use direct Bare-Metal programming to program the device. A thing to take account is the posibility of device addresing configuring the SPI peripheral with the XSPIPS_FORCE_SSELECT_OPTION Macro. Since the peripheral can handle one-hot encoder register for slave selection we must know the physical port to device addresing. This information is located on the platform psu_init.html file

psu_init tree location

MIO 40 connection to the SPI0_CS1

The result

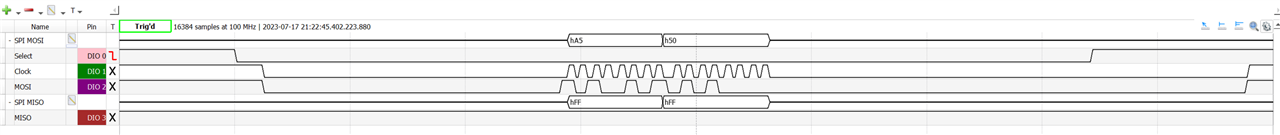

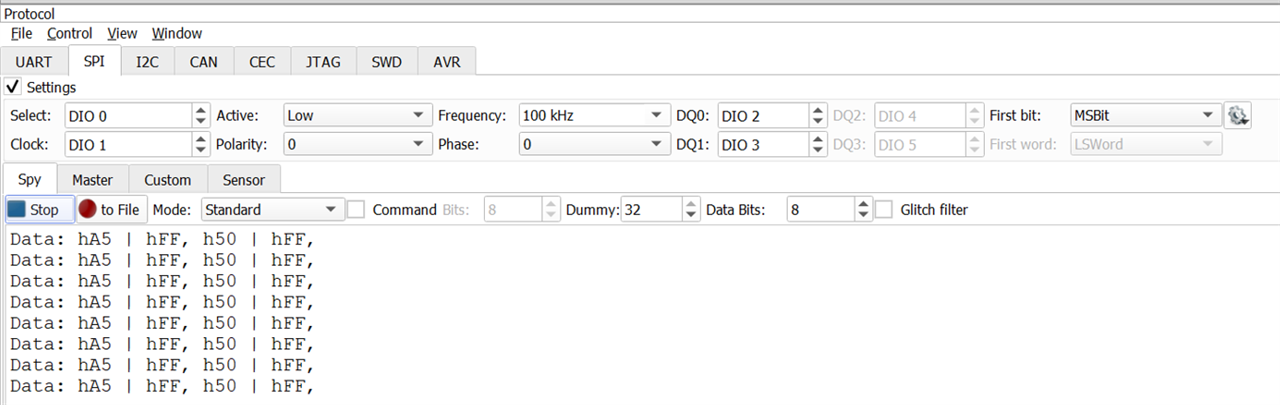

Once the connections were made and the firmware is uploaded to the board feel the magic behind these steps to check if the PS is transmitting information through the SPI 0 periphera

Physical Connections

Logic Analyzer data catch

Protocal data capture