Understanding Minized Hardware Design

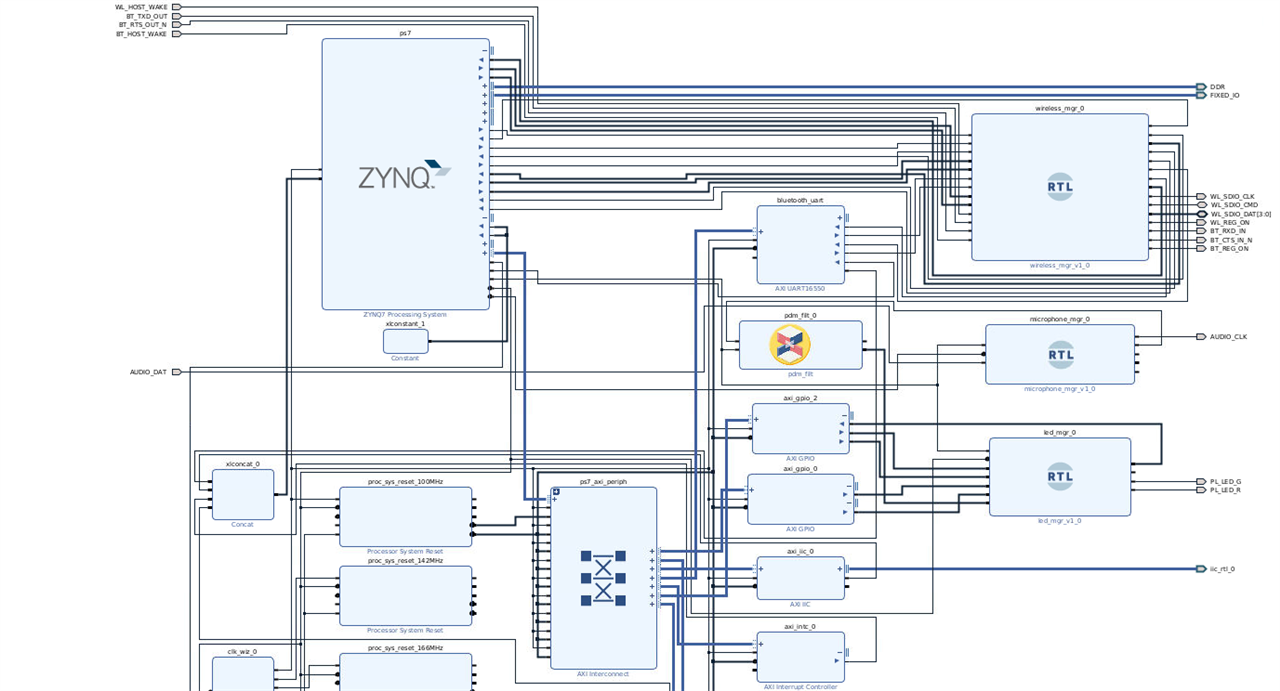

The Minized board was pre-configured with a demonstration project that showcase its capabilities and provide users with a starting point for their own projects. This example design demonstrated a fully working system that had Bluetooth, Wifi, gpios, leds, audio to control an led etc. The design also demonstrated how to use the key features of the board and often leverages the Zynq 7Z007S SoC's FPGA fabric and Arm Cortex-A9 processor. Eventhough the the example design got me going to test the board and its features, I wanted to delve deeper into the Minized example design and the hardware and software tools used to create it. Based on my reading and understanding, I can provide a general overview of how an example design typically works:

1. Project Setup:

The example design is created using FPGA design and embedded software development tools. AMD Vivado is commonly used for FPGA/SoC design, while Vitis and Petalinux are used for embedded software development targeting the Arm Cortex-A9 processor on the Zynq SoC.

2. Hardware Description:

The FPGA design portion of the example typically describes the hardware connections and functionality using a hardware description language like VHDL or Verilog. It sets up various components, peripherals, and interfaces within the FPGA fabric. Nowadays, there are higher level abstraction in terms of blocks and the blocks can be interconnected using tcl scripts. Vivado is then used to synthesis, implement, place and route, generate bitstream and export the xsa file that is given to software developers.

3. FPGA Configuration:

The FPGA configuration file, often referred to as a "bitstream," is generated based on the hardware description. This bitstream is used to program the FPGA fabric with the desired design, effectively defining how the FPGA logic will behave.

4. Processor Software:

The Arm Cortex-A9 processor on the Zynq SoC requires software to run and control various functionalities. The example design includes this software, which is typically written in C/C++ or other compatible programming languages.

5. Firmware Loading:

When the Minized board is powered on or reset, the Zynq SoC's internal boot process takes place. Refer to my previous blog about the Boot modes to understand futher about this topic. The boot process can be configured to load the FPGA bitstream and the processor software into memory.

6. FPGA Initialization:

After configuration, the FPGA fabric is initialized according to the loaded bitstream, configuring the hardware to perform the required functions.

7. Embedded Software Execution:

Once the FPGA is configured, the embedded software running on the Arm Cortex-A9 processor takes control. It can interact with the FPGA fabric through memory-mapped registers and other communication mechanisms.

8. Example Functionality:

The example design may demonstrate various functionalities, such as driving LEDs, reading buttons, communicating over UART, accessing external memory via the micro SD card slot, or performing audio processing etc.

9. User Interaction:

The Minized example design often includes code for user interaction, allowing users to observe the board's behavior through different interfaces, such as led changing colour based on audio intensity (in Minized) or UART communication.

The one thing that certainly interested me was to understand how the micrphone was interfaced to the LED's and the wireless (WiFi and Bluetooth) interfaces.

So I looked further into the design and see if I can find futher information.

I am trying to take a top-down approach into understanding how the design works.

Below are the steps I followed:

1. Find the design files to generate the design:

As I was reading through other blogs, I came across other participants who were on similar path to find the source file.

And came across Avnet github repository that hosts all the code base. I generated the example design for minized.

anushyab@vm_test:/work/avnet-git/hdl/scripts$ vivado -mode batch -source make_minized_sbc_base.tcl -notrace -tclargs minized_sbc base -nolog -nojournal

****** Vivado v2021.2 (64-bit)

**** SW Build 3367213 on Tue Oct 19 02:47:39 MDT 2021

**** IP Build 3369179 on Thu Oct 21 08:25:16 MDT 2021

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

source make_minized_sbc_base.tcl -notrace

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*- -*

*- Welcome to the Avnet Project Builder -*

*- -*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Selected

BDF path /work/avnet-git/bdf

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Creating projects Folder

+------------------+------------------------------------+

| Setting | Configuration |

+------------------+------------------------------------+

| Board | minized_sbc |

+------------------+------------------------------------+

| Project | base |

+------------------+------------------------------------+

| SDK | no |

+------------------+------------------------------------+

| No Close Project | yes |

+------------------+------------------------------------+

| Device | zynq |

+------------------+------------------------------------+

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Vivado version 2021.2 acceptable,

continuing...

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Selected Board and Project as:

minized_sbc and base

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Not Requesting Tag

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Setting Up Project minized_sbc_base...

***** Creating Vivado project...

create_project: Time (s): cpu = 00:00:08 ; elapsed = 00:00:08 . Memory (MB): peak = 2721.602 ; gain = 8.961 ; free physical = 9017 ; free virtual = 14846

***** Setting synthesis language for project to VHDL...

***** Importing constraints file(s)...

***** Assigning Vivado project board_part property to minized...

***** Generating IP...

***** Updating Vivado to include IP folder

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/work/avnet-git/hdl/ip'.

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository '/eda/xilinx/Vivado/2021.2/Vivado/2021.2/data/ip'.

***** Creating block design...

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

INFO: [BD 41-2613] The output directory /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base for minized_sbc_base cannot be found.

***** Adding RTL source Files to design...

***** Adding custom RTL IP blocks to block design...

Making wireless_mgr instance wireless_mgr_0 ...

INFO: [IP_Flow 19-5107] Inferred bus interface 'SDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'WL_SDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from Xilinx Repository).

WARNING: [IP_Flow 19-5661] Bus Interface 'SDIO_CLK' does not have any bus interfaces associated with it.

WARNING: [IP_Flow 19-5661] Bus Interface 'WL_SDIO_CLK' does not have any bus interfaces associated with it.

CRITICAL WARNING: [IP_Flow 19-4751] Bus Interface 'WL_SDIO_CLK': FREQ_HZ bus parameter is missing for output clock interface.

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/work/avnet-git/hdl/ip'.

Making led_mgr instance led_mgr_0 ...

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/work/avnet-git/hdl/ip'.

Making microphone_mgr instance microphone_mgr_0 ...

INFO: [IP_Flow 19-5107] Inferred bus interface 'clk_in' of definition 'xilinx.com:signal:clock:1.0' (from X_INTERFACE_INFO parameter from HDL file).

INFO: [IP_Flow 19-5107] Inferred bus interface 'clk_in' of definition 'xilinx.com:signal:clock:1.0' (from 'X_INTERFACE_INFO' attribute).

INFO: [IP_Flow 19-5107] Inferred bus interface 'resetn_in' of definition 'xilinx.com:signal:reset:1.0' (from X_INTERFACE_INFO parameter from HDL file).

INFO: [IP_Flow 19-5107] Inferred bus interface 'resetn_in' of definition 'xilinx.com:signal:reset:1.0' (from 'X_INTERFACE_INFO' attribute).

INFO: [IP_Flow 19-5107] Inferred bus interface 'AUDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from X_INTERFACE_INFO parameter from HDL file).

INFO: [IP_Flow 19-5107] Inferred bus interface 'AUDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from 'X_INTERFACE_INFO' attribute).

INFO: [IP_Flow 19-4728] Bus Interface 'clk_in': Added interface parameter 'ASSOCIATED_RESET' with value 'resetn_in'.

INFO: [IP_Flow 19-4728] Bus Interface 'clk_in': Added interface parameter 'FREQ_HZ' with value '160000000'.

INFO: [IP_Flow 19-4728] Bus Interface 'AUDIO_CLK': Added interface parameter 'FREQ_HZ' with value '2500000'.

INFO: [IP_Flow 19-7067] Note that bus interface 'clk_in' has a fixed FREQ_HZ of '160000000'. This value will be respected whenever this IP is instantiated in IP Integrator.

WARNING: [IP_Flow 19-5661] Bus Interface 'clk_in' does not have any bus interfaces associated with it.

INFO: [IP_Flow 19-7067] Note that bus interface 'AUDIO_CLK' has a fixed FREQ_HZ of '2500000'. This value will be respected whenever this IP is instantiated in IP Integrator.

WARNING: [IP_Flow 19-5661] Bus Interface 'AUDIO_CLK' does not have any bus interfaces associated with it.

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/work/avnet-git/hdl/ip'.

***** Adding processing system presets from board definition...

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

***** Adding defined IP blocks to block design...

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Device 21-403] Loading part xc7z007sclg225-1

create_bd_cell: Time (s): cpu = 00:00:04 ; elapsed = 00:00:06 . Memory (MB): peak = 2798.391 ; gain = 0.000 ; free physical = 8550 ; free virtual = 14422

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

WARNING: [IP_Flow 19-3374] An attempt to modify the value of disabled parameter 'MMCM_CLKFBOUT_MULT_F' from '10.000' to '20.000' has been ignored for IP 'clk_wiz_0'

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/xin> is being overridden by the user with net <ps7_FCLK_CLK1>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_0/gpio_io_o> is being overridden by the user with net <axi_gpio_0_gpio_io_o>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_0/gpio2_io_o> is being overridden by the user with net <axi_gpio_0_gpio2_io_o>. This pin will not be connected as a part of interface connection <GPIO2>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_2/gpio_io_t> is being overridden by the user with net <axi_gpio_2_gpio_io_t>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_2/gpio_io_o> is being overridden by the user with net <axi_gpio_2_gpio_io_o>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_2/gpio_io_i> is being overridden by the user with net <led_mgr_0_GPIO_to_Zynq>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO1_CDN> is being overridden by the user with net <xlconstant_1_dout>. This pin will not be connected as a part of interface connection <SDIO_1>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO1_WP> is being overridden by the user with net <xlconstant_1_dout>. This pin will not be connected as a part of interface connection <SDIO_1>.

WARNING: [BD 41-1306] The connection to interface pin </axi_intc_0/irq> is being overridden by the user with net <axi_intc_0_irq>. This pin will not be connected as a part of interface connection <interrupt>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CLK> is being overridden by the user with net <ps7_SDIO0_CLK>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CLK_FB> is being overridden by the user with net <wireless_mgr_0_SDIO_CLK_FB>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CMD_O> is being overridden by the user with net <ps7_SDIO0_CMD_O>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CMD_I> is being overridden by the user with net <wireless_mgr_0_SDIO_CMD_to_Zynq>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CMD_T> is being overridden by the user with net <ps7_SDIO0_CMD_T>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_DATA_O> is being overridden by the user with net <ps7_SDIO0_DATA_O>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_DATA_I> is being overridden by the user with net <wireless_mgr_0_SDIO_DATA_to_Zynq>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_DATA_T> is being overridden by the user with net <ps7_SDIO0_DATA_T>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_WP> is being overridden by the user with net <wireless_mgr_0_SDIO_WP>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CDN> is being overridden by the user with net <wireless_mgr_0_SDIO_CDN>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/GPIO_O> is being overridden by the user with net <ps7_GPIO_O>. This pin will not be connected as a part of interface connection <GPIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/GPIO_I> is being overridden by the user with net <wireless_mgr_0_GPIO_to_Zynq>. This pin will not be connected as a part of interface connection <GPIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/GPIO_T> is being overridden by the user with net <ps7_GPIO_T>. This pin will not be connected as a part of interface connection <GPIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/sout> is being overridden by the user with net <bluetooth_uart_sout>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/sin> is being overridden by the user with net <wireless_mgr_0_ZYNQ_UART_RX>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/rtsn> is being overridden by the user with net <bluetooth_uart_rtsn>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/ctsn> is being overridden by the user with net <wireless_mgr_0_ZYNQ_UART_CTS>. This pin will not be connected as a part of interface connection <UART>.

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

***** Assigning peripheral addresses...

Slave segment '/axi_gpio_0/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4120_0000 [ 64K ]>.

Slave segment '/axi_gpio_1/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4121_0000 [ 64K ]>.

Slave segment '/axi_gpio_2/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4122_0000 [ 64K ]>.

Slave segment '/axi_iic_0/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4160_0000 [ 64K ]>.

Slave segment '/axi_intc_0/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4180_0000 [ 64K ]>.

Slave segment '/bluetooth_uart/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x43C0_0000 [ 64K ]>.

Slave segment '/xadc_wiz_0/s_axi_lite/Reg' is being assigned into address space '/ps7/Data' at <0x43C1_0000 [ 64K ]>.

***** Validating the block design...

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-1348] Reset pin /microphone_mgr_0/resetn_in (associated clock /microphone_mgr_0/clk_in) is connected to asynchronous reset source /ps7/FCLK_RESET2_N.

This may prevent design from meeting timing. Please add Processor System Reset module to create a reset that is synchronous to the associated clock source /ps7/FCLK_CLK2.

WARNING: [xilinx.com:ip:axi_intc:4.1-13] /axi_intc_0: Interrupt output connection Bus is selected, but the interrupt bus interface is not connected to a matching interface. Please consider selecting Single instead.

INFO: [xilinx.com:ip:clk_wiz:6.0-1] /clk_wiz_0 clk_wiz propagate

CRITICAL WARNING: [BD 41-759] The input pins (listed below) are either not connected or do not have a source port, and they don't have a tie-off specified. These pins are tied-off to all 0's to avoid error in Implementation flow.

Please check your design and connect them as needed:

/axi_intc_0/intr

***** Validating IP licenses...

License Validation = Successful

***** Creating top level HDL wrapper for design and adding to project...

INFO: [BD 41-1662] The design 'minized_sbc_base.bd' is already validated. Therefore parameter propagation will not be re-run.

CRITICAL WARNING: [BD 41-759] The input pins (listed below) are either not connected or do not have a source port, and they don't have a tie-off specified. These pins are tied-off to all 0's to avoid error in Implementation flow.

Please check your design and connect them as needed:

/axi_intc_0/intr

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/synth/minized_sbc_base.vhd

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/sim/minized_sbc_base.vhd

VHDL Output written to : /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd

INFO: [Project 1-1716] Could not find the wrapper file /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd, checking in project .gen location instead.

INFO: [Vivado 12-12390] Found file /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd, adding it to Project

***** Adding Vitis directves to design...

update_compile_order: Time (s): cpu = 00:00:09 ; elapsed = 00:00:06 . Memory (MB): peak = 2894.434 ; gain = 96.043 ; free physical = 8469 ; free virtual = 14367

INFO: [filemgmt 20-334] All file(s) are already imported in fileset: 'constrs_1'

INFO: [filemgmt 20-348] Importing the appropriate files for fileset: 'constrs_1'

INFO: [filemgmt 20-348] Importing the appropriate files for fileset: 'sources_1'

***** Building binary...

update_compile_order: Time (s): cpu = 00:00:09 ; elapsed = 00:00:06 . Memory (MB): peak = 2934.449 ; gain = 0.000 ; free physical = 8469 ; free virtual = 14367

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-1348] Reset pin /microphone_mgr_0/resetn_in (associated clock /microphone_mgr_0/clk_in) is connected to asynchronous reset source /ps7/FCLK_RESET2_N.

This may prevent design from meeting timing. Please add Processor System Reset module to create a reset that is synchronous to the associated clock source /ps7/FCLK_CLK2.

WARNING: [xilinx.com:ip:axi_intc:4.1-13] /axi_intc_0: Interrupt output connection Bus is selected, but the interrupt bus interface is not connected to a matching interface. Please consider selecting Single instead.

INFO: [xilinx.com:ip:clk_wiz:6.0-1] /clk_wiz_0 clk_wiz propagate

INFO: [xilinx.com:ip:clk_wiz:6.0-1] /clk_wiz_0 clk_wiz propagate

CRITICAL WARNING: [BD 41-759] The input pins (listed below) are either not connected or do not have a source port, and they don't have a tie-off specified. These pins are tied-off to all 0's to avoid error in Implementation flow.

Please check your design and connect them as needed:

/axi_intc_0/intr

Wrote : </work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/synth/minized_sbc_base.vhd

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/sim/minized_sbc_base.vhd

VHDL Output written to : /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd

INFO: [BD 41-1029] Generation completed for the IP Integrator block wireless_mgr_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block led_mgr_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block microphone_mgr_0 .

INFO: [IP_Flow 19-5611] Unable to find an associated reset port for the interface 'M_AXI_GP0'. A default connection has been created.

INFO: [BD 41-1029] Generation completed for the IP Integrator block ps7 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block ps7_axi_periph/xbar .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_gpio_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_gpio_1 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_gpio_2 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_iic_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block bluetooth_uart .

INFO: [BD 41-1029] Generation completed for the IP Integrator block xlconcat_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block xlconstant_1 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_intc_0 .

false

INFO: [IP_Flow 19-3422] Upgraded pdm_filt_fir_compiler_v7_2_i0 (FIR Compiler 7.2) from revision 8 to revision 17

false

INFO: [IP_Flow 19-3422] Upgraded pdm_filt_fir_compiler_v7_2_i1 (FIR Compiler 7.2) from revision 8 to revision 17

INFO: [BD 41-1029] Generation completed for the IP Integrator block pdm_filt_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block xadc_wiz_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_100MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_142MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_166MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_200MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_41MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_50MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block clk_wiz_0 .

WARNING: [IP_Flow 19-4994] Overwriting existing constraint file '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_auto_pc_0/minized_sbc_base_auto_pc_0_ooc.xdc'

INFO: [BD 41-1029] Generation completed for the IP Integrator block ps7_axi_periph/s00_couplers/auto_pc .

Exporting to file /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hw_handoff/minized_sbc_base.hwh

Generated Hardware Definition File /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/synth/minized_sbc_base.hwdef

[Wed Jul 26 14:23:52 2023] Launched minized_sbc_base_xbar_0_synth_1, minized_sbc_base_ps7_0_synth_1, minized_sbc_base_microphone_mgr_0_0_synth_1, minized_sbc_base_led_mgr_0_0_synth_1, minized_sbc_base_wireless_mgr_0_0_synth_1, minized_sbc_base_xadc_wiz_0_0_synth_1, minized_sbc_base_pdm_filt_0_0_synth_1, minized_sbc_base_axi_intc_0_0_synth_1, minized_sbc_base_axi_gpio_0_0_synth_1, minized_sbc_base_axi_gpio_1_0_synth_1, minized_sbc_base_axi_gpio_2_0_synth_1, minized_sbc_base_axi_iic_0_0_synth_1, minized_sbc_base_axi_uart16550_0_0_synth_1, minized_sbc_base_auto_pc_0_synth_1, minized_sbc_base_proc_sys_reset_100MHz_0_synth_1, minized_sbc_base_proc_sys_reset_142MHz_0_synth_1, minized_sbc_base_proc_sys_reset_166MHz_0_synth_1, minized_sbc_base_proc_sys_reset_200MHz_0_synth_1, minized_sbc_base_proc_sys_reset_41MHz_0_synth_1, minized_sbc_base_proc_sys_reset_50MHz_0_synth_1, minized_sbc_base_clk_wiz_0_0_synth_1, synth_1...

Run output will be captured here:

minized_sbc_base_xbar_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_xbar_0_synth_1/runme.log

minized_sbc_base_ps7_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_ps7_0_synth_1/runme.log

minized_sbc_base_microphone_mgr_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_microphone_mgr_0_0_synth_1/runme.log

minized_sbc_base_led_mgr_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_led_mgr_0_0_synth_1/runme.log

minized_sbc_base_wireless_mgr_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_wireless_mgr_0_0_synth_1/runme.log

minized_sbc_base_xadc_wiz_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_xadc_wiz_0_0_synth_1/runme.log

minized_sbc_base_pdm_filt_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_pdm_filt_0_0_synth_1/runme.log

minized_sbc_base_axi_intc_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_axi_intc_0_0_synth_1/runme.log

minized_sbc_base_axi_gpio_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_axi_gpio_0_0_synth_1/runme.log

minized_sbc_base_axi_gpio_1_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_axi_gpio_1_0_synth_1/runme.log

minized_sbc_base_axi_gpio_2_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_axi_gpio_2_0_synth_1/runme.log

minized_sbc_base_axi_iic_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_axi_iic_0_0_synth_1/runme.log

minized_sbc_base_axi_uart16550_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_axi_uart16550_0_0_synth_1/runme.log

minized_sbc_base_auto_pc_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_auto_pc_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_100MHz_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_100MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_142MHz_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_142MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_166MHz_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_166MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_200MHz_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_200MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_41MHz_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_41MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_50MHz_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_50MHz_0_synth_1/runme.log

minized_sbc_base_clk_wiz_0_0_synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/minized_sbc_base_clk_wiz_0_0_synth_1/runme.log

synth_1: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/synth_1/runme.log

[Wed Jul 26 14:23:52 2023] Launched impl_1...

Run output will be captured here: /work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.runs/impl_1/runme.log

launch_runs: Time (s): cpu = 00:01:13 ; elapsed = 00:01:05 . Memory (MB): peak = 3046.512 ; gain = 112.062 ; free physical = 8291 ; free virtual = 14279

***** Wait for bitstream to be written...

[Wed Jul 26 14:23:52 2023] Waiting for impl_1 to finish...

*** Running vivado

with args -log minized_sbc_base_wrapper.vdi -applog -m64 -product Vivado -messageDb vivado.pb -mode batch -source minized_sbc_base_wrapper.tcl -notrace

****** Vivado v2021.2 (64-bit)

**** SW Build 3367213 on Tue Oct 19 02:47:39 MDT 2021

**** IP Build 3369179 on Thu Oct 21 08:25:16 MDT 2021

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

source minized_sbc_base_wrapper.tcl -notrace

create_project: Time (s): cpu = 00:00:06 ; elapsed = 00:00:05 . Memory (MB): peak = 2721.574 ; gain = 7.961 ; free physical = 11853 ; free virtual = 14618

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/work/avnet-git/hdl/ip'.

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository '/eda/xilinx/Vivado/2021.2/Vivado/2021.2/data/ip'.

add_files: Time (s): cpu = 00:00:08 ; elapsed = 00:00:06 . Memory (MB): peak = 2905.656 ; gain = 184.082 ; free physical = 11781 ; free virtual = 14546

Command: link_design -top minized_sbc_base_wrapper -part xc7z007sclg225-1

Design is defaulting to srcset: sources_1

Design is defaulting to constrset: constrs_1

INFO: [Device 21-403] Loading part xc7z007sclg225-1

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0.dcp' for cell 'minized_sbc_base_i/axi_gpio_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0.dcp' for cell 'minized_sbc_base_i/axi_gpio_1'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0.dcp' for cell 'minized_sbc_base_i/axi_gpio_2'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_iic_0_0/minized_sbc_base_axi_iic_0_0.dcp' for cell 'minized_sbc_base_i/axi_iic_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_intc_0_0/minized_sbc_base_axi_intc_0_0.dcp' for cell 'minized_sbc_base_i/axi_intc_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0.dcp' for cell 'minized_sbc_base_i/bluetooth_uart'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.dcp' for cell 'minized_sbc_base_i/clk_wiz_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_led_mgr_0_0/minized_sbc_base_led_mgr_0_0.dcp' for cell 'minized_sbc_base_i/led_mgr_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_microphone_mgr_0_0/minized_sbc_base_microphone_mgr_0_0.dcp' for cell 'minized_sbc_base_i/microphone_mgr_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/minized_sbc_base_pdm_filt_0_0.dcp' for cell 'minized_sbc_base_i/pdm_filt_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_100MHz'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_142MHz'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_166MHz'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_200MHz'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_41MHz'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_50MHz'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.dcp' for cell 'minized_sbc_base_i/ps7'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_wireless_mgr_0_0/minized_sbc_base_wireless_mgr_0_0.dcp' for cell 'minized_sbc_base_i/wireless_mgr_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xadc_wiz_0_0/minized_sbc_base_xadc_wiz_0_0.dcp' for cell 'minized_sbc_base_i/xadc_wiz_0'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xbar_0/minized_sbc_base_xbar_0.dcp' for cell 'minized_sbc_base_i/ps7_axi_periph/xbar'

INFO: [Project 1-454] Reading design checkpoint '/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_auto_pc_0/minized_sbc_base_auto_pc_0.dcp' for cell 'minized_sbc_base_i/ps7_axi_periph/s00_couplers/auto_pc'

Netlist sorting complete. Time (s): cpu = 00:00:00.09 ; elapsed = 00:00:00.09 . Memory (MB): peak = 2905.656 ; gain = 0.000 ; free physical = 11463 ; free virtual = 14229

INFO: [Netlist 29-17] Analyzing 90 Unisim elements for replacement

INFO: [Netlist 29-28] Unisim Transformation completed in 0 CPU seconds

INFO: [Project 1-479] Netlist was created with Vivado 2021.2

INFO: [Project 1-570] Preparing netlist for logic optimization

WARNING: [Opt 31-32] Removing redundant IBUF since it is not being driven by a top-level port. minized_sbc_base_i/clk_wiz_0/inst/clkin1_ibufg

Resolution: The tool has removed redundant IBUF. To resolve this warning, check for redundant IBUF in the input design.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/clk_wiz_0/clk_in1' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_dir' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_dir' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_dir' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_from_Zynq' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_from_Zynq' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_from_Zynq' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_to_Zynq' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_to_Zynq' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_to_Zynq' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[0]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[0]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[0]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[1]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[1]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[1]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[2]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[2]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[2]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[3]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[3]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[3]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xadc_wiz_0_0/minized_sbc_base_xadc_wiz_0_0.xdc] for cell 'minized_sbc_base_i/xadc_wiz_0/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xadc_wiz_0_0/minized_sbc_base_xadc_wiz_0_0.xdc] for cell 'minized_sbc_base_i/xadc_wiz_0/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

INFO: [Timing 38-35] Done setting XDC timing constraints. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc:57]

INFO: [Timing 38-2] Deriving generated clocks [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc:57]

get_clocks: Time (s): cpu = 00:00:09 ; elapsed = 00:00:09 . Memory (MB): peak = 2908.441 ; gain = 2.785 ; free physical = 10954 ; free virtual = 13740

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0_board.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0_board.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc] for cell 'minized_sbc_base_i/ps7/inst'

WARNING: [Vivado 12-2489] -input_jitter contains time 0.618750 which will be rounded to 0.619 to ensure it is an integer multiple of 1 picosecond [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc:24]

WARNING: [Vivado 12-2489] -input_jitter contains time 0.187500 which will be rounded to 0.188 to ensure it is an integer multiple of 1 picosecond [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc:27]

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc] for cell 'minized_sbc_base_i/ps7/inst'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/constrs/pdm_filt.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/constrs/pdm_filt.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i0/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2/pdm_filt_fir_compiler_v7_2_i0_instance/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i0/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2/pdm_filt_fir_compiler_v7_2_i0_instance/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i1/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2_1/pdm_filt_fir_compiler_v7_2_i1_instance/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i1/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2_1/pdm_filt_fir_compiler_v7_2_i1_instance/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_intc_0_0/minized_sbc_base_axi_intc_0_0.xdc] for cell 'minized_sbc_base_i/axi_intc_0/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_intc_0_0/minized_sbc_base_axi_intc_0_0.xdc] for cell 'minized_sbc_base_i/axi_intc_0/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0_board.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0_board.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_iic_0_0/minized_sbc_base_axi_iic_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_iic_0/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_iic_0_0/minized_sbc_base_axi_iic_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_iic_0/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Finished Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Parsing XDC File [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc]

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT0'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:70]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:70]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT0'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:71]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:71]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT1'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:74]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:74]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT1'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:75]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:75]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT2'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:78]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:78]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT2'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:79]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:79]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT3'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:82]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:82]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT3'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:83]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:83]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT4'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:86]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:86]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT4'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:87]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:87]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT5'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:90]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:90]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT5'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:91]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:91]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT6'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:94]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:94]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT6'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:95]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:95]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT7'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:98]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:98]

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

WARNING: [Vivado 12-584] No ports matched 'ARD_DAT7'. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:99]

CRITICAL WARNING: [Common 17-55] 'set_property' expects at least one object. [/work/avnet-git/hdl/projects/minized_sbc_base_2021_2/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc:99]