I have developed the following design as the framework for the bus interface of USB2 interfaced FPGA based instruments.

This firmware in intended to aid the design of instrumentation using the Morph-IC-II module and other fpga systems interfaced to the USB2 bus using FTDI's FT2232H interface chip.

It has been in use in prototype form in my NMR laboratory as the heart of a number of instruments (contributing to a number of papers), and would I believe aid the design of other FPGA based instrumenatation.

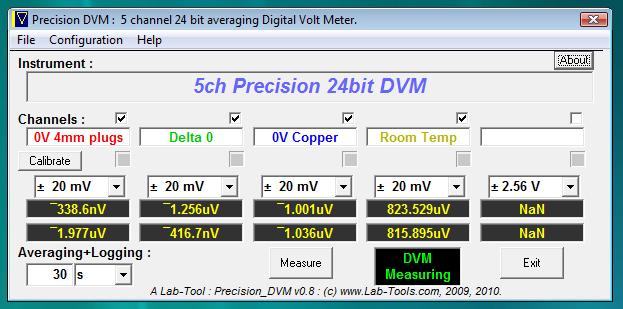

Here is one of these FPGA based instruments (in use, but still in prototype) : 5 Channel Precision 24bit DVM intended for thermocouple use.

The interface is designed to facilitate the creation of such instruments, and in particular features USB bus interface registers, for instrument configuration, control, status and medium-rate data transfer.

But it also now supports full USB2 byte-wide data pipes into the instrument modules.

I am currently implementing this design using the FTDIchip (http://www.ftdichip.com/) MORPH-IC-II FPGA module, which uses the FTDI FT2223H USB2 interface chip, but other FPGA systems can benefit, possibly using the FTDI FT2232H mini modules at the prototype stage.

For my NMR instrumentation and GUI front panels I use a version of the APL Array Programming Language : APLX (http://www.microapl.co.uk/), which can talk to the FTDI .dlls that interface to the FT2232H, but any other language that can talk to the .dlls can be used.

The FTDI 2232H connects to the USB bus and for the data transfer interfaces to an fpga via the A-side octal register and 4 handshake lines (up to you if you use the B-side for programming, as in the MorphicII, but it does also go like the wind).

The first block "USB to Addressed Bus Interface" handles the protocol below, and transfers the USB info to three byte-wide busses : "Bank", "Address", "Data".

There can be multiple "Banks" of instruments.

Each "Instrument" within the fpga has a block of up to 256 byte-wide interface registers (that can of course be used in groups to build wide-word registers - I have used up to 128bit words), plus the streaming byte-wide data-pipe fed at full USB2 rate. These interface registers are used for instrument configuration, control, status and low-rate data transfer.

So that one can read or write single or multi-byte words to a particular instrument register/register group, one has to also give an 8-bit "Bank" address as well as the register address - if one omits "Bank" the software defaults to the 1st bank.

I use Apl for talking to the firmware - it is interactive which means rapid development but the functions run fast as you can see in the YouTube videos. It talks directly to the .dll for the FTDI D2XX direct drivers, so one has full control over the USB data transfers and configuration. But you can use this firmware with any software that can talk to the .dlls ....

The "word" read/write commands are :

BnkAddrNb ezww Data (Data as Nb byte range integers)

Res ← HndlBnk ezrw AddressRange (or list) (interprets Res as N byte word)

For full USB2 rate transfer of vectors of data :

BnkAddr morphic_vector_write DataVector (Where Addr is normally the block start address)

DataVector ← BnkAddr morphic_vector_read N (reads N byte vector)

For this vector data transfer I use synchronous FIFO mode in the FT223H for the data channel:

3.4.2 FT2232H pins used in an FT245 Style Synchronous FIFO Interface : ADBUS[7:0] I/O D7 to D0 bidirectional FIFO data.

I attach a cropped SignalTapII recording, being clocked at 120MHz.

clk_ftdi is a 60 MHz Clock driven from the FTDI chip.

The data being sent is counting up, the remaining byte-count counting down with each byte.

For medium bursts SignalTapII shows the data being clocked in or out at every clock, then there is a short, slightly variable gap between the bursts.

As a test and example of functionality and data transfer speed, I created the following video :

Lab-Tools Morphic-II Fast Data Transfer to Altera Cyclone II.

Demonstrating fast block transfer of vectors of data to and from Lab-Tools modular instrumentation over the USB2 interface, using the Morphic II module containing an Altera Cyclone II Field Programmable Gate Array (FPGA).

With up-transfers of 1k word x 16 bit data (being scaled and then converted from 64bit floating-point data in the Apl interpreter), followed by a USB command to read the same block back, convert it to 64-bit floating point, error checked, displayed on a graph, and all timed, a 1.6GHz Windows 7 64bit lap-top (running a 32bit Apl interpreter) can do this continually every 50ms, with transfer delay jitter just starting to go up. Down at 20 ms the system is just not keeping up. The YouTube video was captured at 10 Hz frame rate, so I used 100ms repeat time for this.

The data-pipe is read/write and normally (as in this case) would go to a memory, but in my second YouTube example it feeds a peripheral with a specific block of firmware that is able to eat the bytes at full USB2 rate :

2012-04-07 - Lab-Tools FPGA Binning Co-processor for Apl

This video describes an example USB2 interfaced FPGA co-processor for use with the array processing language Apl.

This co-processor implements a single scientific algorithm : Binning.

As such it is an example of what can be achieved using field-programmable gate array co-processors with Apl.

The FPGA module used is the Morphic II, available from FTDI. This module has the advantage that it does not require a USB Blaster to program it.

Software, firmware and modules are also available from Lab-Tools Ltd, who are also developing a series of credit-card sized interface and data I/O modules to interface with them.

The FPGA co-processor is accessed and controlled from AplX, a version of the array processing language Apl, from Micro-Apl.

I hope to be ready to make this firmware available for download shortly, as soon as the pricing and licensing details are finalised.

For further details see : http://www.lab-tools.com/instrumentation .

Instrumentation modules including an analogue transient capture/average/process module, based on this firmware, are currently also being finalised.

This firmware in intended to aid the design of instrumentation using the Morph-IC-II module and other fpga systems interfaced to the USB2 bus using FTDI's FT2232H interface chip.