I found a second SPI on J1 header.

So, I have now implemented the "DualSPIder".

What is DualSPIder?

It is used to compensate "Round Trip Delays":

A SPI Master will send (SCLK, MOSI, CS) but the MISO signal from far end (DUT, "Device Under Test") is delayed (e.g. due to ribbon cable or additional line drivers, or using LVDS...).

So, the SCLK is "mirrored back" at the far end (affected by the same delay due to cable length and drivers) and SCLK', MISO are going into a SPI Slave (still as "synchronous").

So, it compensates the "round trip delay", or the additional delays due to line driver, LVDS interfaces...

Figure 1: DualSPIder approach

One SPI Master and one SPI Slave: the slave receives the "mirrored" SCLK signal so that MISO and SCL are still in sync on MCU receiver (SPI is synchronous!),

never mind how long the cable is; if additional drivers are there or if we use LVDS logic (and converters on both end) - the delay is compensated by this approach.

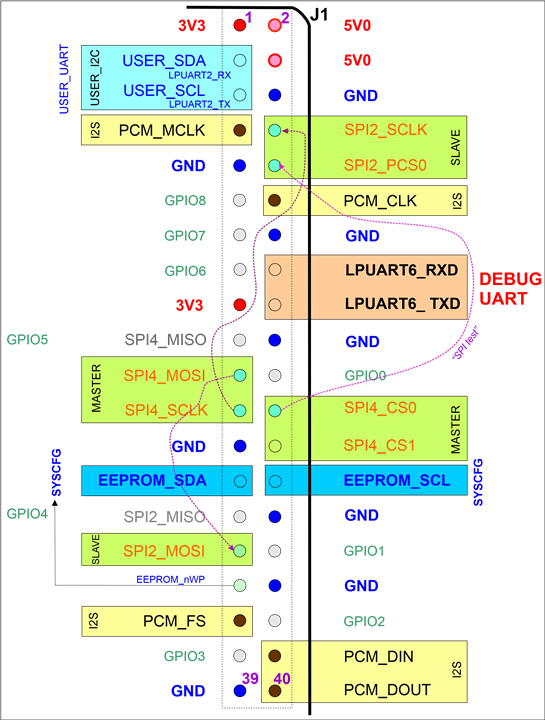

Changed J1 pin usage

In order to gain the second SPI (LPSPI2) I had to free the Debug UART as LPUART1.

Debug UART is now LPUART6 (see the other pins on J1 and connect to it with your MCU-LINK!).

Testing SPI

if you want to test the SPI via Loopback - to see on Rx what was sent on Tx - you had to use now three wires:

J1, pin 21 - to J1, pin 31

J1, pin 23 - to J1, pin 8

J1, pin 24 - to J1, pin 10

All what you send should also be received (and reported on USB VCP UART).

Figure 2: "my" J1 pin usage for DualSPIder and for future use

SPI Performance

I have tested how fast I can go (with this SPI Master plus SPI Slave approach).

ATT: the clock config is modified, in order to increase the speed on SPI: default was just 12 Mbps/MHz.

I can reach:

55.6 MHz for this Master + Slave combination is the maximum I could achieve.

(anyway: way better as the Teensy 4.1 board!)

I use a bit slower: 45.4 MHz, which results in a minimum speed of 4 KHz.

The project is here:

tjaekel/MaaXBoard-RT_SPIder: MaaXBoard-RT SPIder framework (github.com)