Hi!

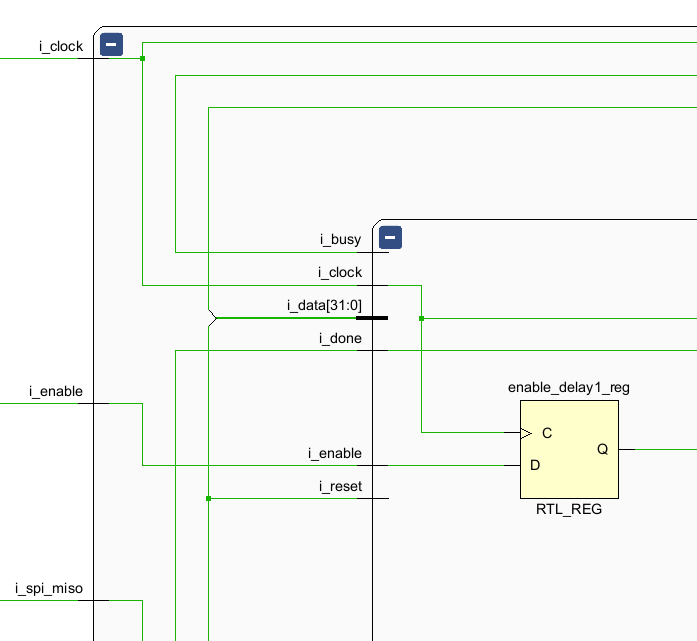

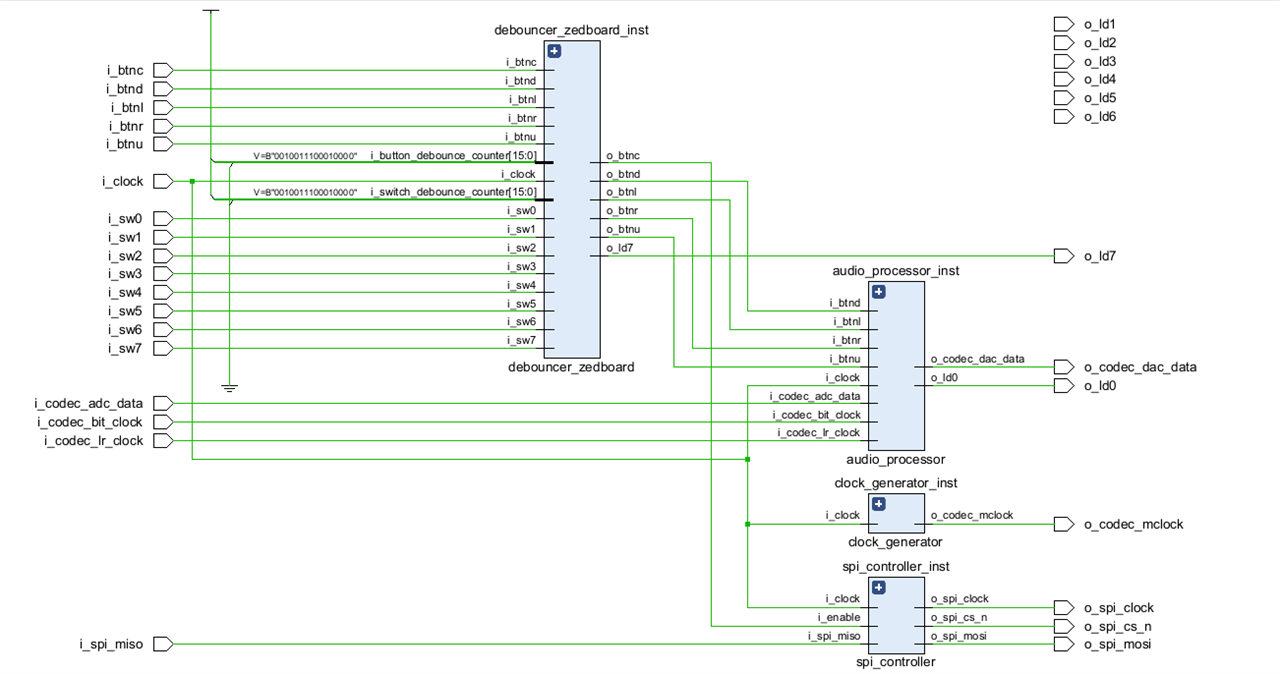

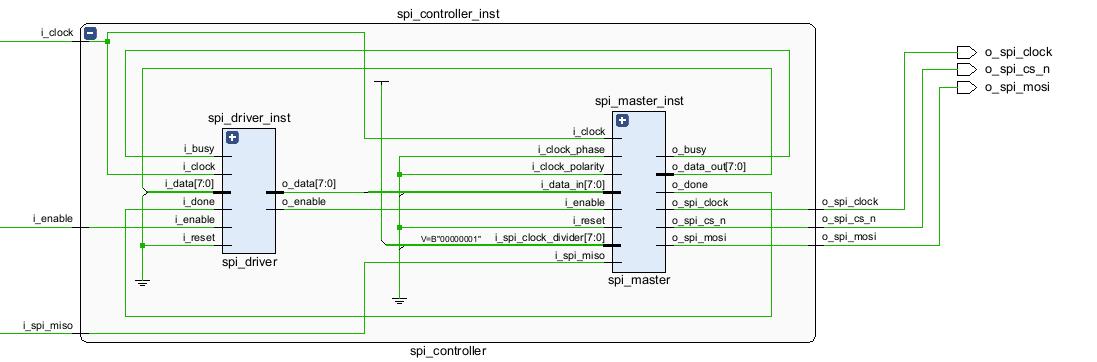

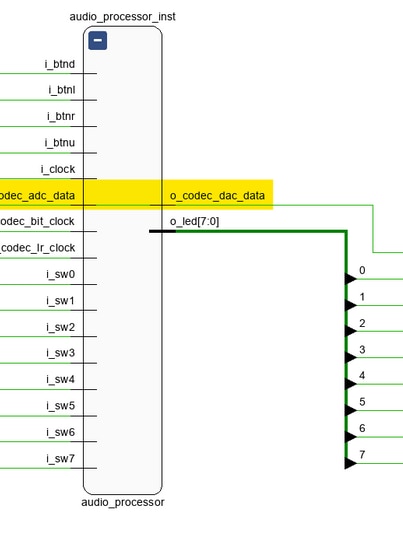

I'm new to FPGA and ZedBoard, and for educational purpose, I'm trying to recive signal from microphone(or LINE_IN) and passthrough it to headphones(or LINE_OUT). Eventually I'm going to create a sound recognition system(frequency detection to be precisie), but for now, I want to properly set up audio codec, and check on headphones if I can hear myself. I found interesting project here: https://www.rtlaudiolab.com/page/4/ (part1-5) that describes how to passtrough audio using SPI communication. I set up everything, just like on this website, but have a problem with SPI driver(which is the codec audio if I understand that correctly), because the data_in are going nowhere. I don't know if that's how it supossed to be, but common sense tell me that it shouldn't be that way. Also, I can generate a bitstream and program zedboard, but i can't hear nothing.

I would be thankful for any advice and help.

PS. Acording to website of the project, i should press BTNC before i could hear anything but that doesn;t help either.

Here are screenshots from the vivado: