Hi,

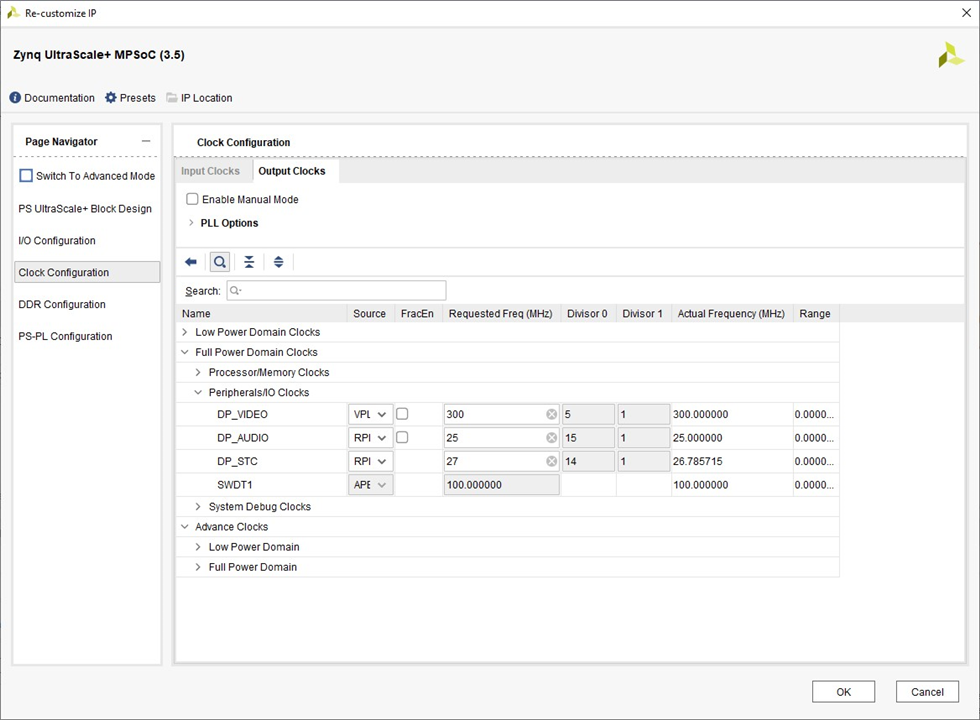

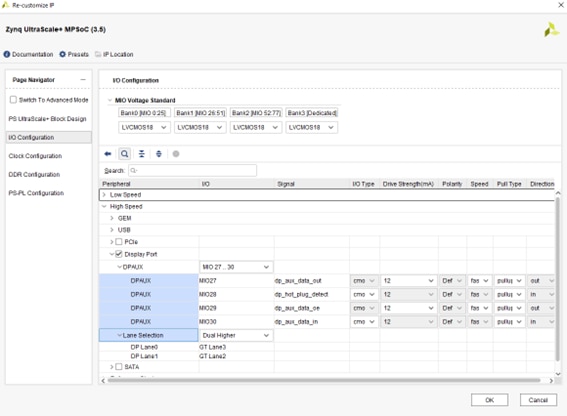

I'm trying to run xdpdma reference example from Vitis 2023.1 in a ZUBoard1CG with a DPEMMC module connected to J2 High Speed Expansion Connector. The block diagram just include a single zynq ultrascale mpsoc IP, with enabled Display Port configured as follow:

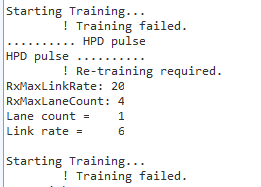

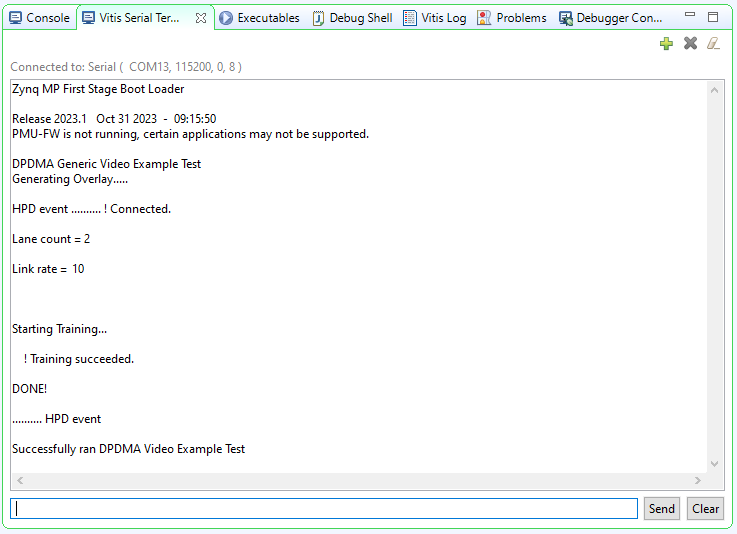

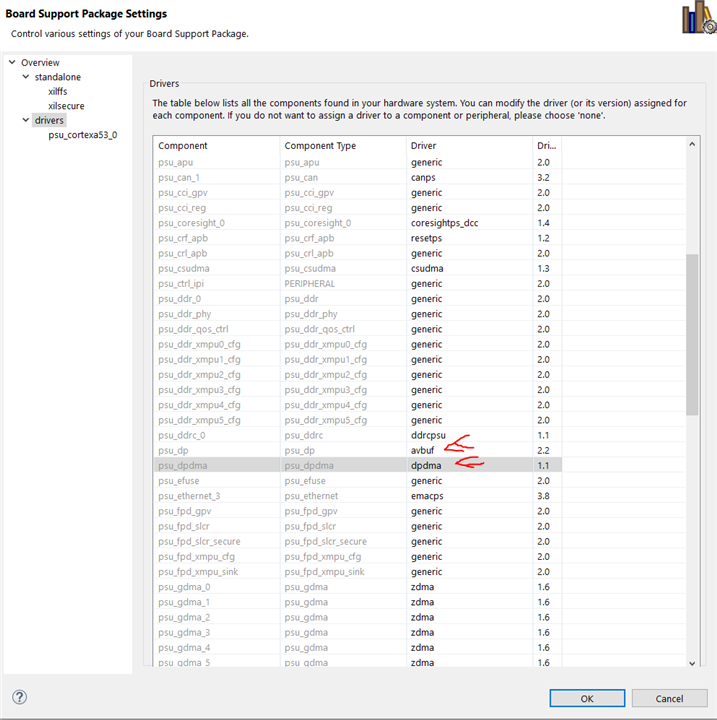

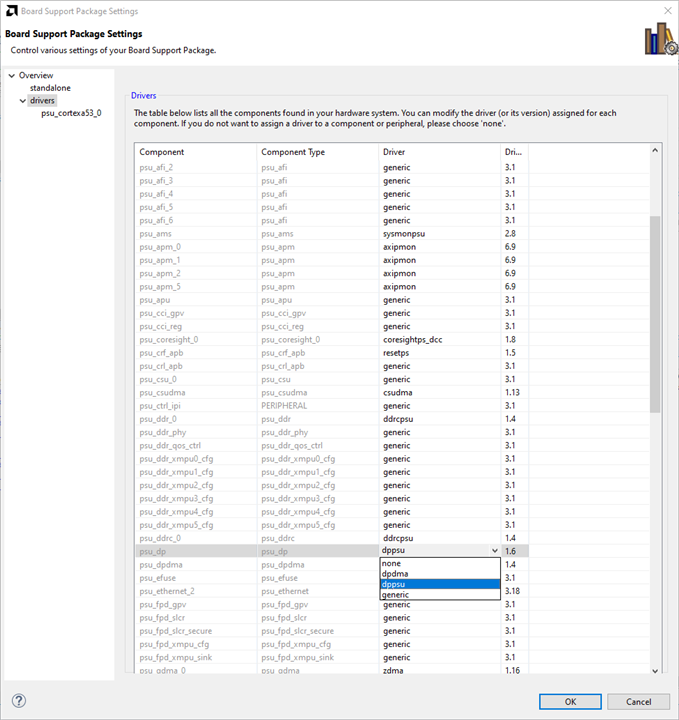

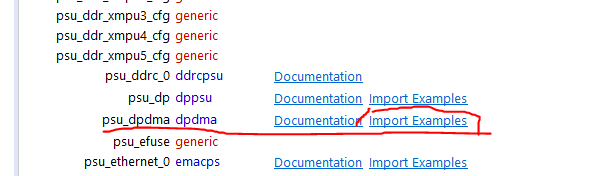

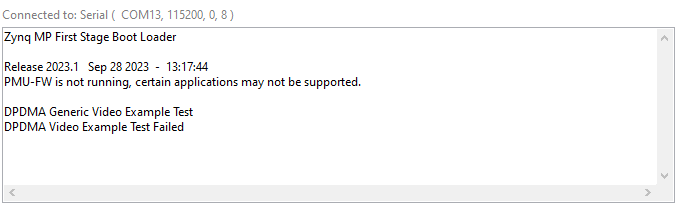

After generating the bitstream and exporting the platform, i created a standalone application in Vitis 2023.1 by importing the xdpdma_video_example into workspace. However, when i try to run this example, the test fails, showing the following messages:

The problem seems to be related to the initialization of the DisplayPort TX core (XDpPsu_InitializeTx). Does any of you have any idea about which is the problem?. It is possible to get a standalone reference design from Avnet for successfully integrate the DPEMMC module with ZUBoard1CG board?. It is very frustrating to buy a module with such a poor support as this, with just a brief description and an schematic. Any help will be appreciated. Thanks