A little over 2 months ago i have my first exploration with Zynq UltraScale+ MPSoC. It started with RoadTest Review for Ultra96. I didn't take part in the roadtest (as i have another ongoing one) but it gets me attracted to look at it closer. Over the past few years, due to my work, i am frequently poked on ultrascale, although i do not use one. The most i have used is still the zynq (ZedBoard, picoZed, miniZed, ZC702 eval board). Coincidentally, there is a local Xilinx event which i attend a little over 1.5 months ago, which has enlighten me further on this new family.

The Zynq UltraScale+ MPSoC is a beast, and the ultra96 is a good start to trying it out. I call it a small beast. First, let's look at why it is a beast.

Figure 1: Main elements of Zynq UltraScale MPSoC

This is the first MPSoC family, which is a multi core system on chip. On top of that it has programmable logic and specific interconnect all in the same chip. So, we can group them into 3 main elements, name processing system (PS), programmable logic (PL) and interconnect. We look at the elements one by one.

Processing System

The PS contains processors, fixed peripherals, clocks, memory, and memory controllers. MPSoC provide quad core or dual core variants. The core is ARM Cortex-A53 based. As you can see in figure 2 below, it also features a GPU in the form ARM Mali-400 MP. There is also dual core ARM Cortex-R5 real time processor in the real-time processing unit. For peripherals,Zynq UltraScale+ MPSoC provides quite a number, separated into high speed connectivity low speed general connectivity like in Figure 2.

Figure 2 Processing System

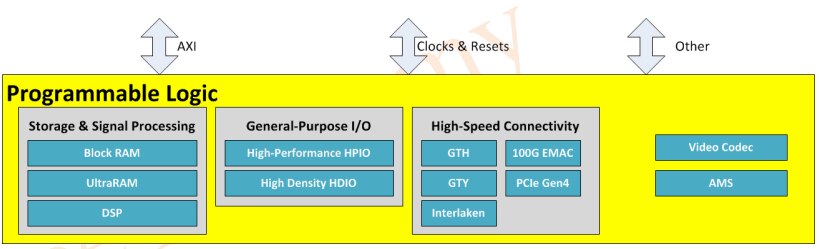

Programmable Logic System

In the PL, based on 16nm technology, it has variant with 103-1143 system logic cells. The Block RAM from 4.5-34.6Mb, UltraRAM memory from 0 - 36 Mb and DSP slices from 240-3528. Some variant has video codec unit. For example, the ultra96 's MPSoC doesn't have video codec, whereas the most costly ZCU102's has one. The PL includes high speed connectivity like PCIe Gen3 x16/Gen4 x8 150G Interlaken and 100G Ethernet MAC. As i understand, the AMS is the analog mixed signal where Xilinx continues to offer an integrated and comprehensive System Monitor (SYSMON) function for UltraScale+ product families. This very popular feature facilitates monitoring of the physical operating conditions of the FPGA including the device’s junction temperature, supply voltages, and external voltage – a key requirement for many industry standards, including FIPS 140-2, IEC 61508, and ISO26262

Application & Pricing

Not all variant of the family has all the components, depending on application area. It is separated into smart control + vision and smart control. One such component is the video codec. With onboard real-time cpu, the family is able to provide low latency determinism and power efficient required for machine learning and edge applications. I haven't checked the price per chip directly, but according to my colleague, it is more than USD100 in low quantity. this make gettng an entry level eval board like ultra96 still the best choice for hobbyist and commercial customer who want to try out the Zynq UltraScale+ MPSoC. So my next step is to try out the ultra96, which i provide in my next blog.

Pros

Of course with all these powerful mashup into MPSoC, the family has enable FPGA to close the gap with ASIC and NVidia GPU, especially for embedded development involving AI, especially current hot topic like convolution neural network (CNN)

The availability of relatively low price ultra96 makes it practical to try new design with this board.

Cons

the biggest hurdle is the learning curve to make full use with this family. Considering the fact that it has 3 different types of ARM cores with different task, and so many diverse connectivity, it is a nightmare for the need of having a multidisciplinary team (ARM firmware, FPGA firmware and the software engineer who integrate them) to handle this family.

Conclusion

The future is AI driven, Many of the application today can be AI driven, and ZynQ UltraScale+ MPSoC is enabling us to use FPGA. A full development from scratch is challenging, but for prototyping and even hobbyist, the inclusion of PYNQ support really cut down the learning time and implementation time. i would want to believe that the PYNQ performance won't be beating the pure manual handcoding, but it does save at least 30% of time. for a typical project that last one year, 30% is more than 1 quarter of saving, and i don't even need to calculate based on the number of engineers needed, multiply by 1 quarter.

Top Comments