The sun has long set on Dual inline Packages (DIP) for high speed digital components. I have joked the Advanced High-speed CMOS (AHC) family in the 74 series are too fast for their own good in a DIP package.

The industry standard pinout of the 74x logic series puts the power supply connections at opposing corners of the IC; namely pins 7 and 14. This results in the longest package interconnect path for IC to PCB landing pads and consequently more opportunities for RLC parasitics to creep into the PDN network from the perspective of silicon die.

What does the literature have to say?

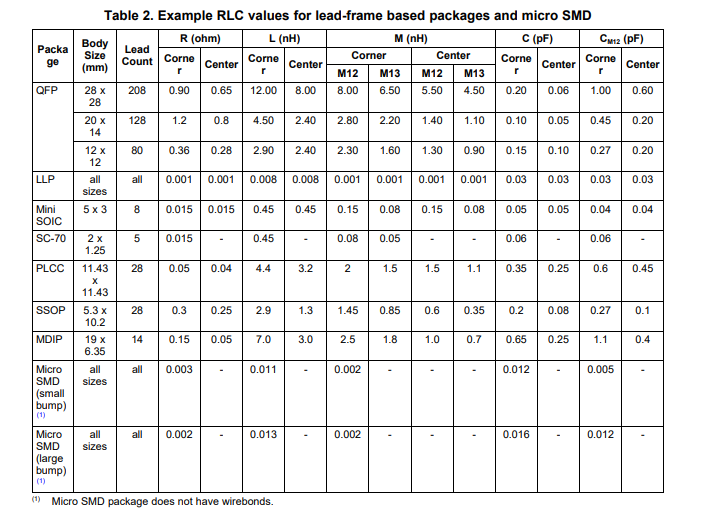

A TI application note: AN-1205 Electrical Performance of Packages (https://www.ti.com/lit/an/snoa405a/snoa405a.pdf)

Claims a DIP-14 package has approximately 7 nH of interconnect inductance for the corner leads.

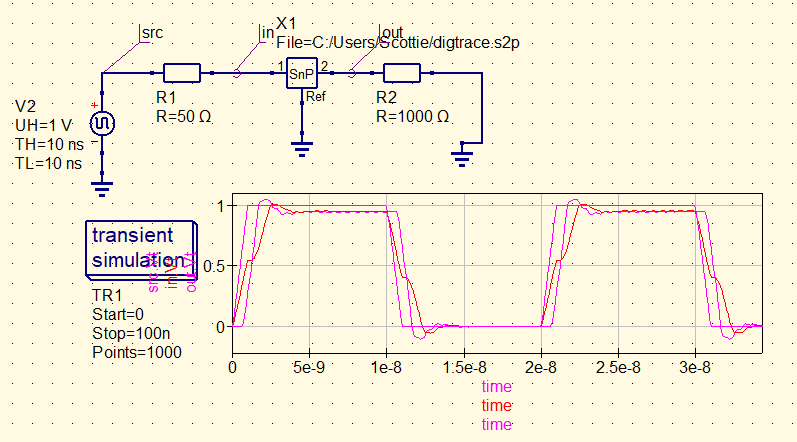

Simulation

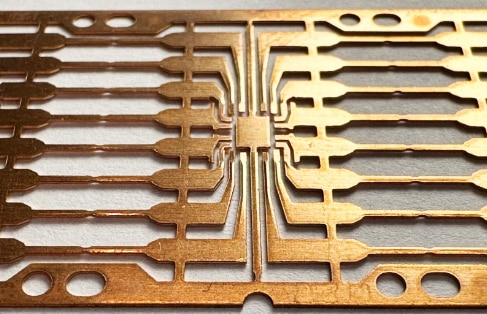

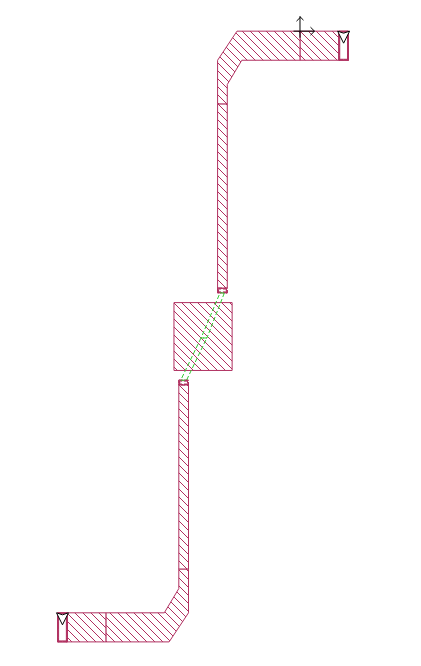

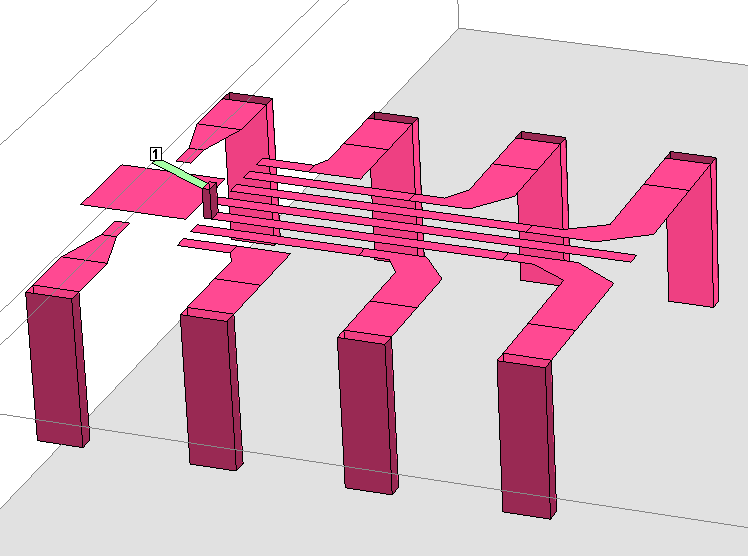

The lead frame internal to a DIP package looks something like the following:

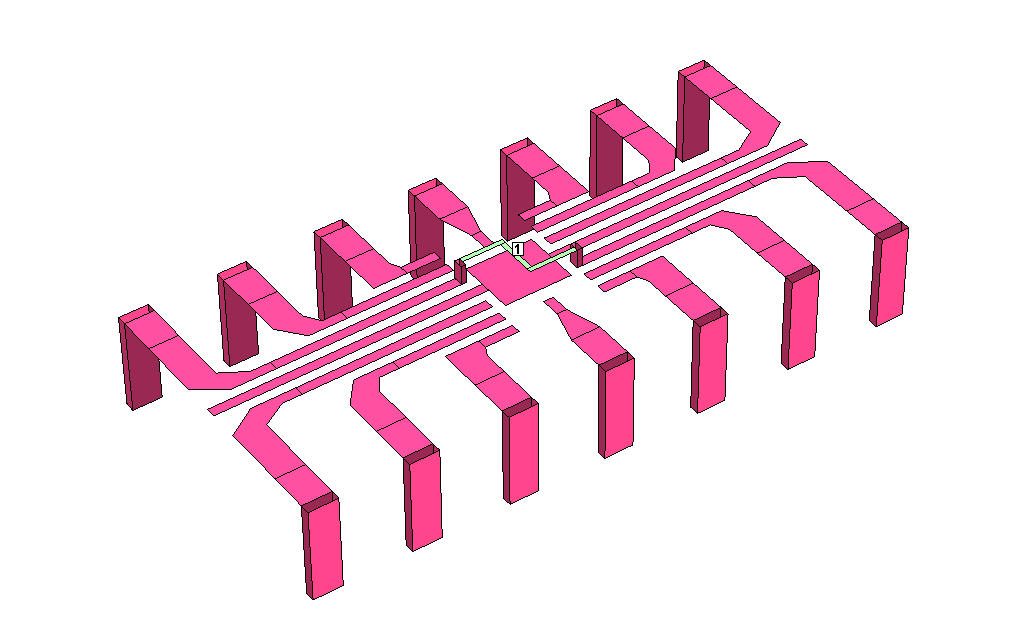

Using my new favorite free E&M simulation tool Sonnet (https://www.sonnetsoftware.com/), I drew a crude approximation of the metal interconnect in a DIP14 package.

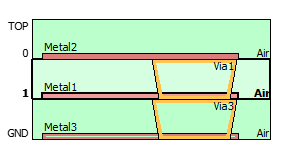

Although it doesn't appear in the 3D preview, I set the lead frame metal to have a thickness of 10 mils. In the free lite edition of Sonnet you are limited to a 3-layer stackup

It is what it is, but for small simulation studies, I think it is adequate. The bottom ground layer is a solid ground plane, so all the pins are shorted at the hypothetical PCB landing pads.

For a first pass, I drew the bond wires on the rectangular grid

You can draw any geometry you like. However, more complicated geometry requires more complicated and detailed meshing to represent said geometry. Which requires more simulation memory. In the lite edition of Sonnet you are limited to 64 MB.

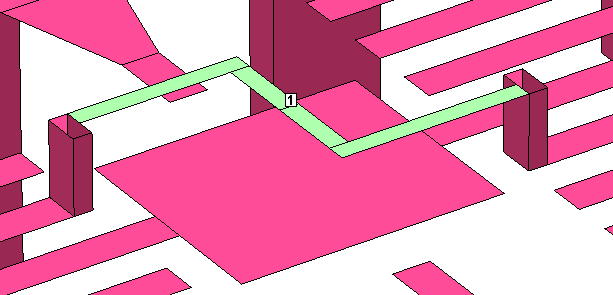

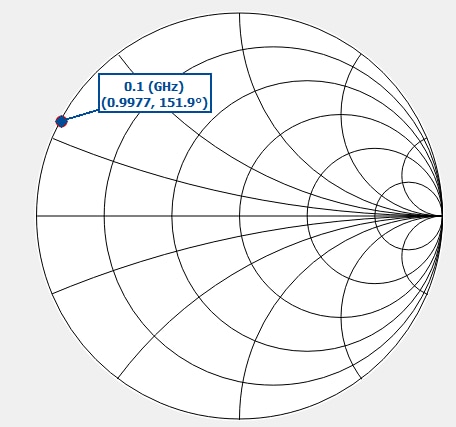

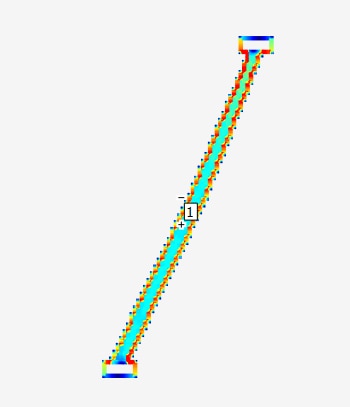

The test feed port is illustrated as the box labeled "1" in the figure above. I ran an S-parameter simulation at 100 MHz. From the perspective of the logic IC we see a short plus some inductance

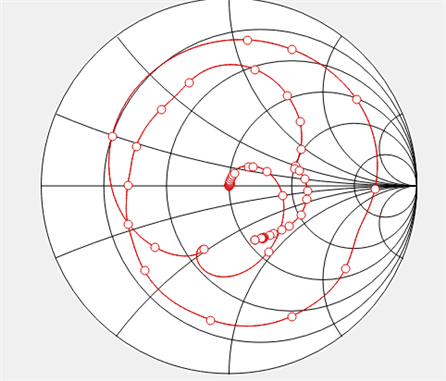

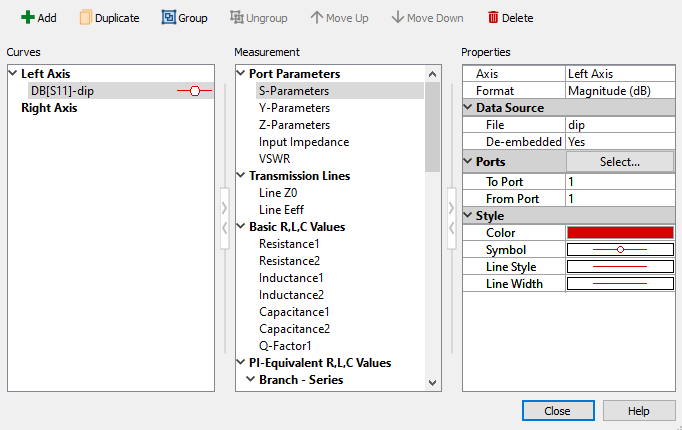

Sonnet has a number of other convenience graphing formats

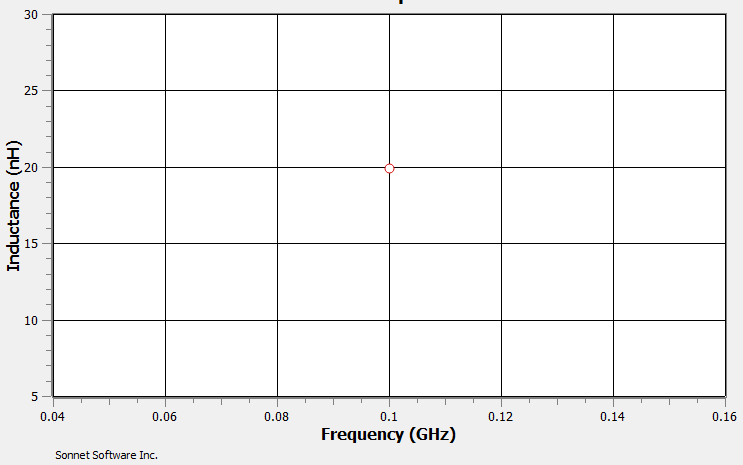

Such as the equivalent inductance

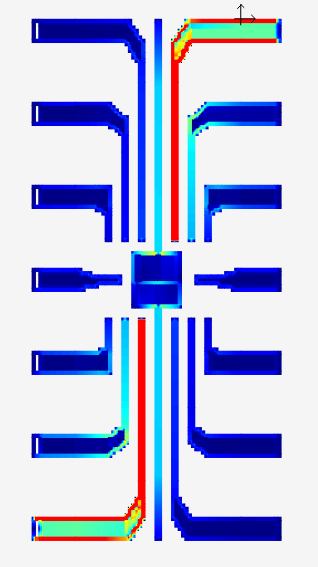

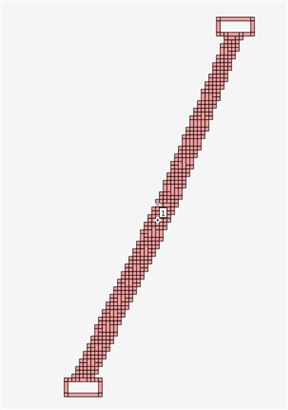

We see a total inductance of 20 nH through both pins 7 and 14, or approximately 10 nH per corner lead. Here is the current distribution in the lead frame at 100 MHz

We could also simplify the geometry removing all addition pins and generate a much finer mesh.

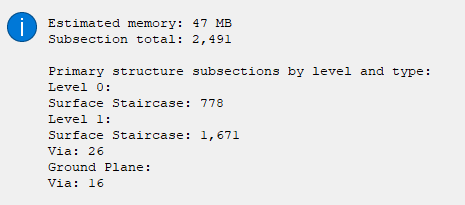

In this case, I ended up with a memory requirement of 47 MB, just below the 64 MB limit, with:

With the alternate bond wire geometry and additional mesh resolution an inductance of 18.5 nH was simulated.

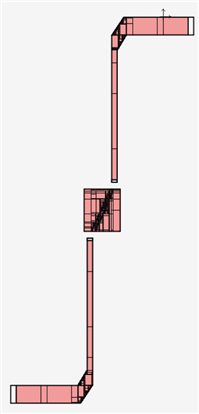

Another approach is simulate just half the package, using a wall referenced feed port

Similar to the other 2 simulations, this third simulation resulted in a corner lead inductance of 9.3 nH.

I know there are lots of E&M simulation tools out there, this is just a "free" one I am experimenting with.

Pretty neat.