电动自行车具有环保节能,价格合适,无噪声,便利等特点,因此,电动自行车成为当今社会人们主要的代步工具。与此同时,消费者和商家对整车的质量及可靠性要求也越来越高。作为整车四大件之一的控制器的可靠性显得尤为重要。功率MOSFET以及相关的驱动电路的设计直接与控制器的可靠性紧密相关,尤其是在续流侧,MOSFET的驱动电路设计不当,续流侧 MOSFET很容易损坏,因此本文就如何测量、分析与调整控制器的MOSFET驱动线路来提高MOSFET的可靠性作一些研究,以便能够为设计人员在设计产品时作一些参考。

1 MOSFET开关过程及MOSFET参数模型

1.1 MOSFET开通过程

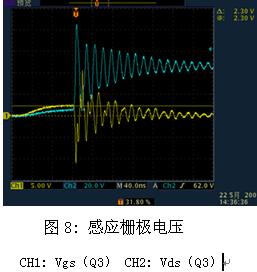

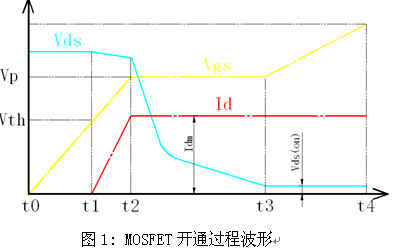

MOSFET开通过程中的波形见图1所示,其开通的过程可分为四个阶段:

阶段A、t0¬—t1:门极电压Vgs由0V逐渐上升至Vth,在此期间内MOSFET关闭,Vds不变,Id=0A。

阶段A、t0¬—t1:门极电压Vgs由0V逐渐上升至Vth,在此期间内MOSFET关闭,Vds不变,Id=0A。

阶段B、t1—t2:门极电压Vgs由Vth上升至平台电压Vp,门极电压为Cgs充电。在此期间内MOSFET开始导通并进入饱和状态,Vds基本保持不变,Id由0上升至Id(max)。

阶段C、t2—t3:门极电压Vgs保持不变,门极电压为Cgd充电。在此期间内MOSFET仍处于饱和状态,Vds迅速下降,Id保持不变。

阶段D、t3—t4:门极电压Vgs由Vp继续上升,在此期间内MOSFET退出饱和状态进入完全导通状态。

MOSFET关断时波形与开通时相反,在此不再叙述。

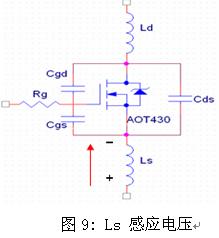

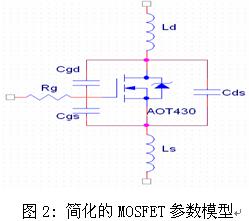

1.2 MOSFET寄生参数

MOSFET寄生参数模型如图2所示。由于MOSFET的结构、引线和封装的影响,在MOSFET制作完成后,其各引脚间存在PN结寄生电容和寄生电感,引脚上存在引线电感。由于源极的引线较长,Ls一般要比Ld大。 因此,我们在实际的开关应用中应特别注意寄生电容和引线电感对开关波形的影响,特别是在负载为电感性负载时更应注意。MOSFET的输入电容、反向传输电容和输出电容分别表示如下:

因此,我们在实际的开关应用中应特别注意寄生电容和引线电感对开关波形的影响,特别是在负载为电感性负载时更应注意。MOSFET的输入电容、反向传输电容和输出电容分别表示如下:

Ciss=Cgs+Cgd

Crss=Cgd

Coss=Cgd+Cds

2 两种常见的MOSFET驱动电路

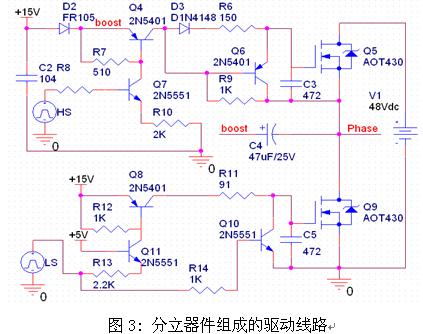

2.1由分立器件组成的驱动电路

由分立器件组成的驱动电路((如图3所示),驱动电路工作原理如下:

A.当HS为高电平时,Q7、Q4导通,Q6关闭,电容C4上的电压(约14V)经过Q4、D3、R6加到Q5的栅极,使Q5导通。在导通期间,Q5的源极电压(Phase)接近电源电压Vdc,所以电容两端的电压随着Phase电压一起浮动,电容C4亦称为自举电容。Q5靠C4两端的电压来维持导通。

B. 当HS为低电平时,Q7、Q4关闭,Q6导通,为Q5的栅极提供放电回路,从而使Q5很快关闭。当Q5关闭后,由于下管的开通或负载的作用,使得Phase电压下降接近0V,从而使C4经过+15V→D2→C4→GND回路充电,为下一次导通做好准备。

C. 当LS为低电平时,Q8、Q11导通,Q10关闭,驱动电路通过R11为下管Q9的栅极充电,使Q9导通。

D. 当LS为高电平时,Q8、Q11关闭,Q10导通,为Q9的栅极提供放电回路,使Q9关断。

E. 当HS和LS同时为高电平时,上管开通下管关闭。当HS和LS同时为低电平时,上管关闭下管开通。在实际应用中,为了避免上下管同时开通,HS和LS的逻辑要靠MCU或逻辑电路来保证。

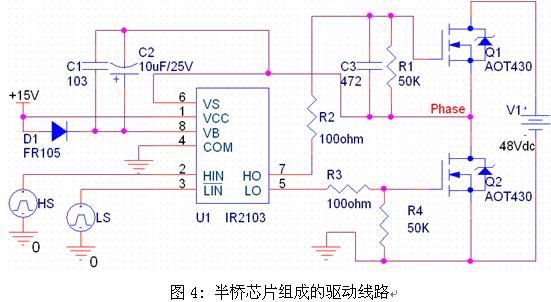

2.2 半桥驱动芯片组成的驱动电路

半桥驱动芯片组成的驱动电路如图4所示,工作原理如下:

A.当HS和LS同时为高电平时,HO有驱动电压输出,使Q1开通。当HS和LS同时为低电平时,LO有驱动电压输出,使Q2开通。

B.电容C2与分立器件驱动电路里的C4作用相同,同样为自举电容。

C.电容C1为去藕电容,为抑制功率MOSFET开关时对驱动电路浮动电源部分的干扰,一般应加上此电容。

2.3 两种驱动线路的区别

A.两种驱动电路在开通时能提供基本相同的驱动电流驱动MOSFET开通,但在MOSFET关断时,分立器件驱动电路因为有三极管放电,所以能提供更大的放电电流关闭MOSFET,而半桥驱动电路由于要经过栅极电阻放电,所以放电电流相对较小,导致MOSFET关闭时间过长,开关损耗相应增加。解决的办法可以是在驱动电阻上反并联一只二极管并增加一个放电的PNP三极管。

B.分立器件驱动电路用的器件较多,可靠性相对没有半桥芯片的驱动电路高。但前提条件是半桥驱动芯片的驱动电路要设计合理。

3 MOSFET驱动线路的要求及参数的调整

门极电压不能超过Vgs的最大值。在设计驱动线路时,应考虑驱动电源电压和线路的抗干扰性,确保MOSFET在带感性负载且工作在开关状态时栅极电压不超过Vgs的最大值。

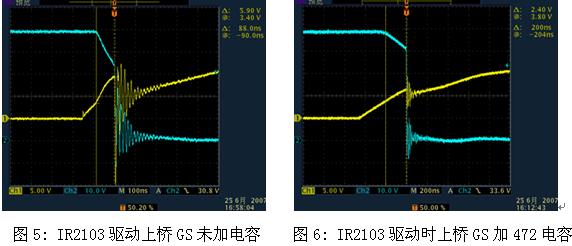

为了能够减少MOSFET的开关损耗,驱动线路应能提供足够大的驱动电流,使开通和关断的时间尽可能短,同时,尽量减少门极电压的高频震荡。如果要获得同样的RC时间常数,使用较小的驱动电阻和较大的电容可以获得较好的驱动特性,但驱动线路的损耗同时也增加了。 图5和图6是实际应用中的测试波形,从图中我们可以看出:①电容的增加使得开启的时间变长,增加了开通损耗。②电容的增加,使得门极电压的高频震荡减少。同时,由于米勒平台的振荡减小,MOSFET在米勒平台期间的损耗也会相应减小。

图5和图6是实际应用中的测试波形,从图中我们可以看出:①电容的增加使得开启的时间变长,增加了开通损耗。②电容的增加,使得门极电压的高频震荡减少。同时,由于米勒平台的振荡减小,MOSFET在米勒平台期间的损耗也会相应减小。

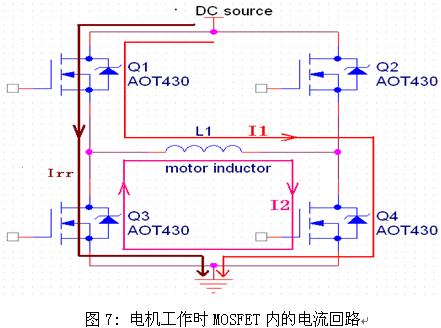

延长MOSFET的开通时间可以减小开通时的涌入电流。由于电机负载为感性负载,所以在PWM关断时存在续流现象(见图7中的I2),为了减小续流侧反向恢复电流(Irr)的大小,PWM侧开关管的开通速度不宜过快。由于MOSFET处于饱和区时有公式:Id=K*(Vgs-Vth)2,(K为一常数,由MOSFET的特性决定)。所以在一定的温度和Vds条件下,从MOSFET的门极驱动电压Vgs可以判断MOSFET中的电流大小。图5中Vgs峰值为9.1V,图6中Vgs峰值为6.4V,所以增加电容使得峰值电流减小。Id也可从MOSFET的转移特性图中获得。

由于MOSFET的封装电感和线路的杂散电感的存在,在MOSFET反向恢复电流Irr突然关断时,MOSFET(Q3)上的电压Vds会出现振铃(如图8中CH2所示)。此振铃的出现会导致Vds超过MOSFET的击穿电压从而发生雪崩现象。如果线路中出现振铃,我们可以通过以下方法来减小振铃:

A.设计线路时应考虑线路板布线:①尽量缩短驱动线路与MOSFET之间的线迹长度;②使大电流回路的铜箔走线尽量短且宽,必要时可以在铜箔表面加锡;③合理的走线,使大电流环路的面积最小。

B.如果线路杂散电感已经确定,可以通过减小PWM侧的MOSFET开通速度来减小在续流侧的MOSFET上的Vds振铃,从而能够使MOSFET上的Vds不超过最大耐压值。

C.如果以上两种方法都不能很好地解决问题,我们可以通过在相线上加snubber的方法来抑制线路的振铃。[3]

注意Cdv/dt产生的栅极感应电压。如图7所示:在控制MOSFET Q1的导通开关期间,因为Q1的米勒效应和导通延迟的缘故,满输入电压并不会立刻出现在Q3的漏极上。施加在Q3上的漏极电压会感应出一个通过其栅-漏极间米勒电容Cgd(见图2)进行耦合的电流。该感应电流在Q3的内部栅极电阻Rg和外部栅极电阻的两端产生一个压降。该电压将对Q3栅极上的栅-源极间电容Cgs进行充电。Q3上的感应栅极电压的幅度是dv/dt、Cgd、Cgs和总栅极电阻的一个函数。

感应栅极电压如图8中的CH1所示,其值已达到2.3V。另外,由于源极引线电感的存在,在Q3内的电流迅速减小时,会在Ls的两端感应出一个极性为上负下正的电压,如图9所示,此时加在DIE上的电压Vgs(die)要大于在外部引脚上测量的Vgs电压,所以由于Ls的影响,使得MOSFET有提前导通的可能。如果下管由于感应电压而导通,则会造成上下管穿通,如果MOSFET不能承受此穿通电流,MOSFET就会损坏。

防止产生Cdv/dt感应导通的方法:

A.选择具有较高门限电压的MOSFET。

B.选择具有较小米勒电容Cgd和较小Cgd/Cgs的MOSFET。

C.使上桥(Q1)的开启速度变慢,从而减小关断时的dv/dt和di/dt,使感应电压Cdv/dt和Lsdi/dt减小。

D.增加Q3的栅极电容Cgs,从而减小感应电压。

保留Cdv/dt感应导通的好处

Cdv/dt感应导通有一个好处:它能够减小续流侧MOSFET上的电压尖峰和Vds振铃(V = L×dIrr/dt; L:环路寄生电感), 同时也减小了系统的EMI干扰。因此,在设计MOSFET驱动线路时,我们应根据实际情况来权衡驱动参数的调整,即究竟是阻止Cdv/dt感应导通以求最大限度地提升电路效率和可靠性还是采用Cdv/dt感应导通来抑制过多的寄生振铃。

4 结论

4.1 在开始设计之前,应该全面了解所选MOSFET的参数,判断MOSFET是否能满足产品要求,包括MOSFET的耐压(Vgs和Vds)、最大电流等参数,确保当工作条件最恶劣时这些参数不要超过MOSFET的最大额定值。

4.2 在线路设计阶段,必须进行热设计,以确保MOSFET工作在安全工作区。应特别注意线路板的布线,尽量减小线路杂散电感。

4.3 在不影响可靠性的情况下尽量缩短开关时间,将开关损耗降到最低。有时为了进一步提高效率,降低温升,还可采用同步整流。