The rectangular substrates provide 3.7x more usable area than 300mm (12-inch) round wafers. (Image credit: TSMC via LinkedIn)

TSMC (Taiwan Semiconductor Manufacturing Co) is reportedly developing rectangular substrates for AI applications, according to an article from Nikkei. The development is still in its early stages and could take several more years before it's fully realized. That said, if the company manages to commercialize the technology, it could revolutionize the chip-making industry.

Instead of traditional 300mm diameter wafers, TSMC's new method of manufacturing rectangular substrates will boost that area up to 510mm by 515mm, providing 3.7 times more increased space. This would effectively allow for more chips to be produced from a single wafer, reducing the waste found on circular wafers. As with any innovative process, there are drawbacks, with the most notable being the need for new equipment. TSMC admits it can't use traditional fabrication tools for the new process; however the company is reportedly working with equipment and material suppliers, but the details are scarce.

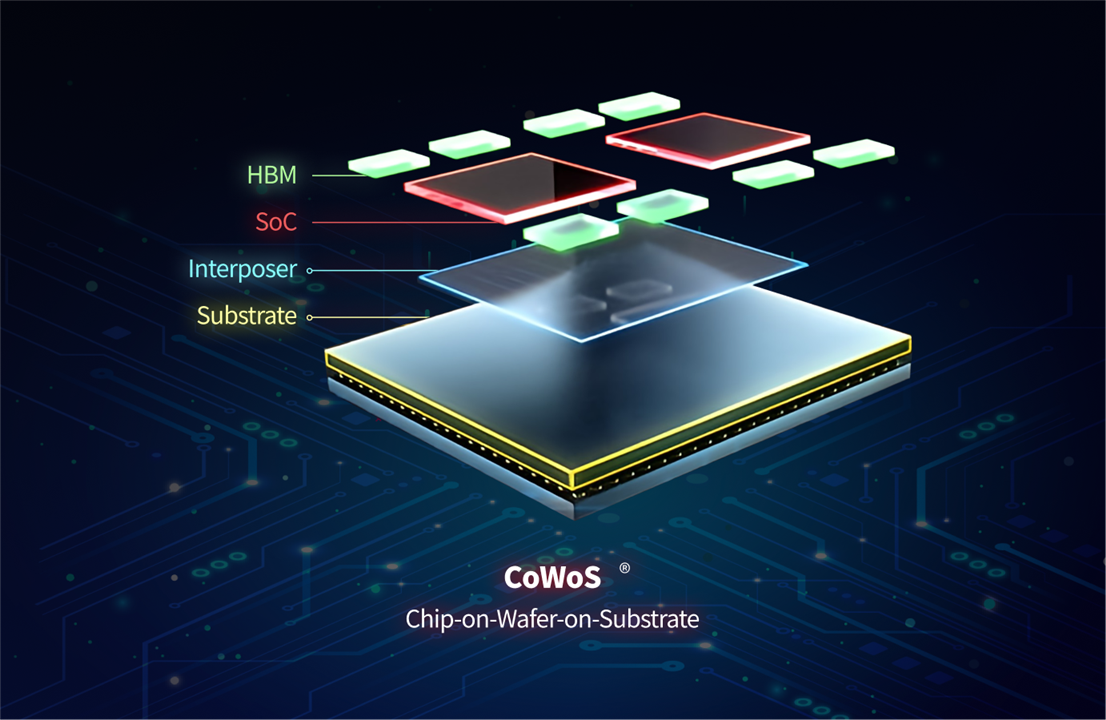

TSMC mentioned that it's closely following advancements in next-gen packaging technologies, including panel-level packaging. Once regarded as less advanced, chip packaging has now become a key factor in driving semiconductor innovation. For example, Nvidia's AI computing chips, such as the H200 and B200, rely on TSMC's 300mm CoWoS technology, which is crucial for manufacturing processors for faster data processing.

As AI chips grow in size and complexity, the efficiency of traditional manufacturing methods will decline, prompting the need for TSMC's rectangular wafers. Pushing toward those rectangular substrates is considered a long-term plan and will likely take five to ten years before becoming commercialized, as manufacturing equipment will need to be overhauled to accommodate the new shape and ensure the success of the new packaging method.

Have a story tip? Message me at: http://twitter.com/Cabe_Atwell