Hi,I am a beginner in electronics and i just wanted to help with a certain circuit of mine that I was handling and it was a boost converter but the input 3.7v is the same as the output and wanted the output to be 5v DC

Be sure to click 'more' and select 'suggest as answer'!

If you're the thread creator, be sure to click 'more' then 'Verify as Answer'!

Hi,I am a beginner in electronics and i just wanted to help with a certain circuit of mine that I was handling and it was a boost converter but the input 3.7v is the same as the output and wanted the output to be 5v DC

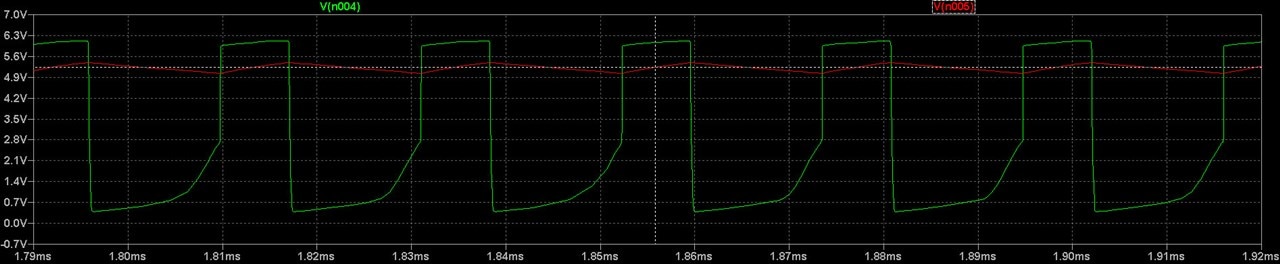

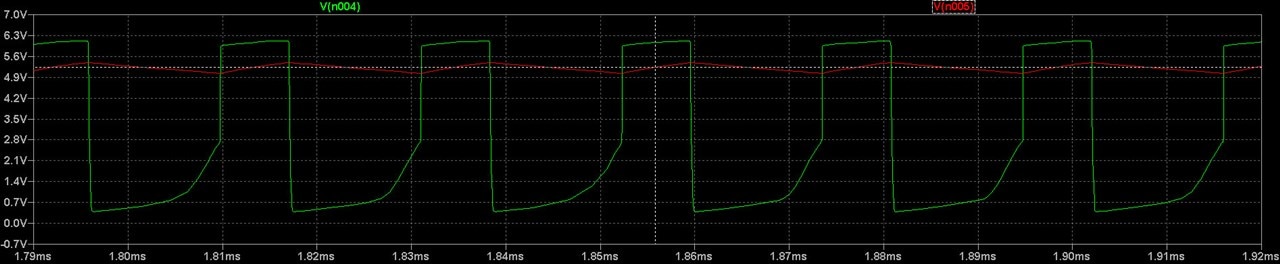

I simulated the TLC555 boost converter ckt I mentioned using LTSPICE XVII at 2.7 VDC input and it gave 5.2 VDC out. I didn't optimize the pulse width nor did I put in a regulation feedback loop and it runs open-loop with a fixed pulse width in this version. But it can easily be done by modulating the CONT pin (pin-5) with an opamp as an error amp along with a dc reference.

If you look below at the waveforms, the red trace is the DC output of about 5.2V with some ripple. The Green is the bottom-side of the inductor (also the FET drain). The FET I chose here was one with a low enough Vth to make the ckt work at the low VIn of 2.7 VDC. I wouldn't try to build this ckt with that FET. Instead, choose a good, low Vth and low RDSon N-CH FET if you want to build this.

I got the SPICE model of the CMOS 555 timer IC, TLC555 from the TI website. Just Google TLC555 SPICE model and you'll find it. I had no convergence problems with this IC model, it seemed to simulate pretty well and fast.

I simulated the TLC555 boost converter ckt I mentioned using LTSPICE XVII at 2.7 VDC input and it gave 5.2 VDC out. I didn't optimize the pulse width nor did I put in a regulation feedback loop and it runs open-loop with a fixed pulse width in this version. But it can easily be done by modulating the CONT pin (pin-5) with an opamp as an error amp along with a dc reference.

If you look below at the waveforms, the red trace is the DC output of about 5.2V with some ripple. The Green is the bottom-side of the inductor (also the FET drain). The FET I chose here was one with a low enough Vth to make the ckt work at the low VIn of 2.7 VDC. I wouldn't try to build this ckt with that FET. Instead, choose a good, low Vth and low RDSon N-CH FET if you want to build this.

I got the SPICE model of the CMOS 555 timer IC, TLC555 from the TI website. Just Google TLC555 SPICE model and you'll find it. I had no convergence problems with this IC model, it seemed to simulate pretty well and fast.