Hello,

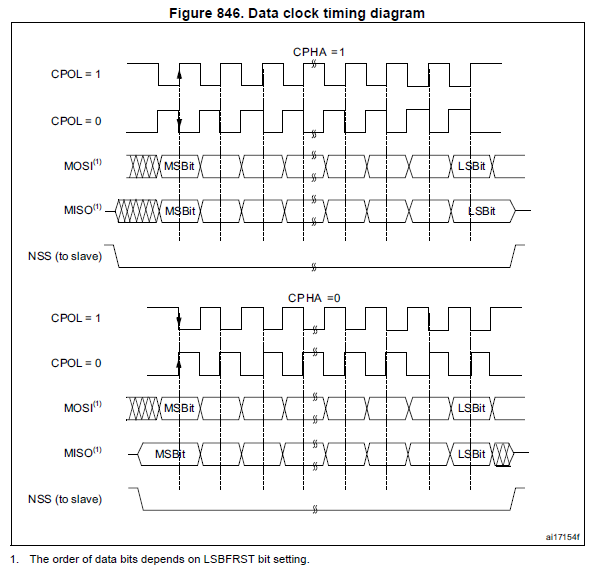

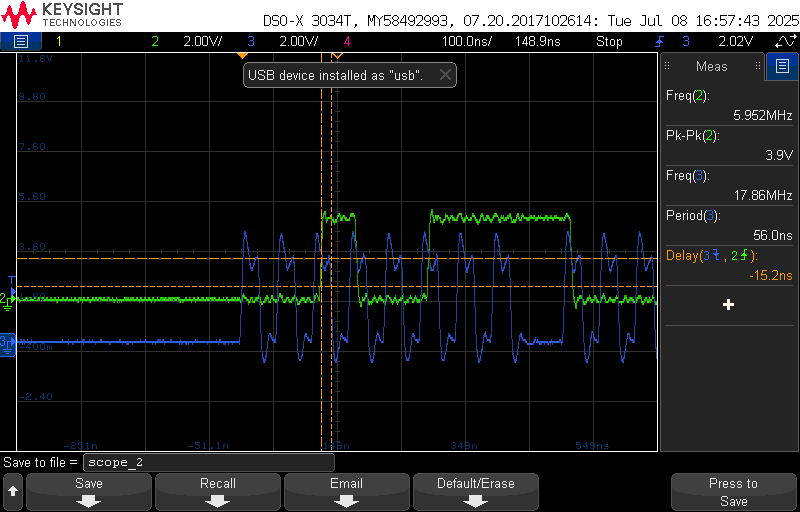

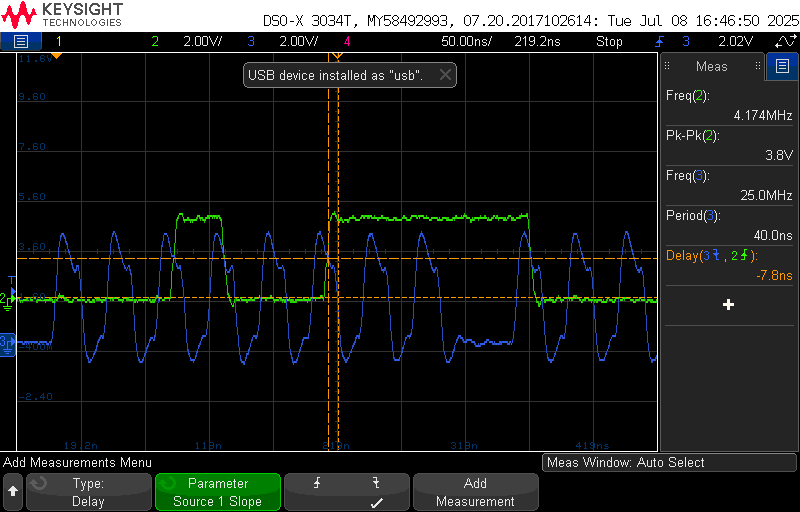

I am using PI CM 4 as SPI master and receiving data from the slave. The transmission works fine till 18 MHz in SPI mode01 or 11 (SPI mode 00 and 10 gives corrupts data even at lower speed). However, a bit shift is noticed beyond 18 MHz i.e when tested at 25 or 31 MHz the bit shifts by one place e.g If I am sending 00100111 00010111 then pi receives 00010011 10001011. I have tested with shorter wires but the problem still persist. The oscilloscope readings show no extra 0 as is recorded in, only change that is happening from 18Mhz to 25 Mhz is the delay between the rising edge of MISO to that of falling edge of SCK is decreasing with increase in clock speed: at 18Mhz it is 15.2ns, at 25Mhz it is 7.8ns and at 31 Mhz it is 3.2ns.

In given oscilloscope readings blue is clock (SCK) and green is MISO. The data is sampled at the falling edge of the clock.

Please help me fix this issue.