1. Introduction

In this blog, we will extend our previous LED blinking example to again blink more LEDs. We will see how we can use PYNQ to program our FPGA. In this design, we will use the low speed expansion header in the Ultra96v2 board to connect to external LEDs and then we will implement an 8-bit UP-DOWN counter using Python in PYNQ and then make our LEDs show us those numbers.

However, before we get started, it is necessary that we follow the PYNQ setup guidelines provided in the following link.

PYNQ Setup: https://ultra96-pynq.readthedocs.io/en/latest/getting_started.html

All the files for this blog are available here: https://github.com/rajivbishwokarma/element14_p2p_blogs

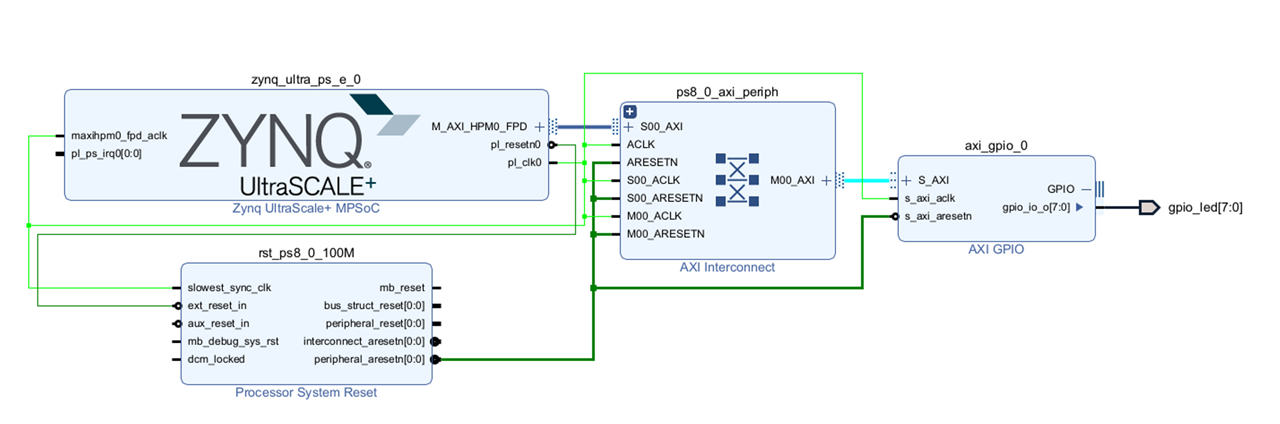

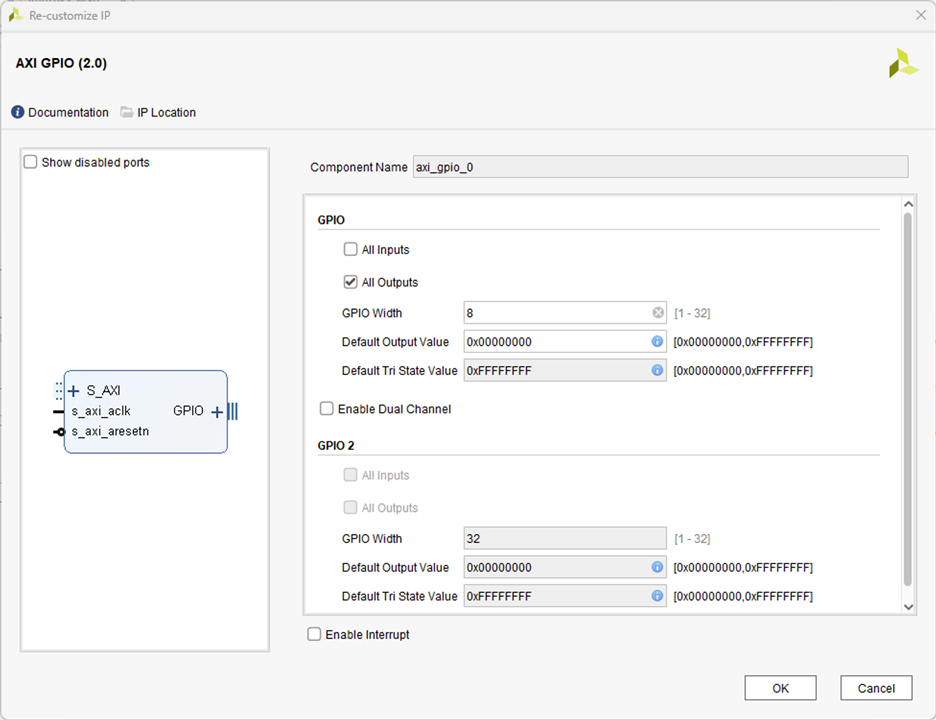

2. Setting up hardware in Vivado

The block design that we create in this project is similar to the previous block. But rather than using just 2 bit lines in the AXI GPIO, we will use 8.

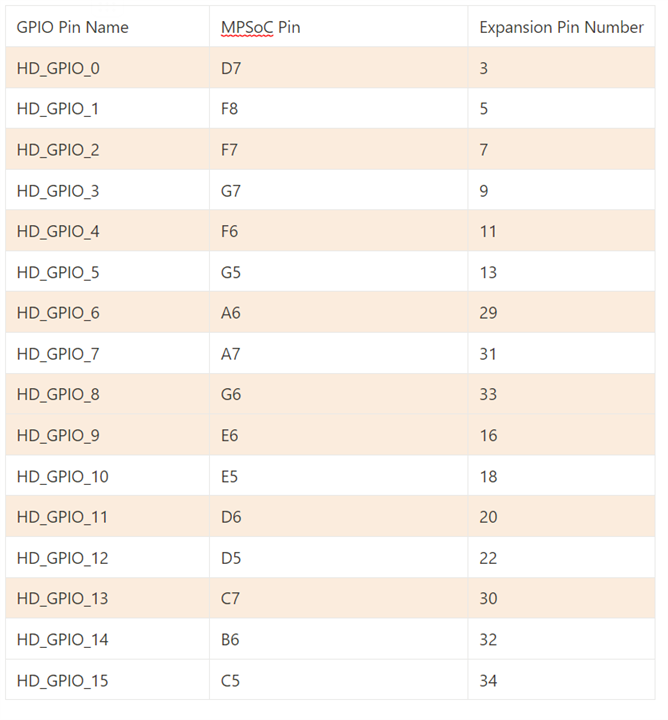

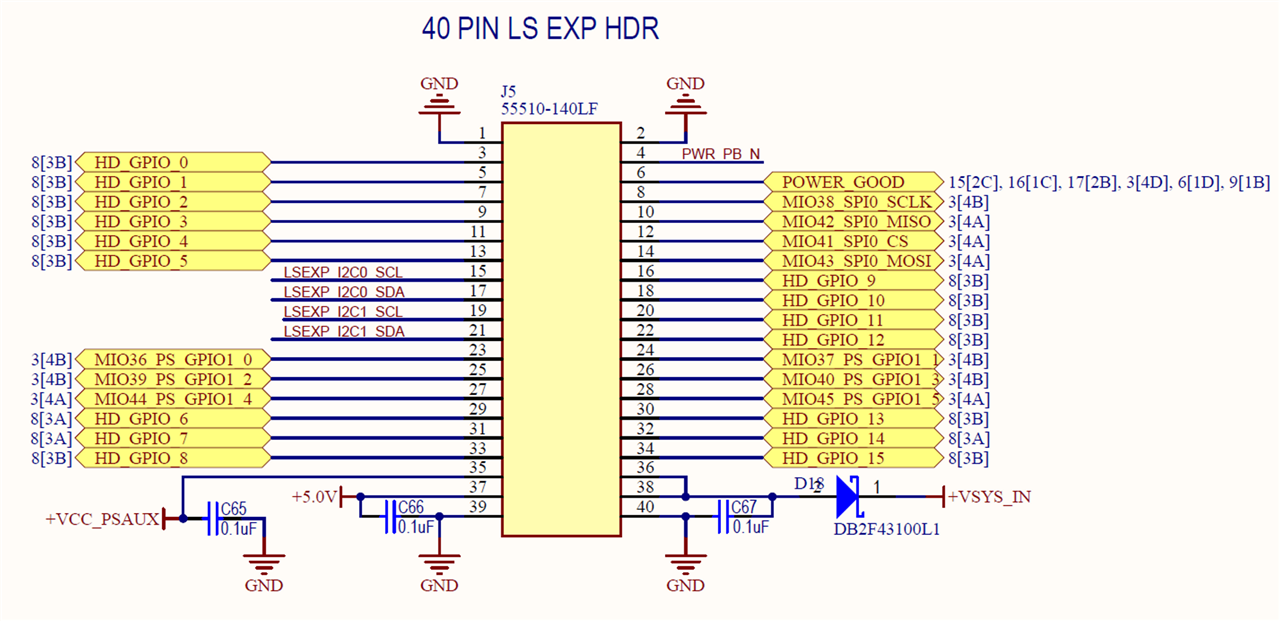

We then map the physical pins to the Zynq MPSoC pins in the constraint file. The way we do is using the Ultra96v2 schematic available here: Ultra96-V2 | Avnet Boards

In the schematic, we can see that the 40 PIN low-speed expansion header (LS EXP HDR) has the HD_GPIO_0 through HD_GPIO_15. So we can utilize all of them through PL. I have used the following orange highlighted pins because my jumper pins were larger than the spacing of the two pins in the LS EXP HDR and did not fit in slots sequentially.

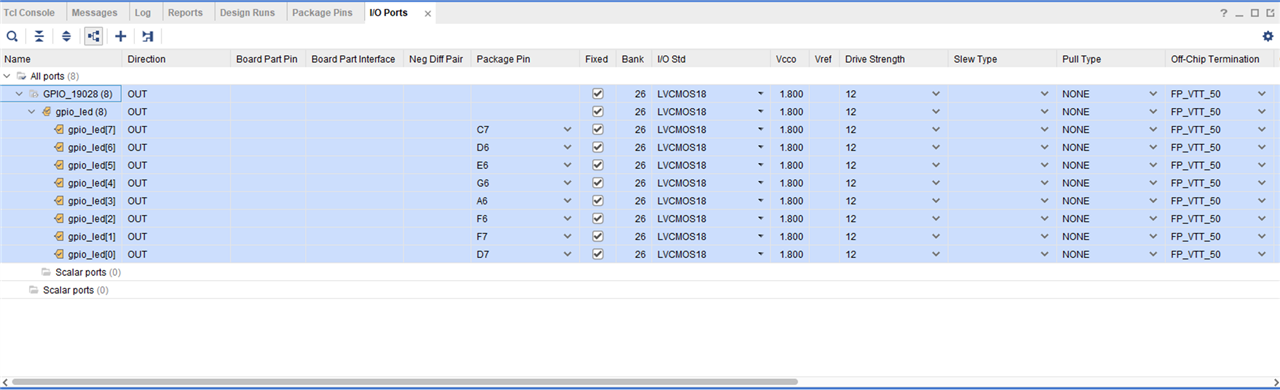

Then creating the constraint file according to the required specification.

[Note: This image is here just to make this blog look more sophisticated.]

The constraint file.

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {gpio_led[0]}]

set_property PACKAGE_PIN D7 [get_ports {gpio_led[0]}]

set_property PACKAGE_PIN F7 [get_ports {gpio_led[1]}]

set_property PACKAGE_PIN F6 [get_ports {gpio_led[2]}]

set_property PACKAGE_PIN A6 [get_ports {gpio_led[3]}]

set_property PACKAGE_PIN G6 [get_ports {gpio_led[4]}]

set_property PACKAGE_PIN E6 [get_ports {gpio_led[5]}]

set_property PACKAGE_PIN D6 [get_ports {gpio_led[6]}]

set_property PACKAGE_PIN C7 [get_ports {gpio_led[7]}]

Now, after this we just generate the bitstream and export it. And, we then make note of the two files that we need, namely. Then after starting a new Jupyter notebook within Ultra96v2, we can upload these files as shown in the image.

- Hardware handoff (.hwf)

- Bitstream (.bit)

In the Jupyter Notebook, we can run the following code.

from pynq import Overlay

from pynq.lib import AxiGPIO

import time

overlay = Overlay('u96_8bit_expynq.bit')

gpio_led = overlay.ip_dict['axi_gpio_0']

LED = AxiGPIO(gpio_led).channel1

LED[0:8].write(0)

while (1):

# 8-bit up counter

for i in range(255):

LED[0:8].write(i)

print(f"LED: {hex(i)}")

time.sleep(1)

# 8-bit down counter

for i in range(255, 0, -1):

LED[0:8].write(i)

print(f"LED: {hex(i)}")

time.sleep(1)

The end result would be as shown in the video below.

YouTube: https://youtu.be/T47WlpKiQ8Q