What is Path to Programmable 3

- An initiative program from Element14 to encourage the FPGA Enthusiast to offer structured FPGA-based SoC training.

- Encourages the challengers to Submit an idea of implementation.

- A Expert committee from Element14 Community will Finalize the challengers based on their initial abstracts.

- FPGA Platforms like Ultra96-V2 and MiniZed will be provided for the training free of cost.

- Challengers has to go through the trainings, Create the blogs for the trainings and can discuss in the forum.

- Based on the Trainings Blogs and the Final Build Project blogs, the winner will be announced

What led to this sequence of events

- Submitted my Abstract for the Path to Programmable 3

- Shortlisted and notified via email.

- Ultra96-V2 Kit sent from Element14.

- Installation of the Ubuntu and Vitis

- Software, Hardware and Peta Linux Training

- Handon Lab sessions

Board Received from Element14

Very Happy to receive these set of beautifully packed boards from Element14.

These Boards all the way traveled from Chicago, USA to Bangalore India.

The experience of Unboxing these boards is unique compared to unboxing a smartphone or a laptop.

1. BOX-1

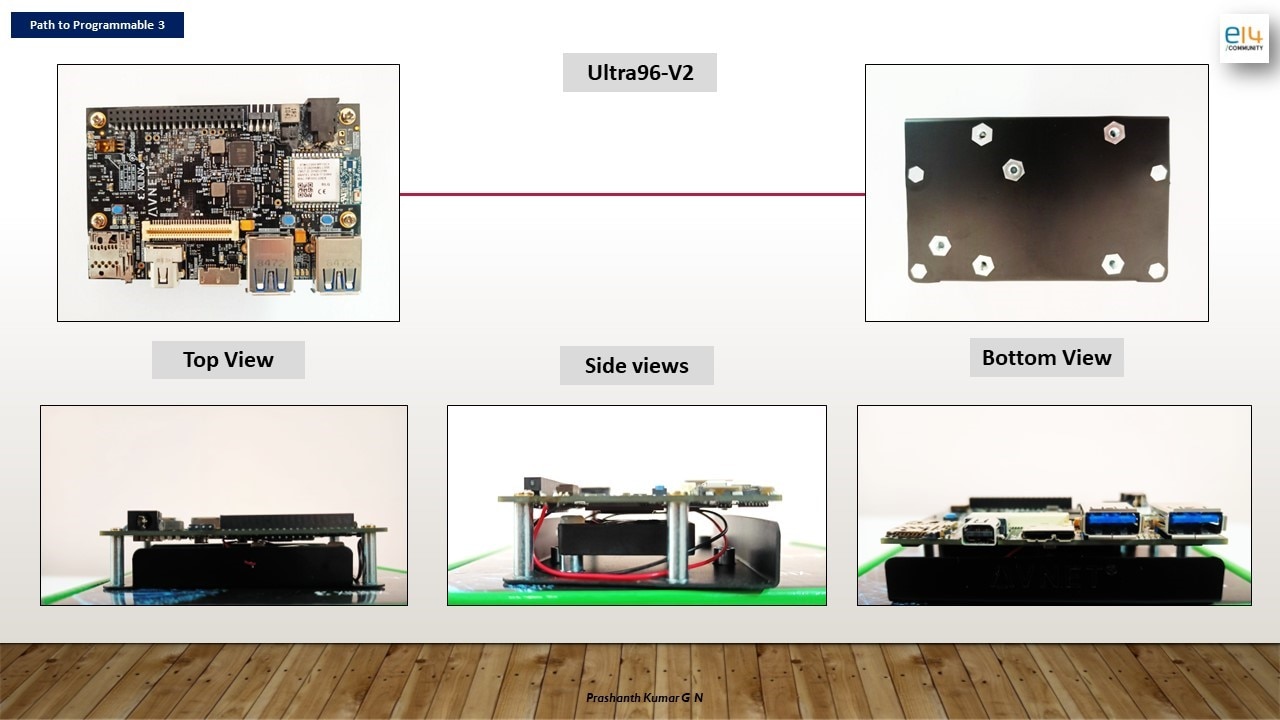

- Box-1 Contains Ultra96-V2 Single Board computer (SBC), 16GB micro-SD Card with Standard SD Adapter, Getting Started Note, A voucher from Xilinx.

- Ultra96-V2 features can be found in below link

I have tried to capture the board with different views. As a Hardware Engineer, I have done several photo-shoots of the board which I have designed.

Photo shoot of Electronic boards is a unique experience.

2. BOX-2

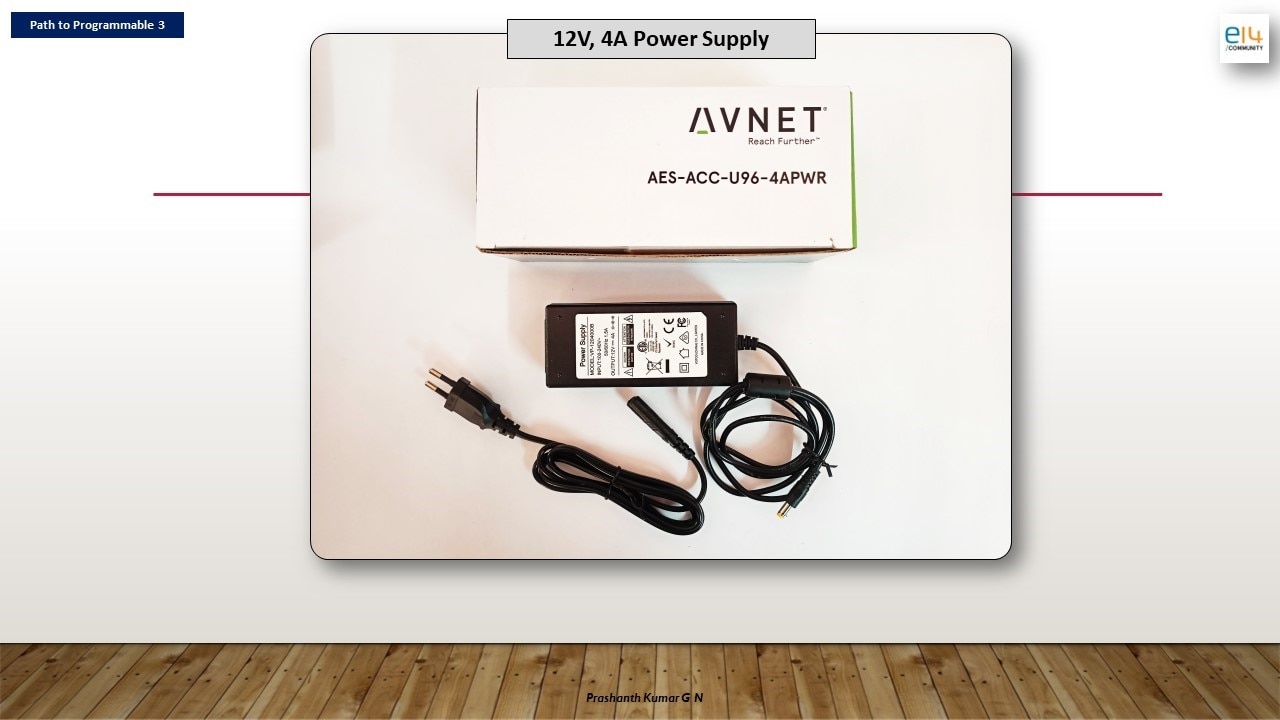

- Box-2 Contains Power Supply required for the Ultra96-V2

- DC 12V 4A is the output

- 100VAC to 240VAC 50/60 Hz Input Voltage, 1.5 A current

- Supplied with Four international plug adapters. We use European Standard Plug.

3. BOX-3

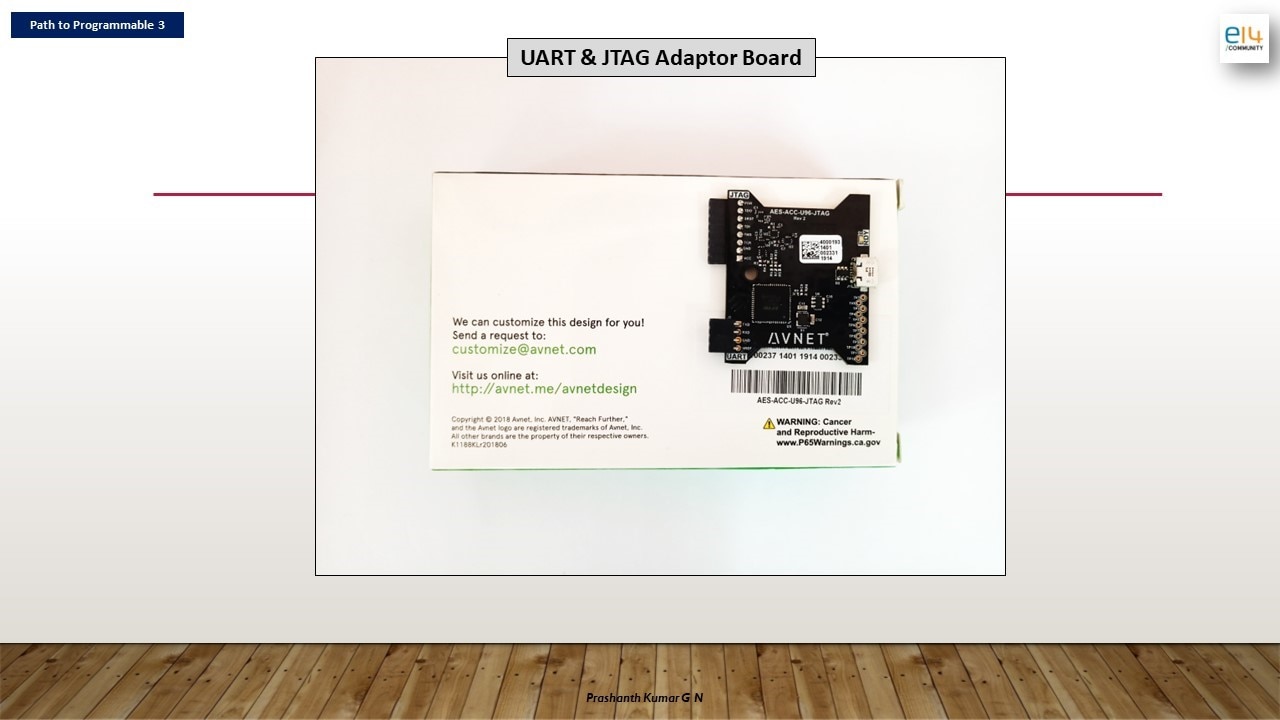

- Box-3 USB to UART and JTAG Adaptor Board with micro-USB port connectivity

- Inexpensive compared to Xilinx Platform Cable II

- Single FTDI FT2232 Chip which has Dual Channel supporting JTAG and UART

- Board contains a companion SPI Flash for FT2232 which loads the firmware/configuration to perform USB to JTAG and USB to UART Functions

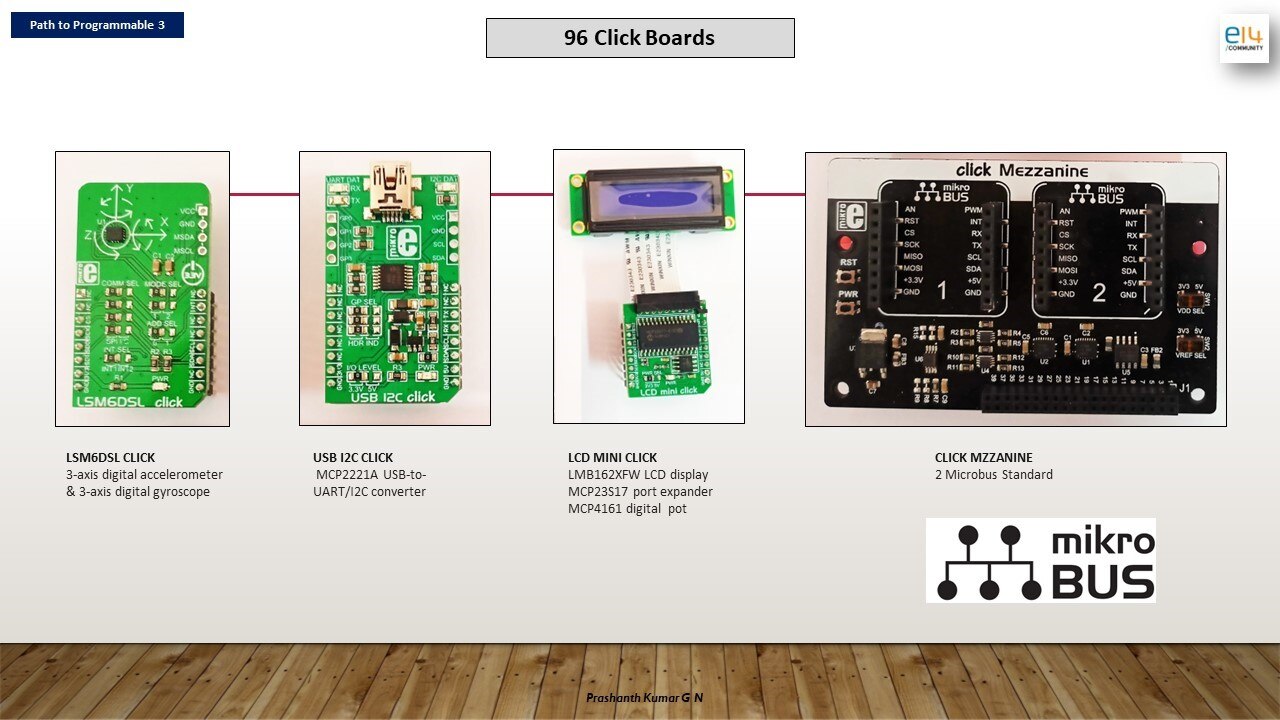

4. BOX4

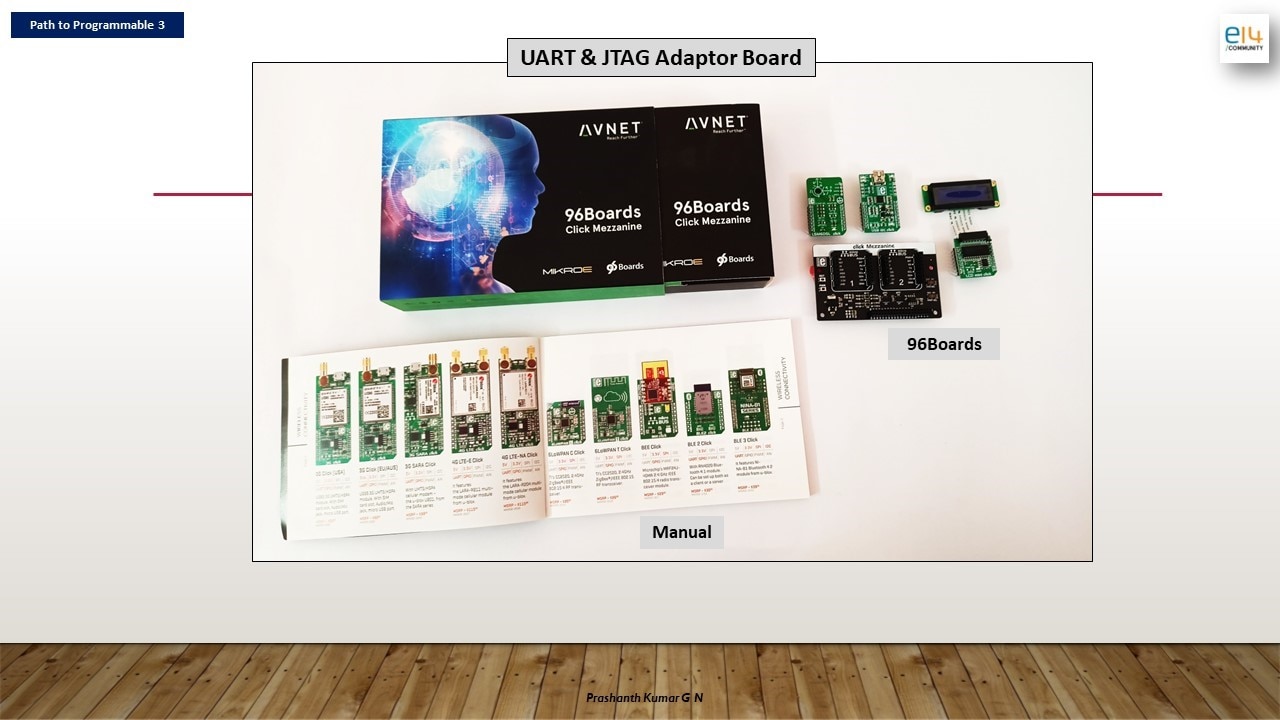

- Box 4 includes 96Boards Click Mezzanine - Which is a Daughter card for Ultra96-V2 SBC to Expand the IOs

- Contains 2 mikroBUS Standard Host Connectors

- three Click boards:

- MIKROE-1985, USB-UART Click - USB mini connector with FT232RL chipset

- MIKROE-2453, LCD Mini Click - An 16x2 LCD with he MCP23S17 port ex pander and the MCP4161 digital POT

- MIKROE-2731, LSM6DSL Clic - LSM6DSL high-performance 3-axis digital accelerometer and 3-axis digital gyroscope.

Getting Started with Training

(+) Avnet Boards Technical Training Courses - element14 Community

Recommended Order to Get Started with Training

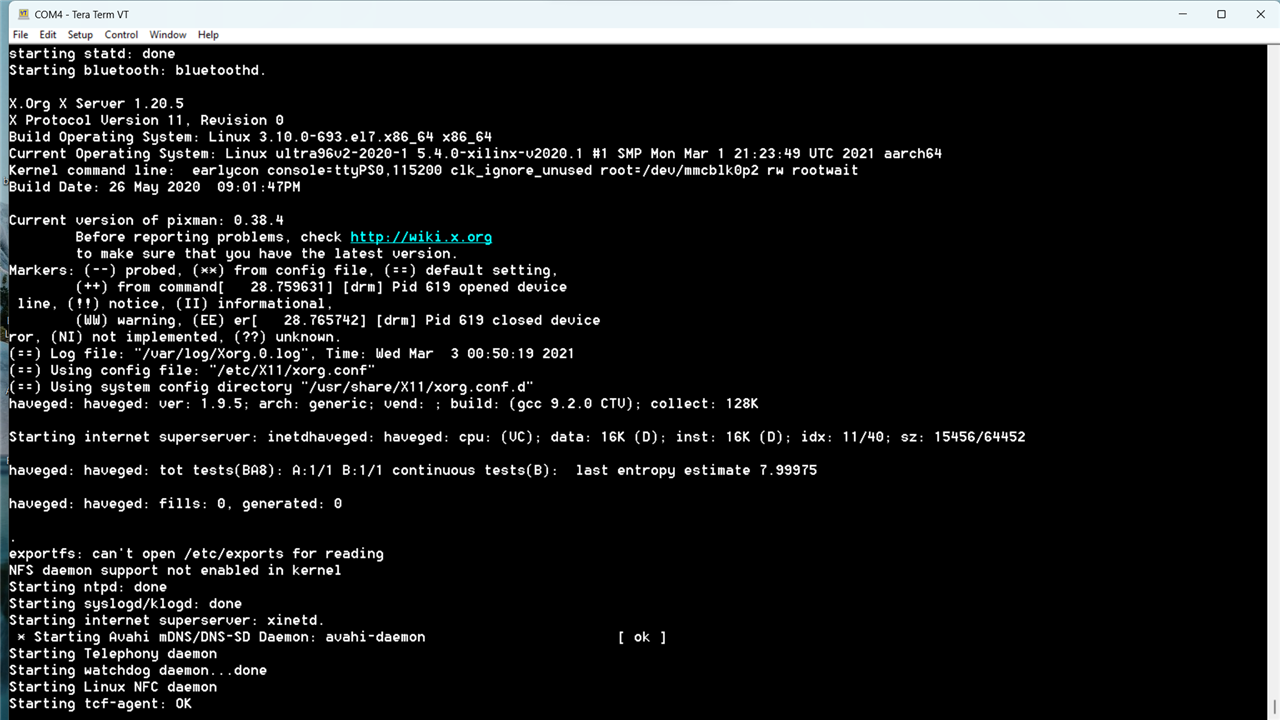

Ultra96-V2 SBC Booting

Please do provide your comments, Suggestions.

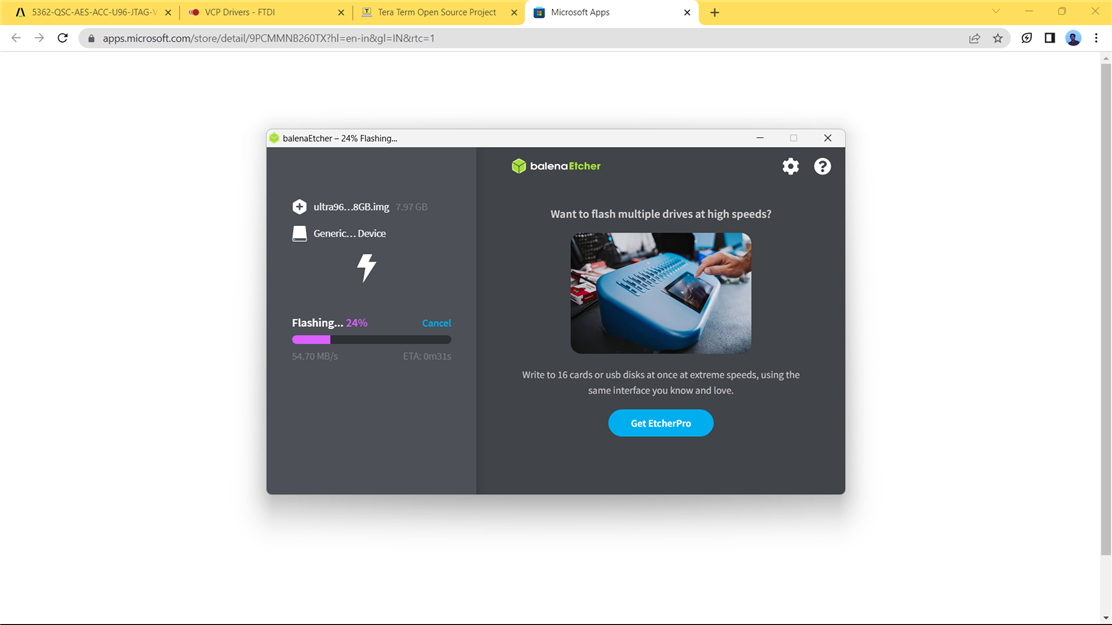

SD card Flashing

Tera term Snapshot

Log File : 0624.teratermlog.txt

Software Training

Lesson 1 : Ultra96-V2 Software Technical Training 2021.2: Lesson 1 - element14 Community

Summary of Lesson1

- What is the course is about

- How to Develop a Software using Xilinx Vitis 2021.2

- Vitis Design Flow

Lab 0 – Pre-Lab : Setting Up a Development Platform for Zynq MPSoC

Experiment 1 : Installation of Ubuntu

- The Lab Manual suggest using the Virtual Box within Windows OS itself, when we tried to install the same, the Virtual BOX very slow, Ubuntu loading was taking longer time to load the OS.

- Dropped the Idea of using Linux via virtual box and Switched to Dual Boot the PC with recommended Ubuntu 18.04 Version

- Drawbacks with Ubuntu 18.04 Version

- no Wi-Fi Driver Available

- No Touch Pad Driver

- Started to Use USB to Ethernet Adapter and Wired Mouse

- no Wi-Fi Driver Available

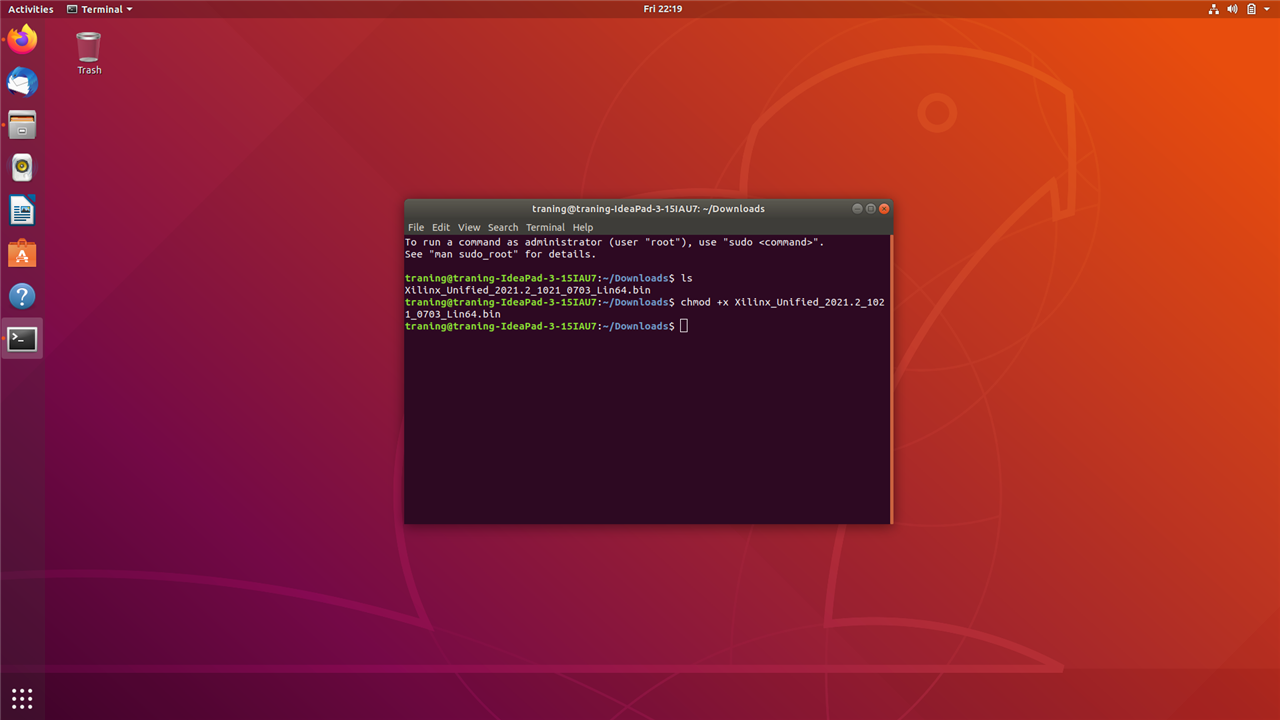

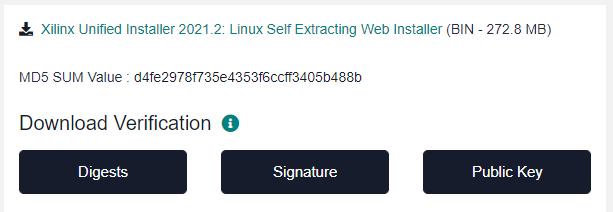

Experiment 2 : Installation of Xilinx Vitis and Vivaldo Suite

- Unlike Windows Double click to install, Command line method was new to me, Started using linux..

| {gallery}My Gallery Title |

|---|

|

chmod +x Xilinx_Unified_2021.2_1021_0703_Lin64.bin Command to Enable Permission to Run the Binary File |

|

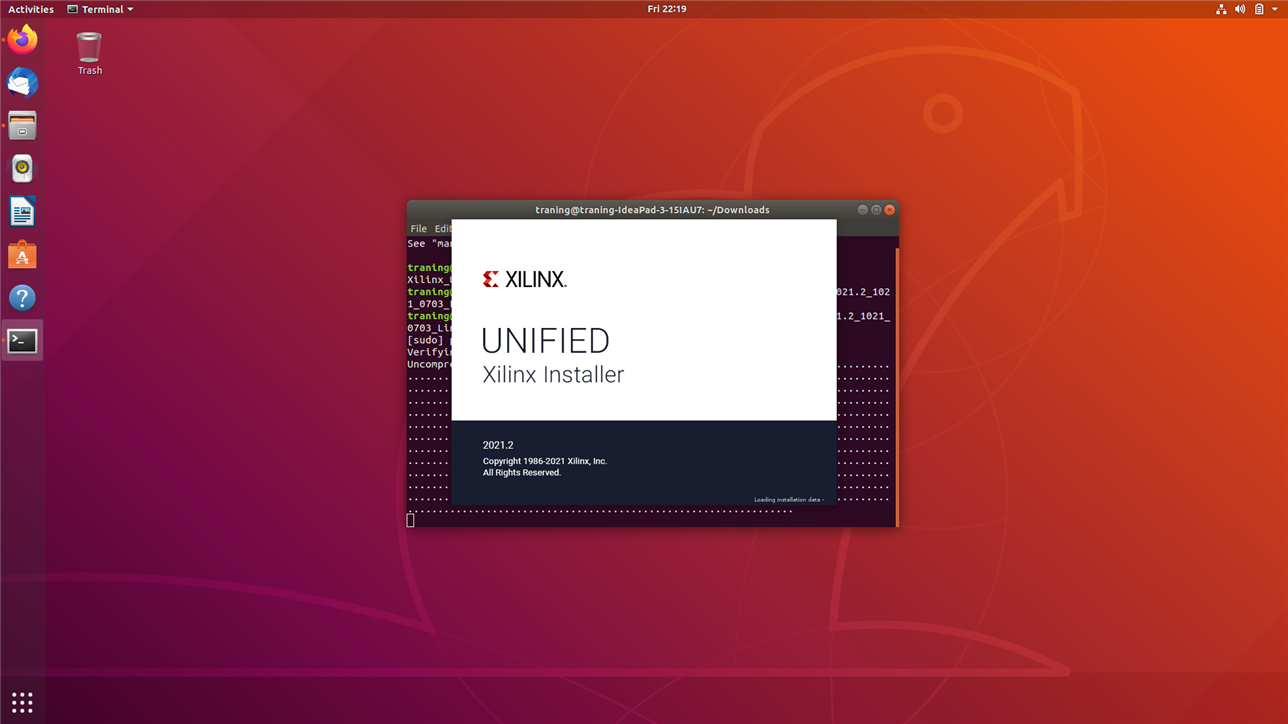

sudo ./Xilinx_Unified_2021.2_1021_0703_Lin64.bin Running the Xilinx Installer Binary File |

|

Installation Window opens. |

|

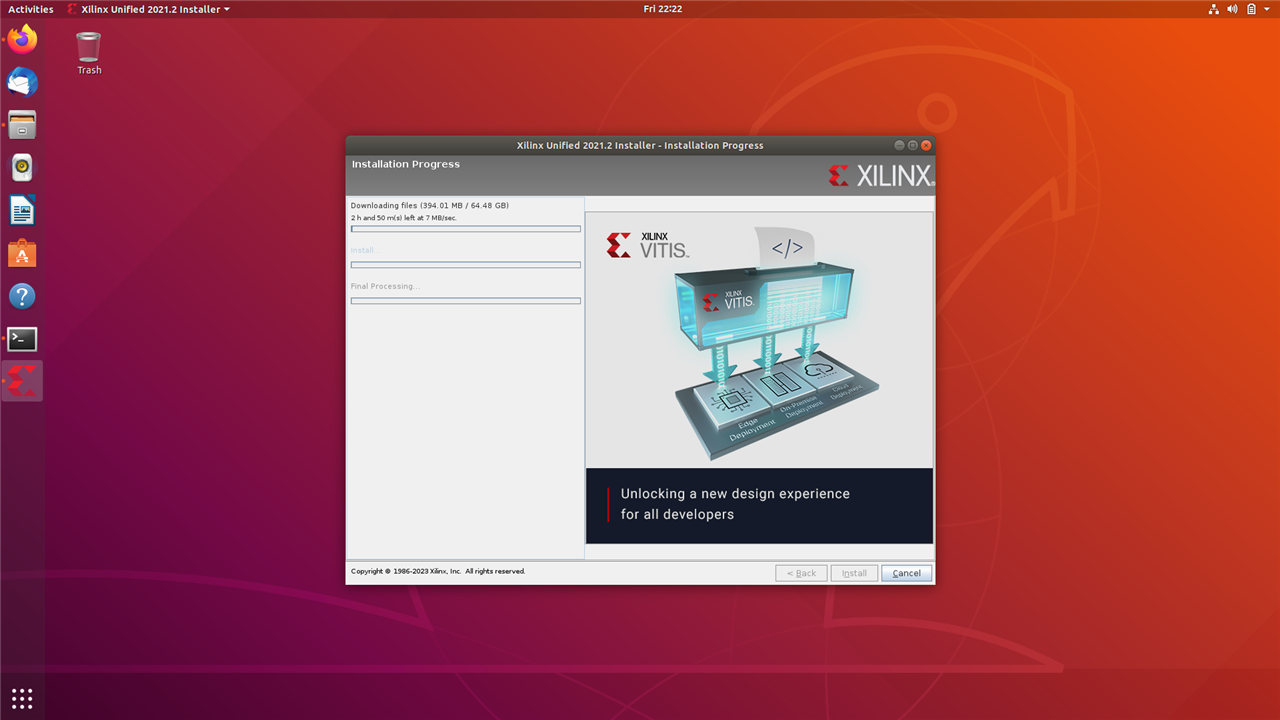

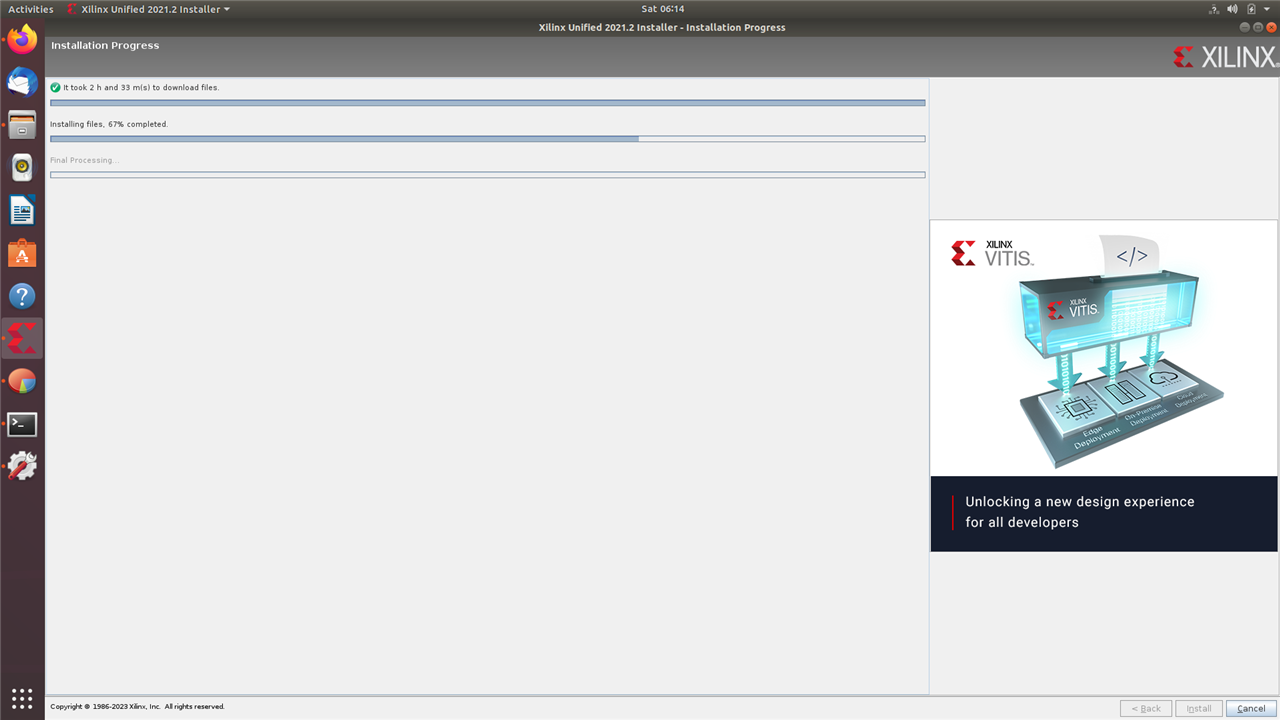

After Several Attempts of downloading the Files from the Server, finally completed the Downloading and Installation |

Experiment 3: Setting Up Avnet Technical Training Course Lab Files

- Mismatch in the manual observed regarding the ZynqSW_2021_1_student.zip Files where as the Lab Files and Lab Solutions naming and File Types were Different

- Unzipped all Files and Placed in the Folder

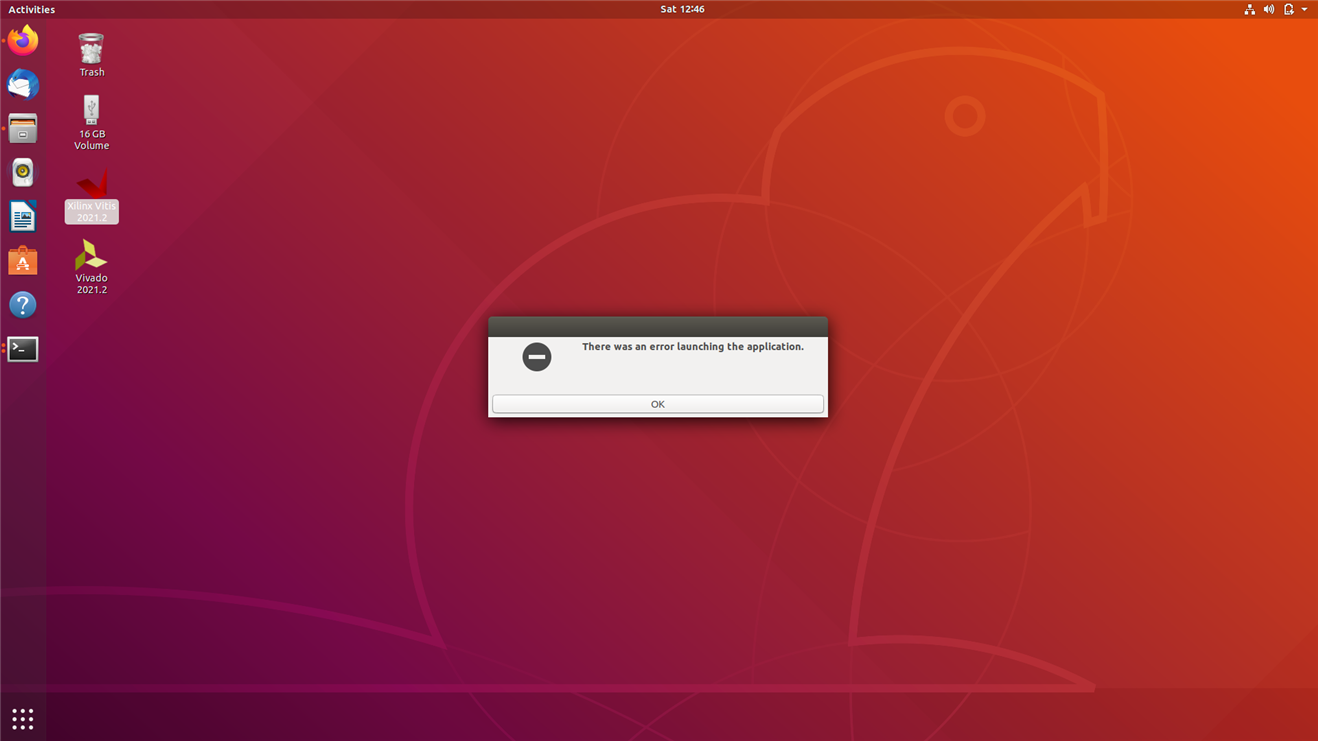

Experiment 4 : Finish setting up Xilinx Vivaldo and Vitis

- Followed the Lab manual to create the Scrip that opens the Vivado and the Viitis

- We encountered problem in creating Desktop Link for Vivado and Vitis: ERROR OCCURED

-

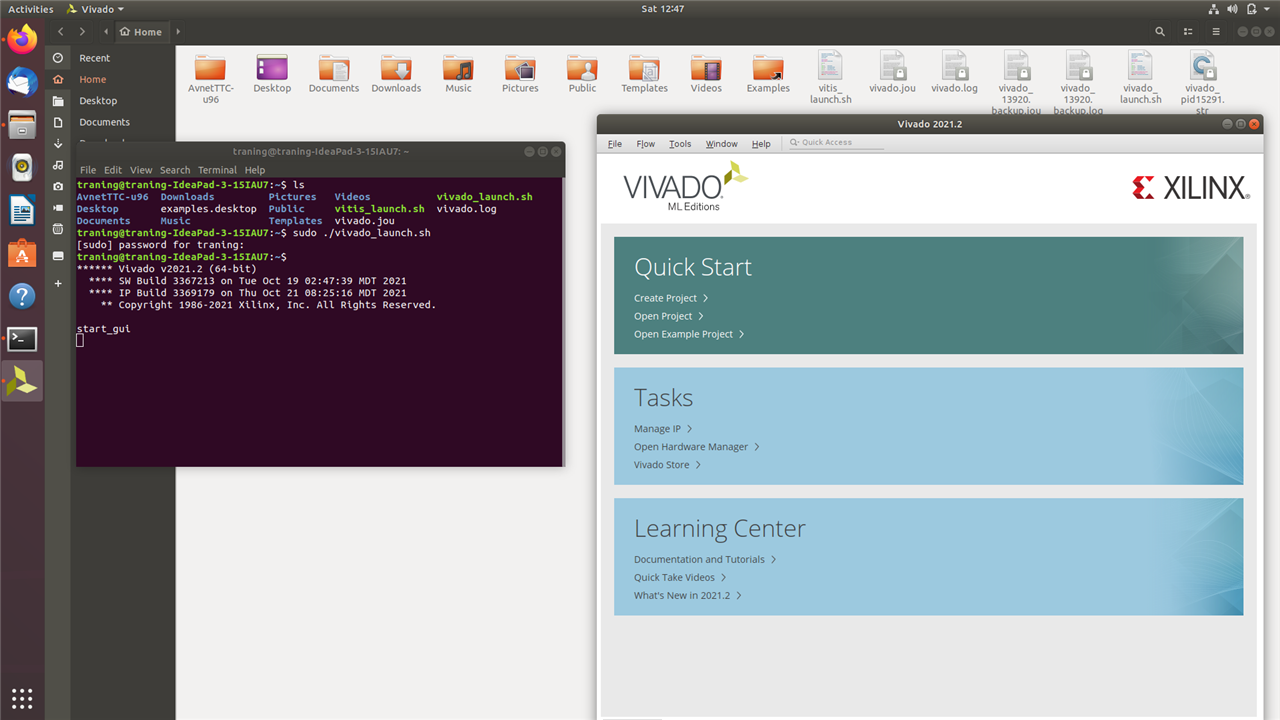

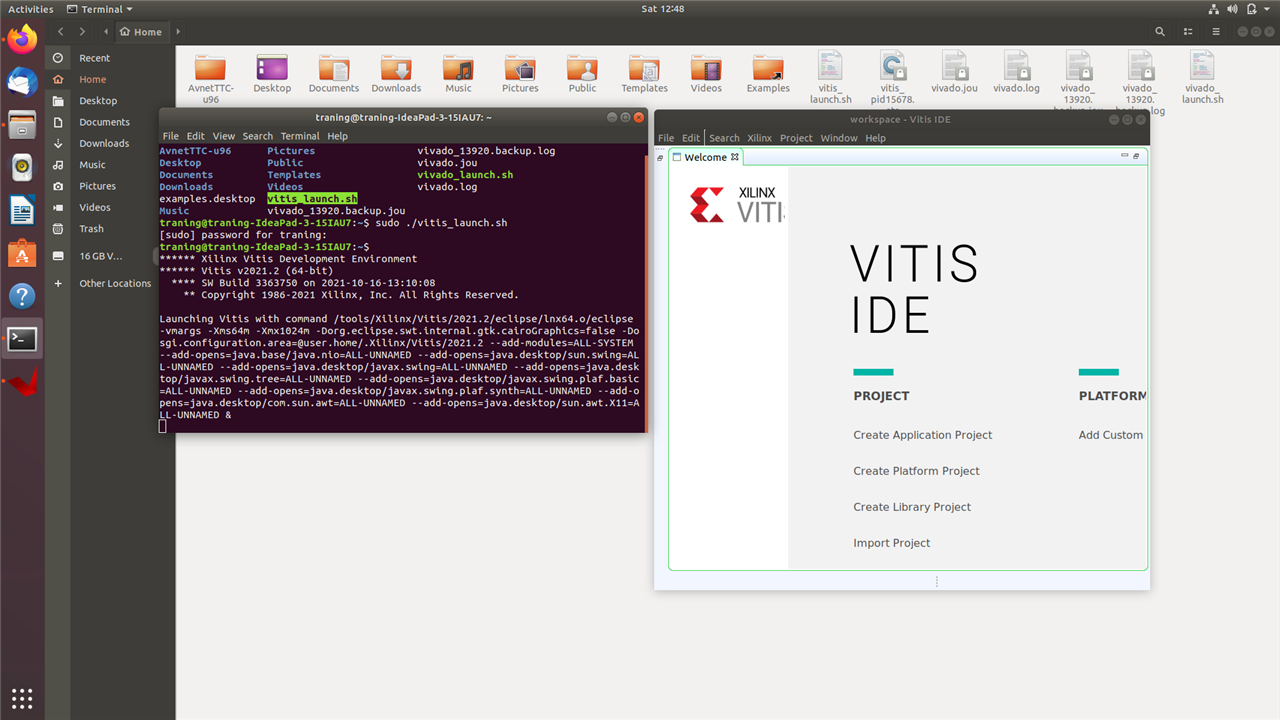

- Figured out an Alternative solution to Launch the Vivado and the Vitis Applications

- Launching Vivado : By running Script

- Launching Vitis

Lesson 2 : Ultra96-V2 Software Technical Training 2021.2: Lesson 2 - element14 Community

Summary of Lesson2

- Zynq MPSOC Architecture

- What is PS and PL : With Block Diagram

- Processing System - ARM A53 and R5, DDR, Bulit in Peripherals

- Programmable Logic - Logic elements, AXI Bus, Memory, Clocking, Integrated IPs

- Hardware Designer and Software Developer Persecutive of Design

- PS and PL features : ARM, GPU, logic cells, BRAM, etc

- Outputs from Vivaldo : XML, BMM, .bit BitStram

- Architecture of Ultra93-V2 hardware Platform

- UGC1085 - Zynq TRM

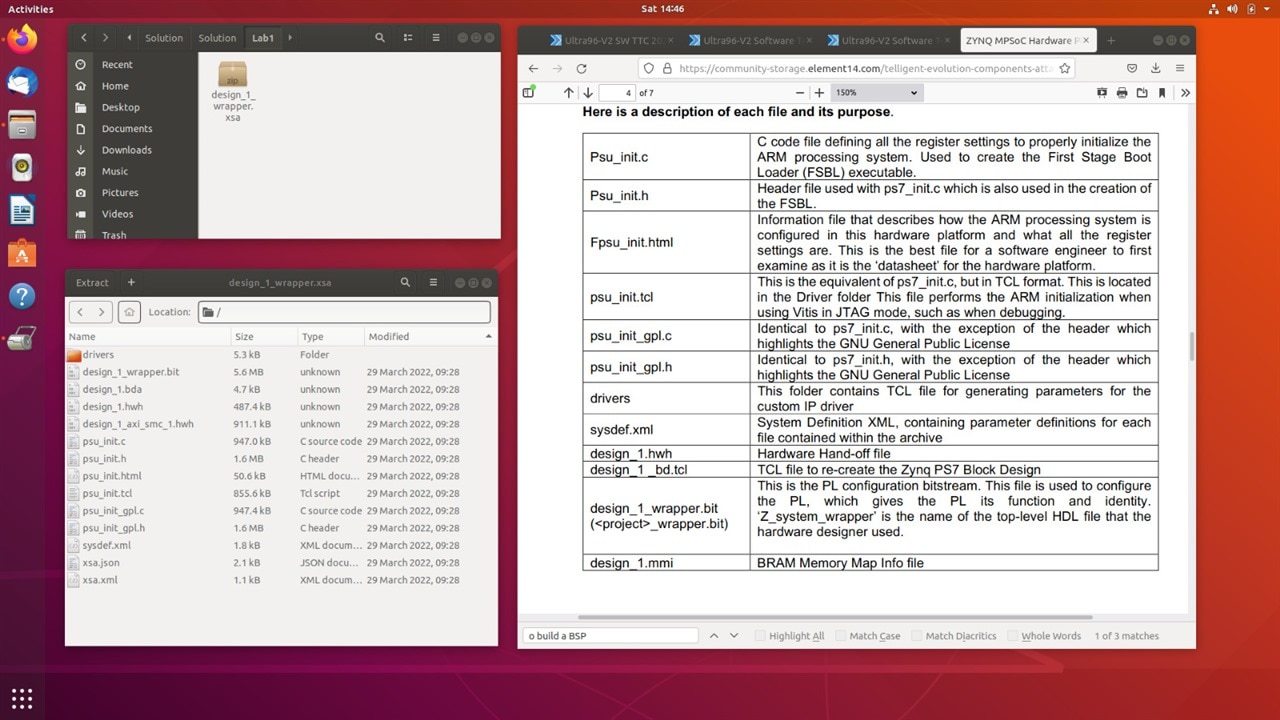

Lab 1: Explore a Zynq MPSoC Hardware Platform

- Exploring the Zynq hardware platform archive File

Lesson 3 : Ultra96-V2 Software Technical Training 2021.2: Lesson 3

Summary of Lesson3

- Vitis Application Development Flow

- Automatic BSP Generation

- Hardware Software Cross probe

- GNU, Xinx Tool chains

- How the tool look like : Eclipse : Workbench and Workspace

Lab 2: Importing the Hardware Platform into Vitis

Experiment 1: Workspace and Hardware Platform

Create a platform project from existing XSA File

Experiment 2: Examine the Hardware Platform

Lesson 4 : Ultra96-V2 Software Technical Training 2021.2: Lesson 4

Summary of Lesson 4

- Xilinx Provides Device Drivers

- Introduction to BSP

- BSP -Collection of Parameterized Driver for Specific MPU System

- UART Device Driver example : HW Instance - Associated Driver

- GCC Tool-chain - libgcc.a

- UG643 - OS and Library Documentation

- What is BSP

- A board support package (BSP) is a collection of libraries and drivers that will form the lowest layer of the application software stack.

- The software applications must link against or run on top of a given software platform using the application programming interfaces that it provides.

- Therefore, before one can create and use software applications in Vitis, you must create a board support package

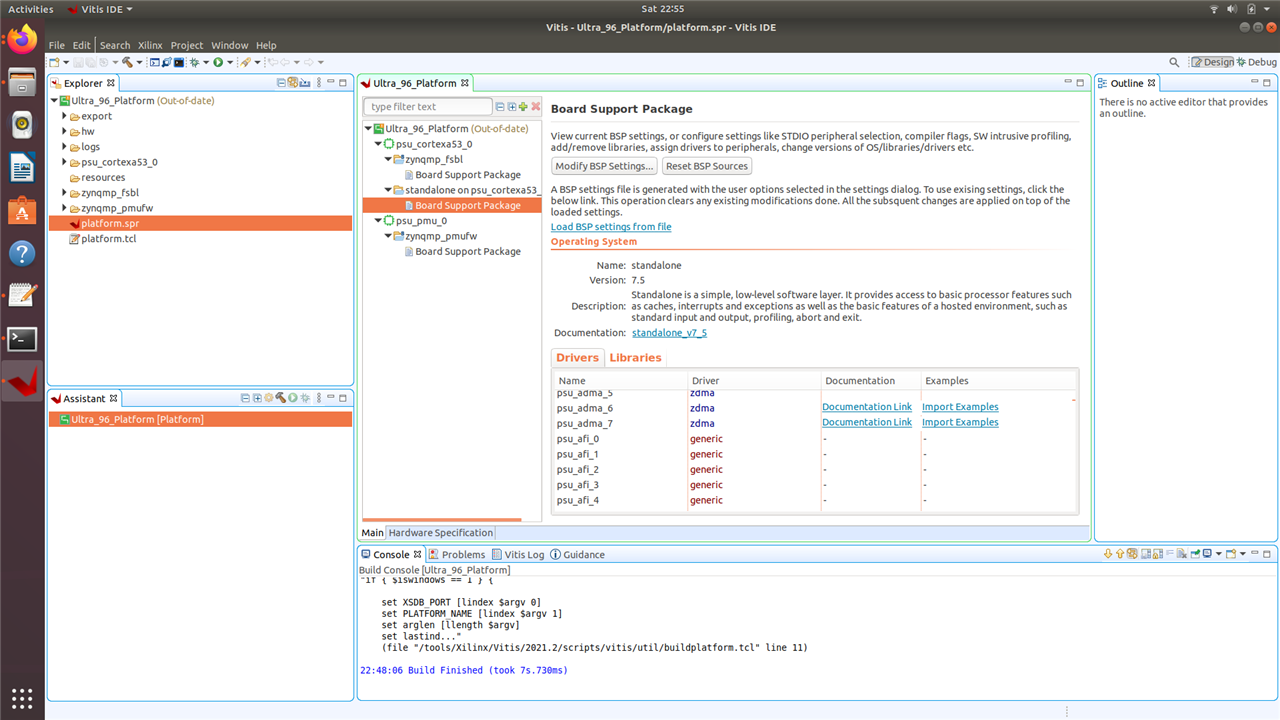

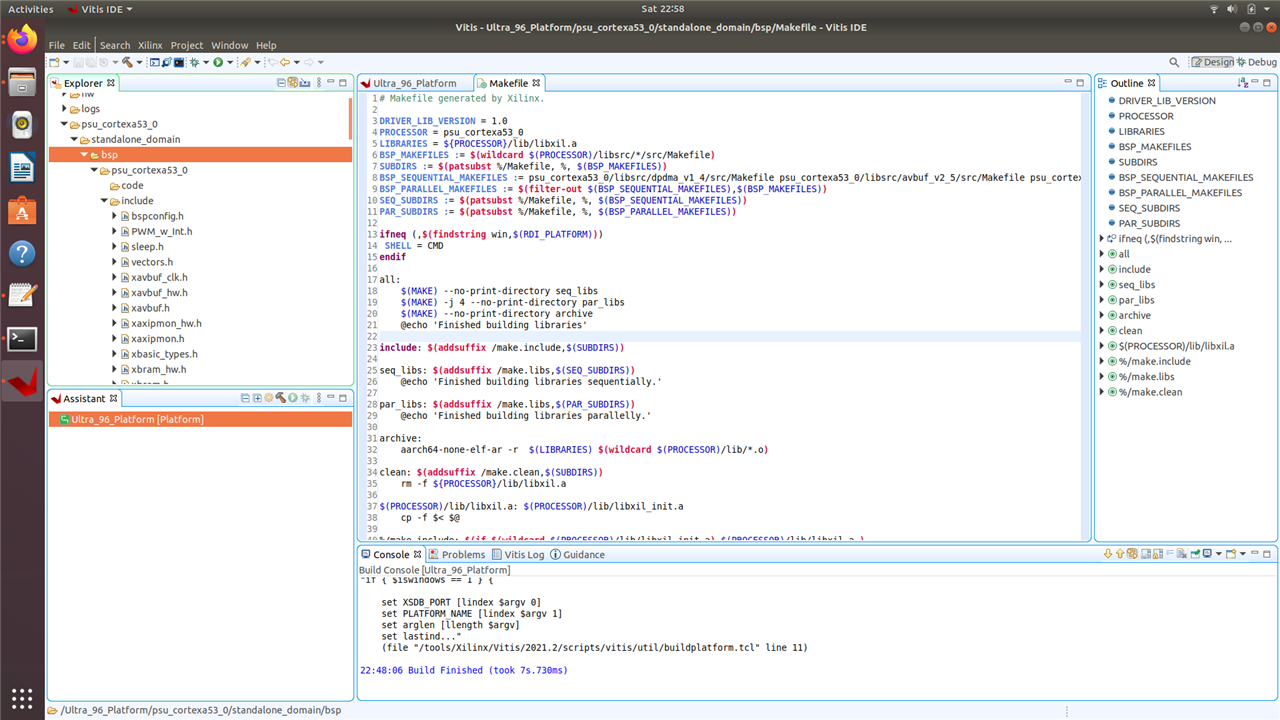

Lab 3 : Bare Metal Board Support Package

What is Bare Metal

Bare metal programming is a low-level type of programming that is hardcoded to a system at the hardware level and operates without an abstraction layer or operating system (OS)

Experiment 1: Generate the Standalone Board Support Package

Experiment 2: Explore the BSP

Experiment 3: Library Generator (LibGen)

Lesson 5 : Ultra96-V2 Software Technical Training 2021.2: Lesson 5

Summary of Lesson5

- Example Code for Every Peripherals Available

- Sample Applications includes

- Hello World : through PS UART

- IwIP echo server : Sample Output via Ethernet Stack

- Memory test

- Peripheral Test

- Zynq MPSoC First Stage Boot Loader : FSBL

- Link Script Generator - Where Application Running from : DRAM, OCM, BRAM

Lab 4 – Develop a Zynq Software Application

Experiment 1: Develop an Application with Example Code

Experiment 2: Add Peripheral Test

Experiment 3: Add and Edit Memory Test

Experiment 4: Add and Edit Memory Test Full Range

And the Learning with Element14 Continues.....

Thanks & Regards

Prashanth Kumar G N