Software Training

Lesson 6: Connecting Hardware and Debugging

Summary of Lesson6

- Ultra96 V2 Hardware Explanation

- How to Debug the application using RUN configuration

- Setup for Processor initialization, RESET, Download Bit steam, Terminal and Profiling

Lab 5– Connecting Vitis to Hardware

Experiment 1: Setup Hardware and Download Bitstream

| {gallery}Lab 5 |

|---|

|

|

|

|

|

|

Debug an Application

| {gallery}Debug an Application |

|---|

|

|

|

|

|

Lesson 7: First Stage Boot Loader

Summary for Lesson 7

- First Stage Boot loader (FSBL) for Zynq UltraScale+ MPSoC configures the FPGA with hardware bitstream (if it exists) and loads the OS Image or Standalone Image

- Standalone PL configuration without PS is not possible

- configuration of FSBL by external host is by JTAG mode

- Secure and non Secure Boot Modes

- Can boot from 4 Master Boot Devices : QSPI, NAND,eMMC and SD

- Slave Boot Devices : JTAG and USB2.0

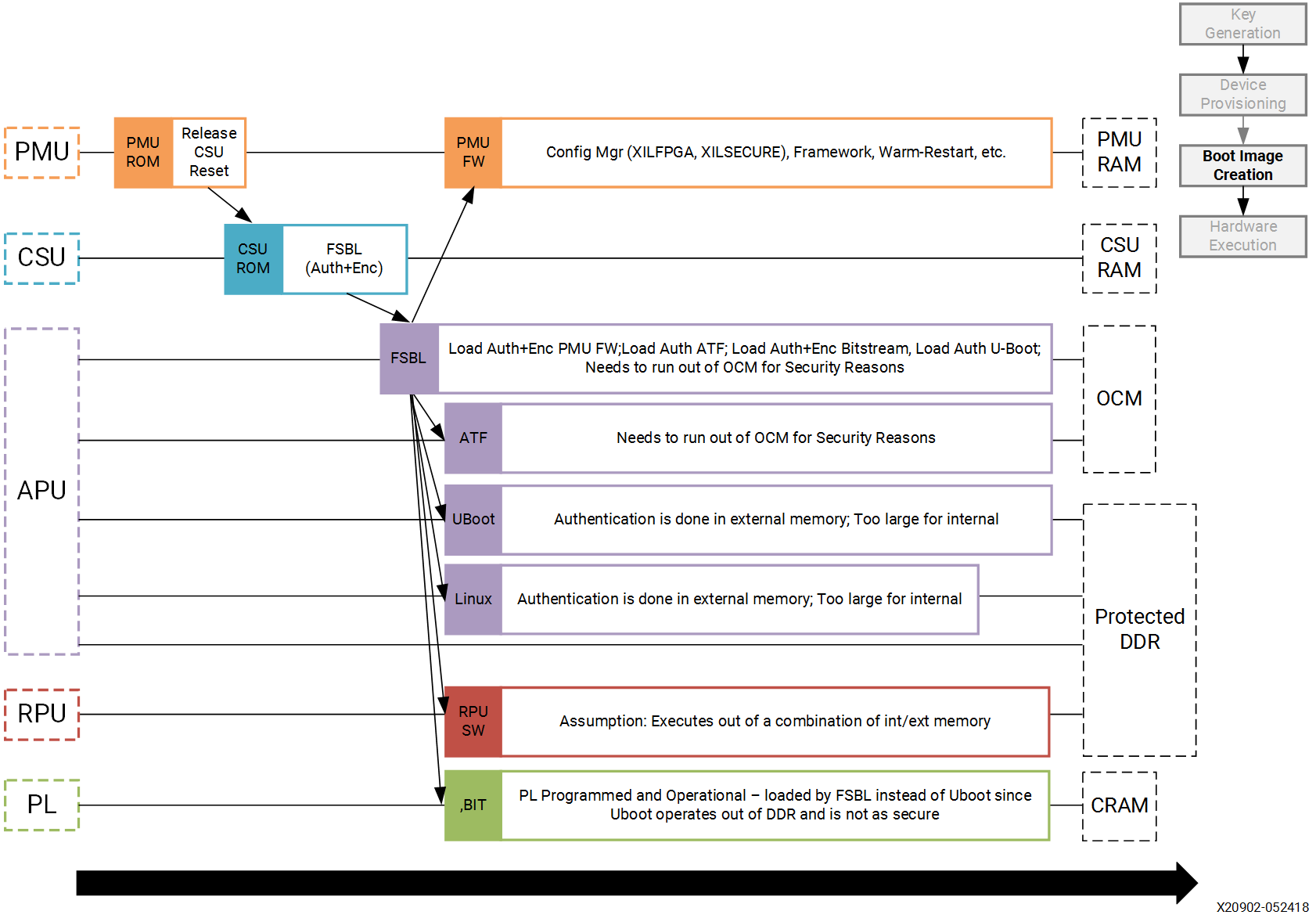

- Zynq Ultrscale+ Boot Flow

What does FSBL Does

- Initialize Processing system

- Initialize PLL, External memory and MIO

- configure PL with bitsream

- Provide option for Secure Boot Modes

- Execute Application Code

Boot Flow Diagram

PMU Boot

- configuration both PMU and CSU

- Validates PLL clocks

- Clear PSU and CSU RAM

- Validate LPD AUX Unit

CSU Boot

- initiate on chip memory.

- Determine boot mode

- Loads FSBL on OCM

- Execution by R5 or A53

- CSU loads PMU;s Firmware

Stage 2 Boot

- Loads Uboot and Runs DDR

- Loads OS and Kernal Images

- OS is loaded from NAND/QSPI/USB/Ethernet/Sd

LAB6 : First Stage Boot Loader (FSBL)

| {gallery}My Gallery Title |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- using Viti's Create Boot Image Wizard.

- File order should be: First Stage boot loader, Bitstream and Application: File order matters.

- To Flash QSPI, we can use Vitis Program Flash memory utility Wizard

- Multiple non volatile types

- .BIN and .MCS Format Files

- Programming at Offset

- Erase check verify option

ULTRA96-V2 Does not have QSPI

LAB7 : Boot from SD

| {gallery}SD boot |

|---|

|

|

|

|

|

Lesson 9: Vitis Project Management

- Walk through on the VITIS IDE

- Store the repositions: Include custom Files

LAB 8 : Explore Workspace

| {gallery}Explore Vitis |

|---|

|

|

|

|

|

|

|

Summary for Lesson 10

Interrupt means some interface or peripheral needs an Immediate Response or attension

Hardware Interrupts

- Asynchronous changes in Hardware

- Generating outside the processor

- IOndiactes peripherals needs an attention immediately.

Software Interrupts

- Synchronous event in software needs for a change in execution.

- Also called an Exception.

Lab 09 : Interrupts

| {gallery}My Gallery Title |

|---|

|

|

|

Lesson 11: AMD Xilinx Libraries

- System allows range of Different Libraries

- Power management

- Single FAT Generic File System

- TCP IP Support - Open Source

- Secure Programming eFUSE

- In System Serial programming

- Libraries can be added within BSP Settings

LAB 10 : AMD Xilinx Libraries

Learning with Element14 Continues

Regards

Prashanth Kumar G N