In this blog, we will be working on the process of printing messages to the serial port on the Ultra96-V2 development board. Serial communication is a fundamental method for interacting with embedded systems, allowing you to monitor and debug your FPGA designs. We'll be able to send messages from your FPGA design to a terminal or serial monitor connected to the Ultra96-V2 board.

Launch Xilinx Vivado and open your existing FPGA design project for the Ultra96-V2 board. If you haven't created a project yet, complete the necessary steps to create a new project and add your design files.

| {gallery}Creating Vivado Project |

|---|

|

|

|

|

|

|

|

|

|

Open the ZynqDesign project and open the Block design, design_1.bd.

Double click on the Zynq ultrascale+ MPSoC to customize IP. We will be configure the Zynq MpSoC step by step as shown below.

| {gallery}Configuring Zynq MpSoC |

|---|

|

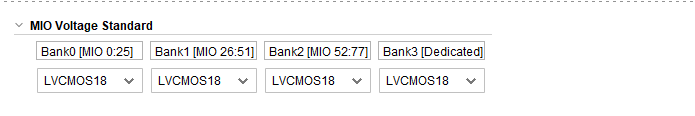

Set the all bank voltages to LVCMOS 1.8V |

|

Enable UART 1 and set the I/O to MIO0 .. 1 |

|

Check the "Switch to Advanced Mode" and set UART1 baud rate to 115200. |

To configure the memory and clocks for Zynq MPSoC, Click on the Clock Configuration.

| {gallery}Configuring Memory & Clocks |

|---|

Verify the input clock frequency - 33.333 MHz |

|

Verify the following in the output clocks. ACPU frequency - 1200 MHz CPU R5 frequency - 500 MHz |

|

Disable the PS-PL reset by unchecking the Fabric Reset Enable. |

|

Enable the DDR Controller and switch the memory type to LPDDR4. |

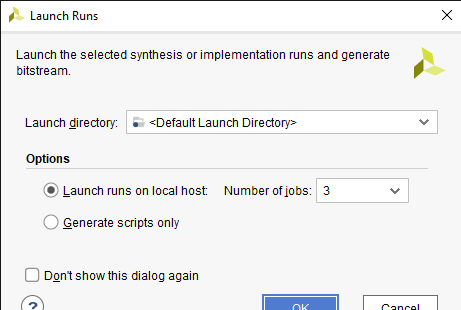

Proceed to implement the design by clicking on "Run Implementation" in Vivado. Once implementation is successful, generate the bitstream by clicking on "Generate Bitstream. Click Next in the Export Hardware Platform, on the next page check the Include bitstream box and click OK.

| {gallery}Exporting Hardware |

|---|

|

|

|

Creating Vitis Project

Create Platform Project by selecting File → New → Platform Project. Name the platform project as “Ultra96_Platform”.

Select the .xsa file generated in the previous step. This will create a new platform from hardware using the design_1_wrapper.xsa file.

| {gallery}My Gallery Title |

|---|

|

|

|

|

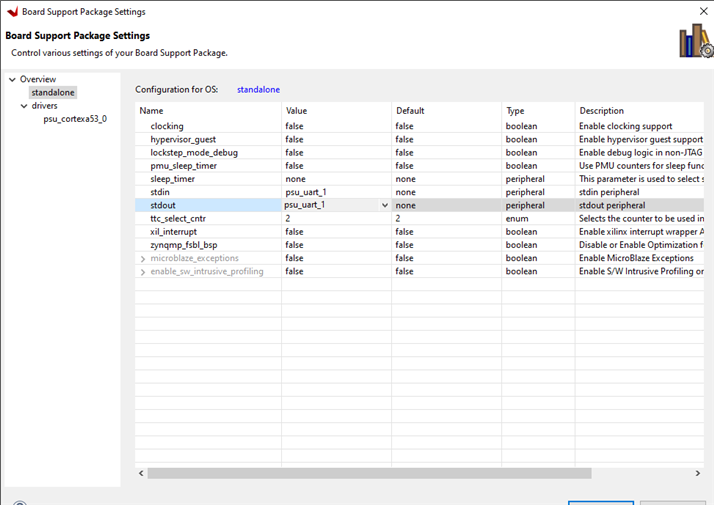

Click Modify BSP Settings on the standalone on psu_cortexa53_0. Click standalone in the Board Support Package window. Make sure that stdin and stdout are set to the psu_uart_1 peripheral.

Right Click on the Ultra_96_Platform and select build the platform.

How let's create a new application project by selecting File → New → Application Project. Make sure that the ultra96_platform is selected. I've named the Application Project as “HelloWorld". Select Hello World from the Available Templates field. Click Finish.

| {gallery}Creating Application Project on Vitis |

|---|

|

|

Right-click on the HelloWorld Application and select Build. Right-click on the application and select Run As → Launch Hardware to program the FPGA.

| {gallery}Programming FPGA |

|---|

|

|

|

|

Connect the USB-to-UART cable to the JTAG UART connector on the Ultra96-V2 board. The other end of the cable should be connected to your computer.

Open a terminal or serial monitor program on your computer. Configure the settings to match the UART communication parameters set in your FPGA design. Once the FPGA design is running on the Ultra96-V2 board, your messages will be sent to the serial monitor. You should see the messages displayed on the terminal or serial monitor.

We have successfully implemented serial communication and printed messages from your FPGA design on the Ultra96-V2 board to a terminal or serial monitor. Feel free to experiment further by sending different messages and expanding the functionality of your FPGA design using the UART module.

.