Hi,

as from subj, working with AUBoard15P with Vivado 2025.1, seeing the following issues:

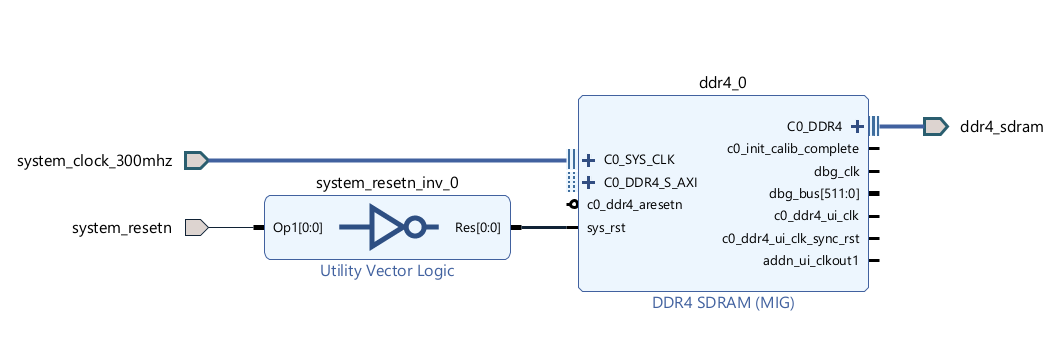

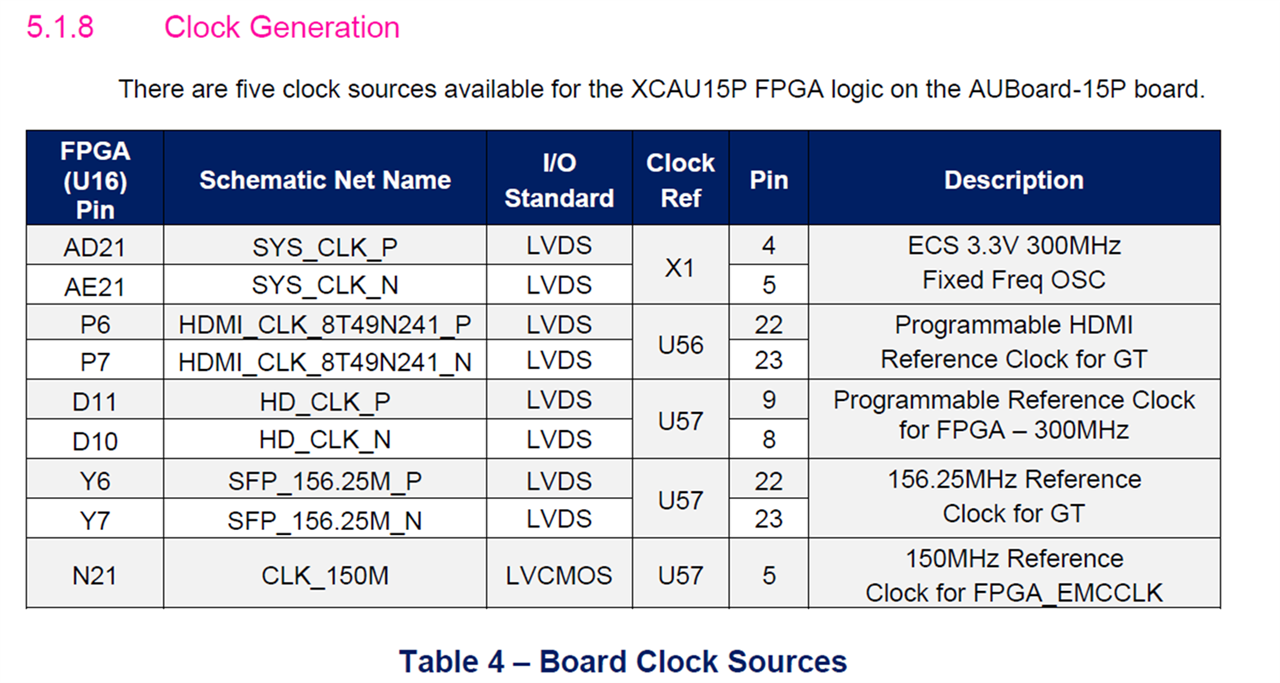

1) in IP Integrator Board tab the AUBoard peripherals + reset are present, but the 300 MHz system clock is missing, and trials to insert it form the Vivado Automation (from "Connection Automation" or from the GUI of Clocking Wizard) also fails, these last two case gives the error:

ERROR: [Common 17-69] Command failed: Failed to get scope property. Unknown property 'VLNV'

Manually deifning this clock and manually constraining it in xdc of course owrks, but the question is about the board files and the automation not working: is this a bug of the board file or not? Any workaround about it?

2) By updating the Vivado Board Catalog from the Refresh button, the AUBoard is not present - at least for my installation, where for example the Avnet ZUBoard is correctly present - solution was to manually install the boar file under ~/.Xilinx/Vivado/2025.1/xhub/board_store/xilinx_board_store/XilinxBoardStore/Vivado/2025.1/boards/Avnet

But any clue or better workaround why the Refresh button does not add the AUBoard?

Thaks in advance