Hi,

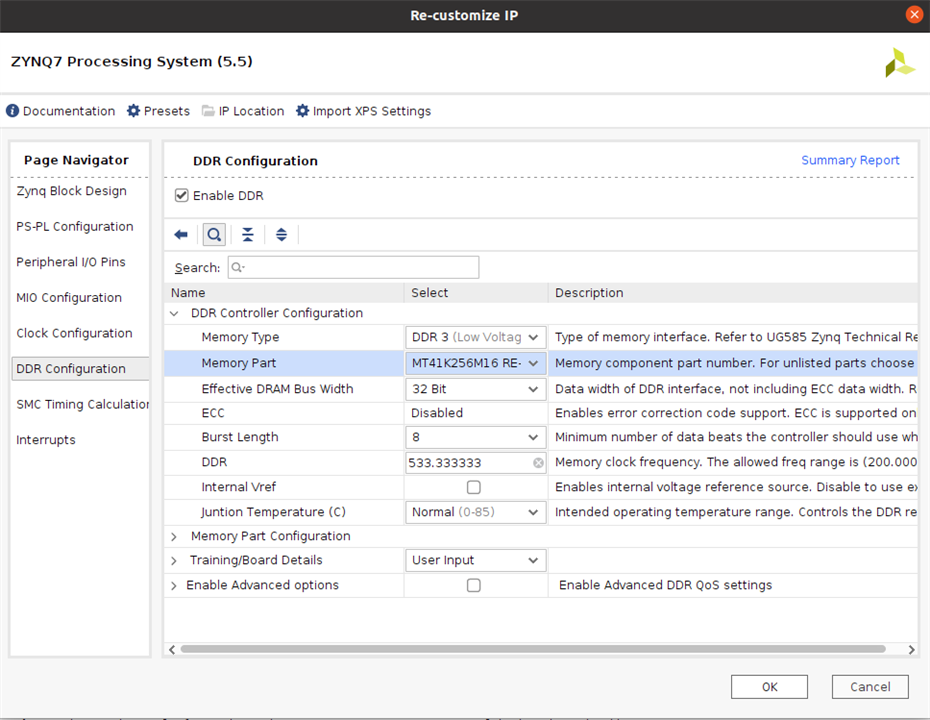

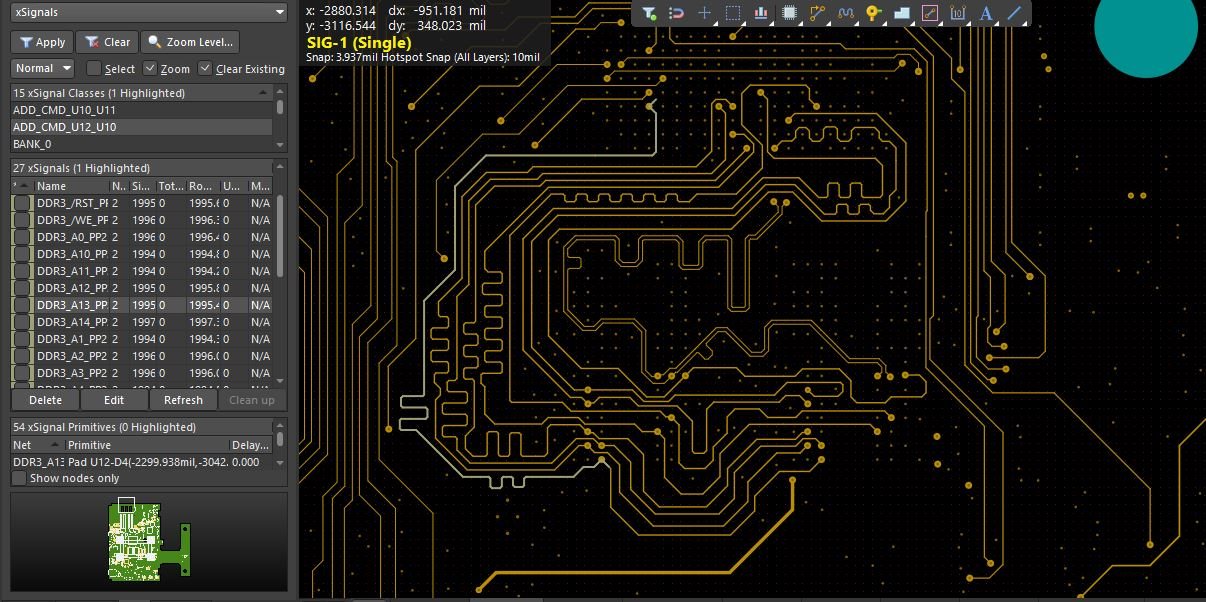

we are facing the issue while booting up with 533MHz operating speed of DDR3L.

Processor Part number : XC7Z010-2CLG400I

DDR3L Part number : MT41K256M16TW-107 AUT:P

Case 1: we have configured DDR3L operating speed to 533.333MHz in Vivado and build the project same as Pico Zed board ( Pico Zed board operating frequency is 533.333MHz)

Observation: only 3 lines were printed after that there is no progress after this lines

U-Boot 2022.01-00194-gb31476685d (Sep 20 2022 - 06:35:33 +0000)

CPU: Zynq 7z010

Silicon: v3.1

DRAM: ECC disabled 1 GiB

Case 2: configured the DDR3L operating frequency to 303MHz in Vivado

Observation: Board is booted up and no errors found.

We required to operate with 533.333MHz i request any suggestion can be helpful to resolve my issue.

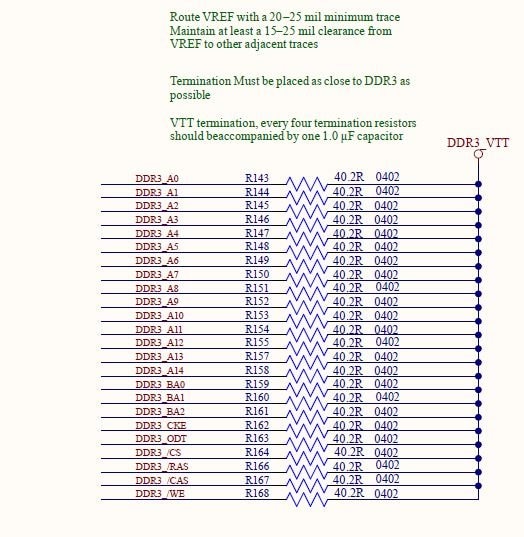

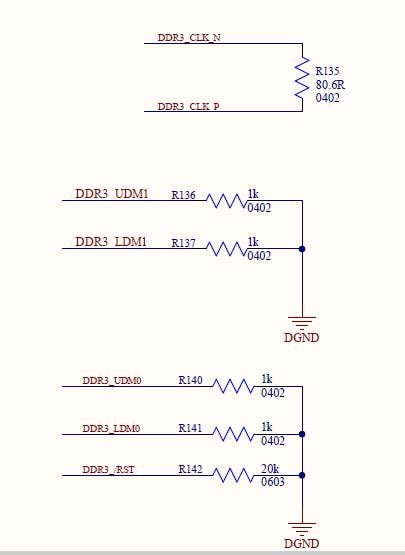

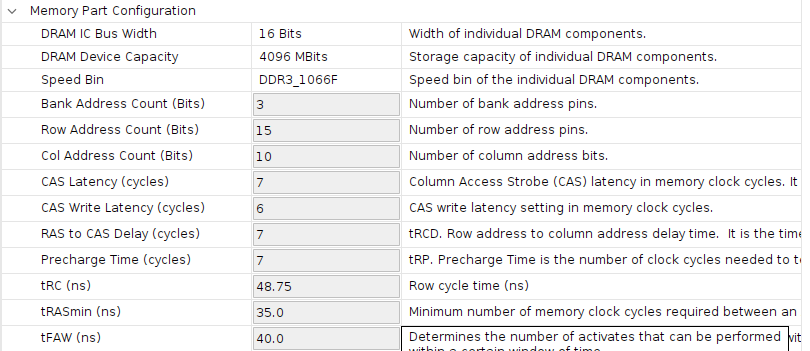

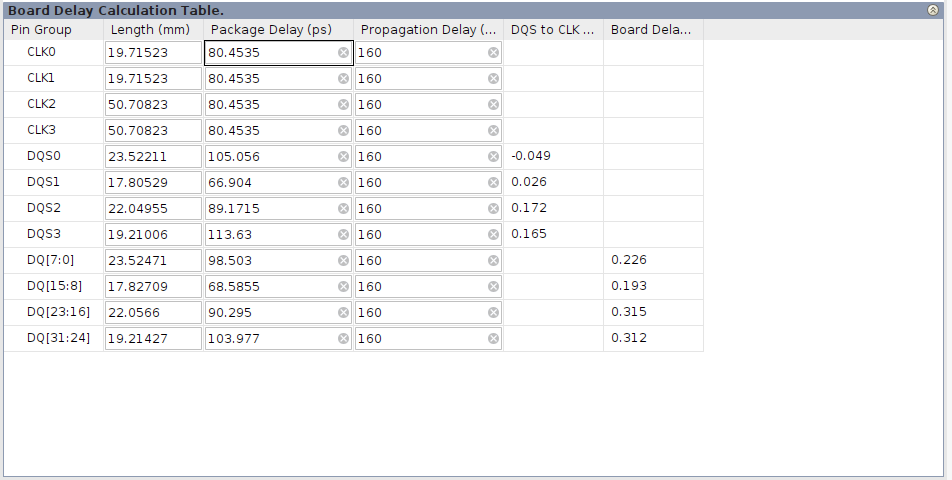

Let me know if we need to change the DDR timings.

Thanks in advance

I

I