Does the Xilinx part on the board wait for the entire boot load to finish before it starts running or does it start right after BIT file is loaded?

Does the Xilinx part on the board wait for the entire boot load to finish before it starts running or does it start right after BIT file is loaded?

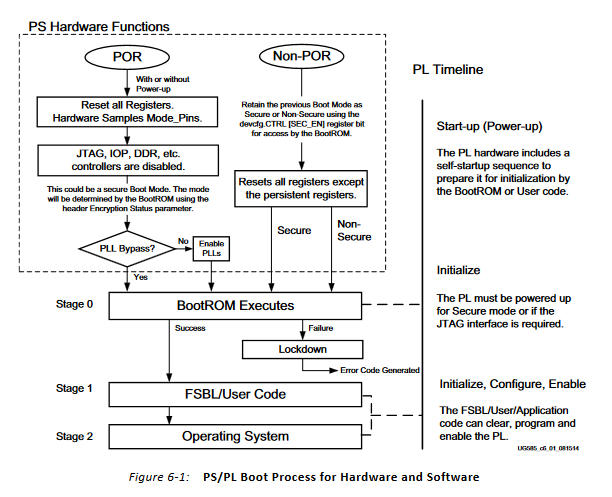

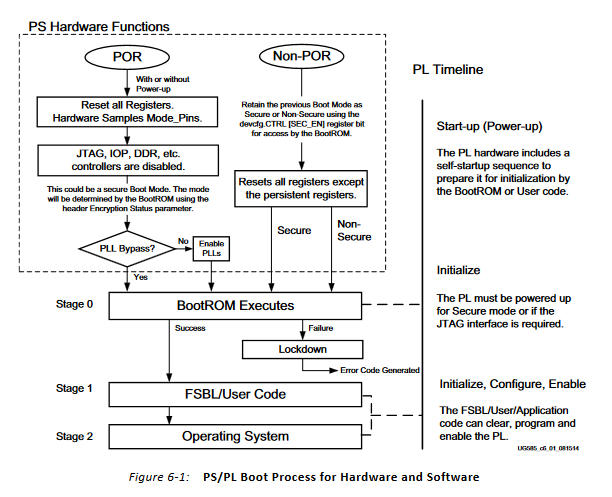

Every FPGA architecture from Xilinx is slight or big different. For PicoZed. Zynq FPGA on PicoZED starts to run codes, such as FSBL, after the power rails finishing the predefined power-up sequence. It is a multi-stage booting process, so Zynq FPGA starts to run codes before fully boot up. Please read Xilinx document: UG585,

There is a reset tree to control when to reset PS and PL after the booting is totally finished. FPGA source codes also can control some of the reset procedure if the user would like to change it.

Every FPGA architecture from Xilinx is slight or big different. For PicoZed. Zynq FPGA on PicoZED starts to run codes, such as FSBL, after the power rails finishing the predefined power-up sequence. It is a multi-stage booting process, so Zynq FPGA starts to run codes before fully boot up. Please read Xilinx document: UG585,

There is a reset tree to control when to reset PS and PL after the booting is totally finished. FPGA source codes also can control some of the reset procedure if the user would like to change it.