Does the Xilinx part on the board wait for the entire boot load to finish before it starts running or does it start right after BIT file is loaded?

Does the Xilinx part on the board wait for the entire boot load to finish before it starts running or does it start right after BIT file is loaded?

Clarification. When does PL start running? After the entire load or during?

After PS release PL reset if you like to load FPGA bitstream with FSBL.elf together. There are voltage level shifter between PS and PL domain. PL reset released from PS side can make voltage level shifter work properly on PL side.

Thanks, so to start the PL after FPGA bitstream I need to release the PL reset.

How do I go about this? Do I use the DONE output pin or is this done thru software?

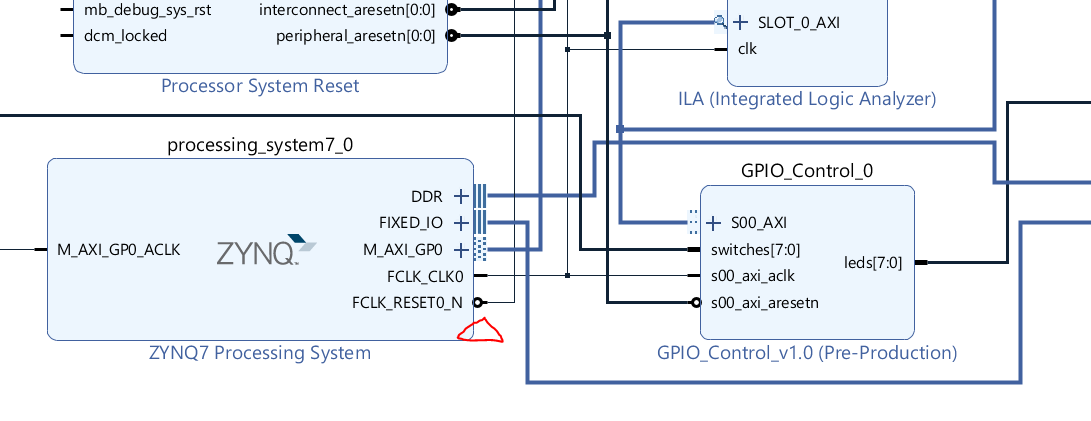

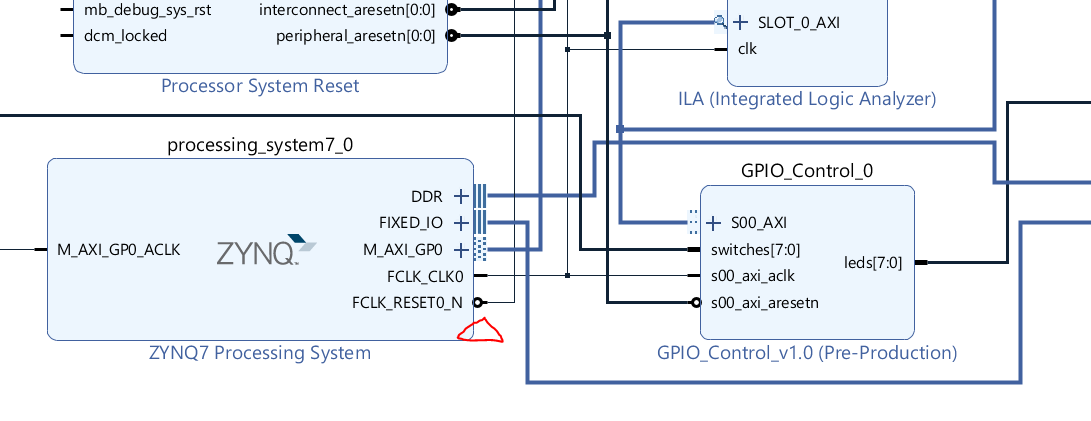

No,you don't need to do it. Zynq FPGA already has a default mechanism to do it. If you need reset PL after the default PL reset from PS, you can use many ways to do. One is with Linux initialization flow, which is software reset flow to reset PL once more. There is a reset pin from PS to PL if you build a FPGA project at Vivado. You can see the reset at Vivado project as this:

No,you don't need to do it. Zynq FPGA already has a default mechanism to do it. If you need reset PL after the default PL reset from PS, you can use many ways to do. One is with Linux initialization flow, which is software reset flow to reset PL once more. There is a reset pin from PS to PL if you build a FPGA project at Vivado. You can see the reset at Vivado project as this:

Issue solved. Bitstream is loaded and PL is configured, but because of large application load, the PS clk that I use for PL is not starting up until after complete load. So, it seams the PL is not running.

One correction on my previous points: the level shifter between PS and PL should be enabled after FPGA bitstream loaded. So please check DONE bit for bitstream loading.

Good to hear that you got things sorted out.