Hello everyone,

I'm working with a ZCU208 board by using the matlab/simulink board support provided at this link:

https://rfsoc-hdlcoder.readthedocs.io/en/latest/zcu208.html

All the examples work fine and I'm capable to modify the templates for my purposes without particular problems.

The only issue is related to when I try to set the sampling rate of the DACs over 7 Gsps, namely 8.6 GHz.

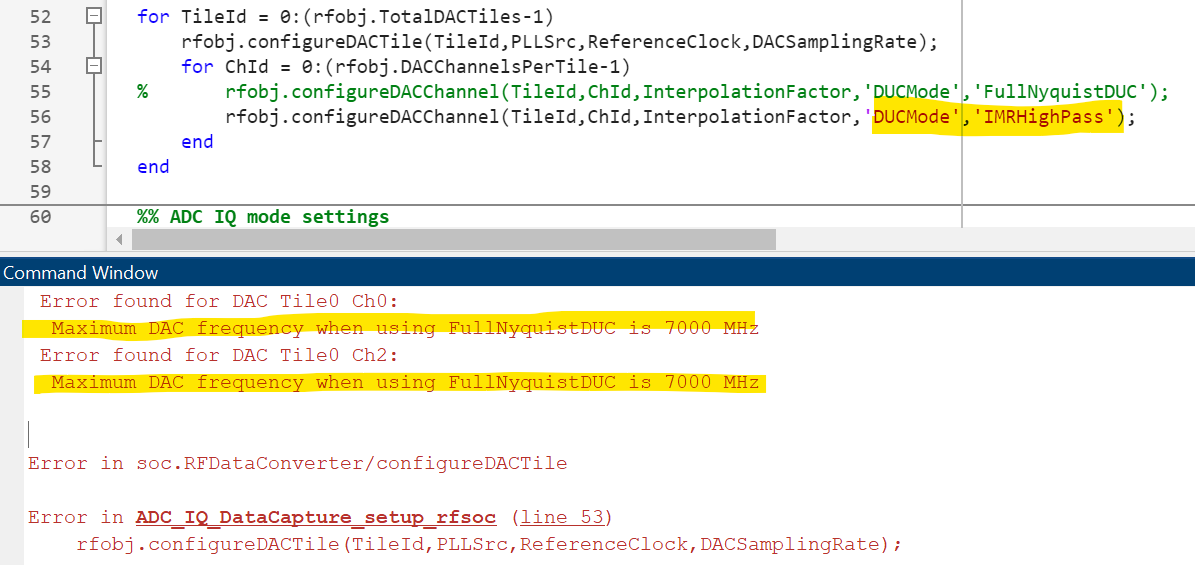

I receive the error: Maximum DAC frequency when using FullNyquistDUC is 7000 MHz

Of course, I'm not using Fully Nyquist mode, but I set the IMR filter in High Pass mode as depicted in the screenshot below:

It seems that the problem is connected with soc.RFDataConverter object provided by Xilinx, but I'm not sure.

Did anyone have the same problem or is able to replicate it?

Regards