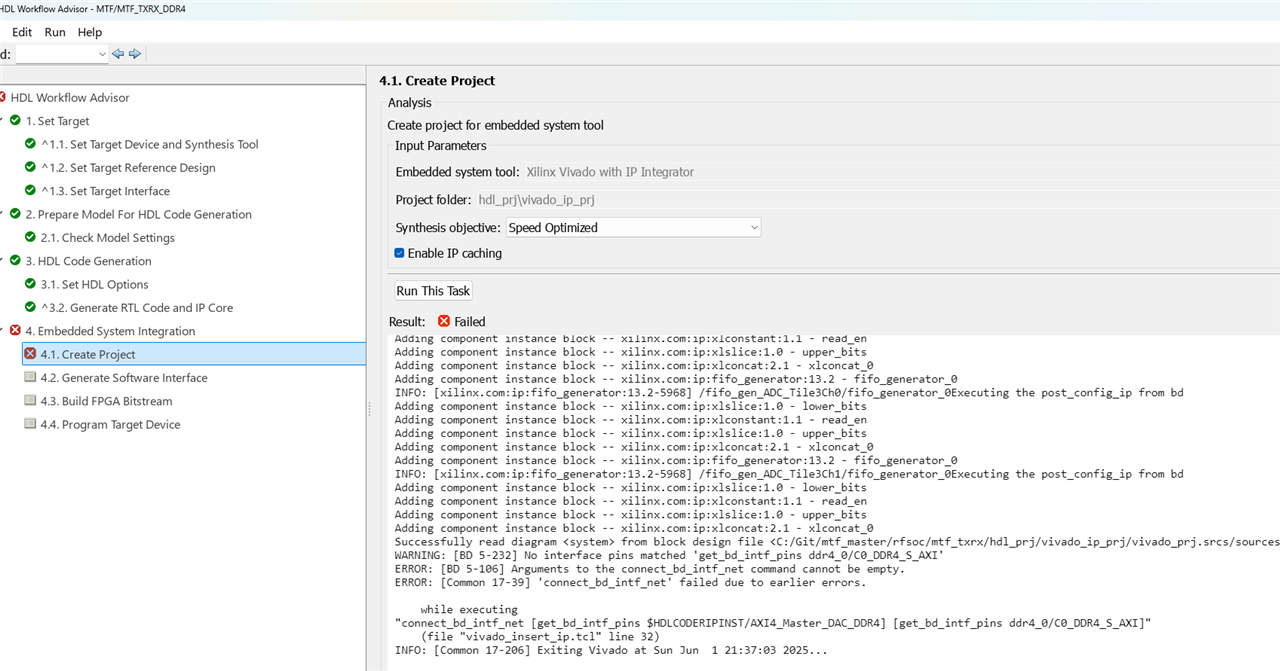

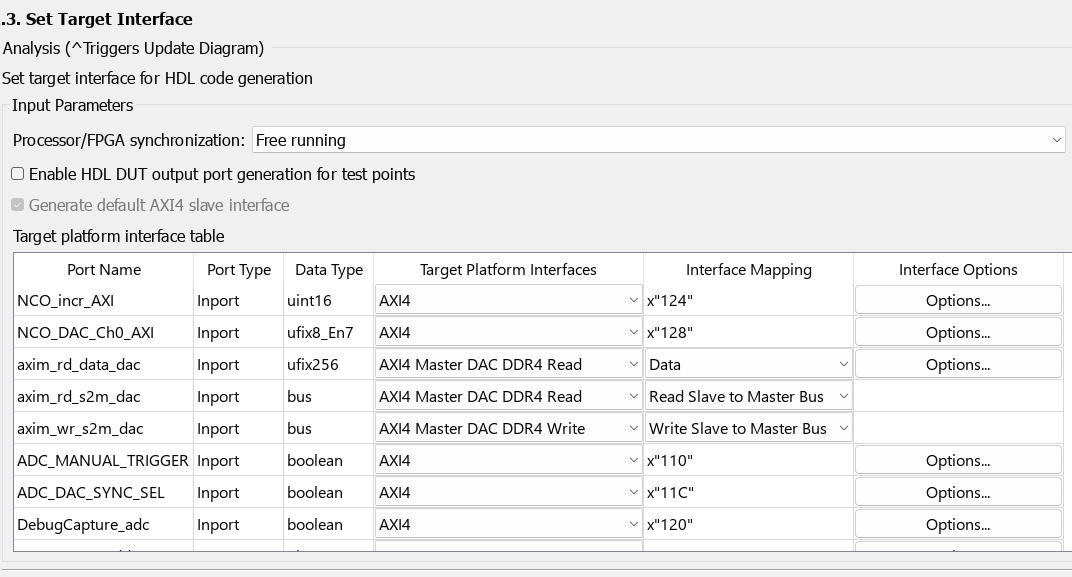

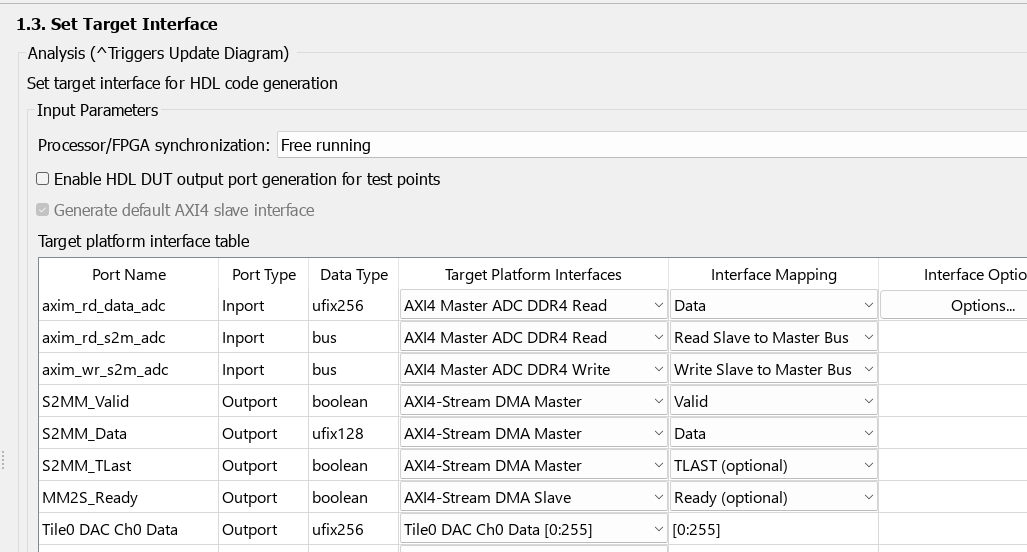

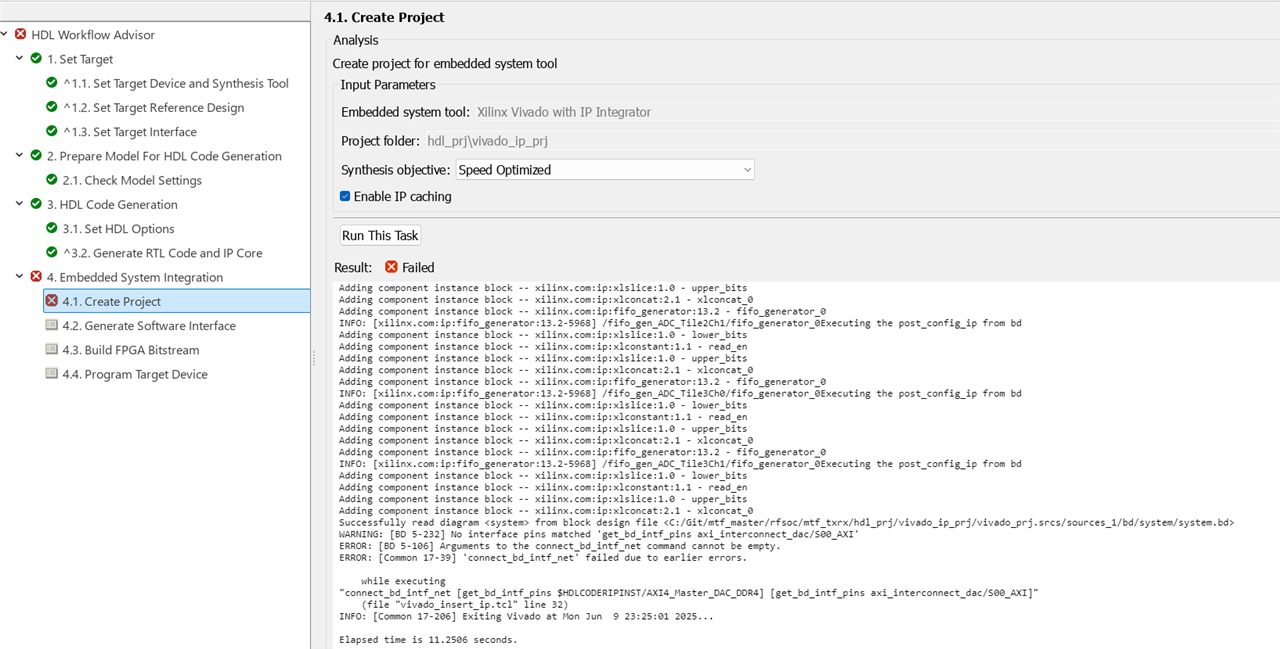

The examples provided for ADC/DAC with DDR4 interface only support one DDR4. I have modified them so I could simultaneously capture ADC samples to one DDR4 and stream DAC samples from another DDR4. I modified the reference designs and made sure that the HDL workflow advisor detects the changes in the plugin_rd.m. I also manually added 2 AXI4Master in plungin_rd.com. Everything is good till I make the Vivado project and it fails there! The failure is related to connecting the AXI to DDR4 MIG! I did everything you could possibly imagine, but no luck! That would be great if someone could provide instructions which work! Appreciate any response.