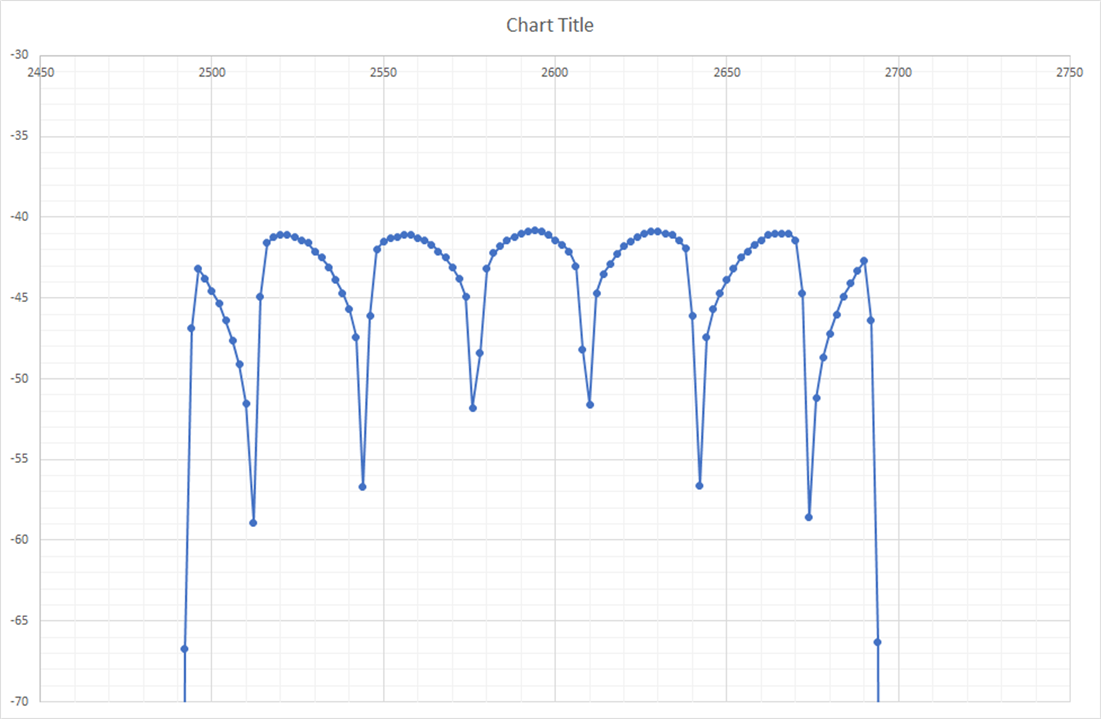

I have an RFSoC Design using Vivado 2020.2 where I have an data stream coming from the RFDC Block at 1536 M Sample Per Second (MSpS). The fabric won't clock at this rate so the RFDC block gives me a 8 sample wide stream blocking at 192 MHz. The stream feeds an FIR Block where it is low pass filtered and decimated by 6 to give me 256 MSpS. This stream is still clocked at 192 MHz and we see 2 samples per cycle with only every 2 of 3 cycles active. The trouble is that if I measure the frequency response of the filter, it's rubbish. Sharp dips of 10 dB or more in the passband response at regular intervals where it should be flat to within less than a dB.

If I change the filter configuration to not decimate and follow it be a separate block that decimates by 6 I see the expected flat response. I only have the filter from integer decimation by 6 to single rate, it uses the same coefficients etc.

The work around is expensive, the DSP slice requirement goes from 120 to 680.

Has anyone else seen anything like this?

I hate to blame the tools, and the FIR block is quite mature, but maybe operating at "Super Sample Rate" as Xilinx describe it in PG149 is a bit bleeding edge.

Best Regards

Paul