I have generated a design which uses via.

When I do the Gerber export I get a anti mask on the silk mask layer, so the via will show metal when built.

With BGA I have had far too many shorts if I do not put silk mask over them. I often leave the hole of the via as metal, as some fabs don't like that.

How do I make the mask on via's not appear on the silk mask layer outputs?

This to me means CS is not usable for BGA devices?

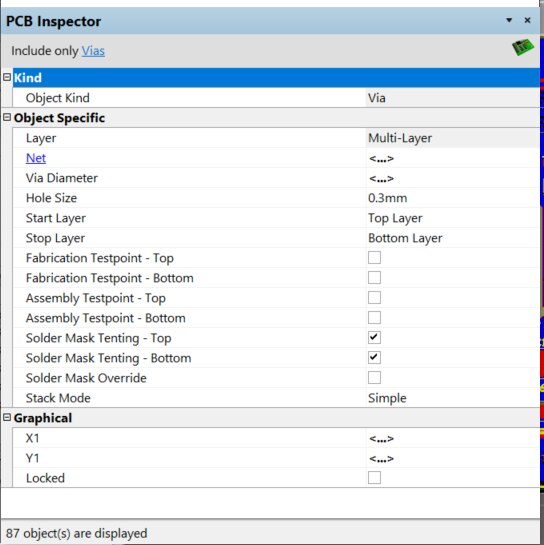

In Altium Designer you can set the tenting on the via as a rule.

Is this possible in CS, Sorry just started using it so not really sure where to start to have a go at fixing this.

See this pic with the D59 code appearing on the vias of the solder mask layer.

Thanks, much appreciated

Lee