Designing an Inverting Buck-boost Converter with MagI³C Power Module

WPMDH1302401 / 171032401171032401 (6 - 42 VIN / 3A / 5 - 24 VOUT)

ANS007B BY CHRISTOPHER RICHARDSON

1. Introduction

MagI³C Power Modules from Würth Elektronik eiSos are normally used as synchronous buck regulators, capable of stepping down a higher input voltage to a lower output voltage with high efficiency and a compact, low-EMI footprint. The inverting buck-boost is another topology that can be implemented with the MagI³C Power Module family using just a few adjustments. This topology converts a positive input voltage, VIN, into a negative output voltage, -VOUT, and the magnitude of -VOUT can be both greater than and less than the magnitude of VIN.

Figure 1: Input and Output voltage range

Input voltage range and the absolute value of the output voltage range can overlap when using an inverting buck-boost regulator. This application note will explain how to select the eternal components for the inverting buck-boost topology and show how the buck topology evaluation boards can be used for buck-boost as well. Figure 2 shows how a inverting buck-boost topology can be derived from a synchronous buck by reassigning the ground and output terminals and modifying the connection of the input capacitor.

Figure 2: Synchronous buck (left) and synchronous inverting buck-boost (right)

Figure 3 shows the basic schematic of a MagI³C Power Module from the VDRM family operating as a synchronous buck on the left, and then the changes needed for an inverting buck-boost on the right. Implementing the circuits of Figures 2 and 3 would not require CIN1. This capacitor is not shown in the block diagram and its benefit will be explained in section 4.7.1.

Figure 3: Synchronous buck (left) and inverting buck-boost (right) using VDRM family modules

2. Voltages and Currents in the Synchronous Inverting Buck-boost

Figure 4: The inverting synchronous buck-boost converter with the control MOSFET on (left) and with the sync MOSFET on (right). Duty cycle, D, is defined in EQ.2 below

Figure 4 shows the two switching states of the synchronous, inverting buck-boost converter. When the control MOSFET is on the voltage across the inductor, VL is equal to the input voltage, VIN. During this period, the current ramps up in the inductor. Also, the output capacitor sustains the output voltage. When the control MOSFET turns off and the sync MOSFET turns on the inductor current commutates, flowing through the system ground, the load, and through the sync MOSFET, generating a negative voltage across the load resistor with respect to system ground. The inductor current also charges the output capacitor, and the voltage across the inductor is equal to (-VOUT).

3. Voltage, Current and Duty Cycle Limitations

Selecting the proper MagI³C Power module for buck topologies is straightforward – the input voltage range, output voltage range and output current range listed in each module´s datasheet show the precise limits for each of these quantities. For the inverting buck-boost more calculations are required, and both the maximum input voltage range and the output current range are lower when using this topology than they are for the buck.

3.1. Input Voltage Range

Closer inspection of the buck-boost regulator in Figure 3 reveals that the module´s reference voltage is no longer system ground, but in fact is the negative output voltage. The total voltage from the VIN pin to the AGND pin of the module is equal to the input voltage plus the absolute value of the output voltage. This can be observed by considering that the voltages across CIN2 and COUT add together, with system ground at their midpoint. Table 1 shows the maximum input voltage rating for each member of the VDRM family:

| Type | Package | WE Order Code | Farnell Order Code | WE Part Description | VIN [V] | VOUT [V] | IOUT [A] |

|---|---|---|---|---|---|---|---|

| Variable Step Down Regulator Module (VDRM) | TO263-7EP | 171012401171012401 | 2505846 | WPMDH1102401J | 6 - 42 | 5 -24 | 1 |

| TO263-7EP | 171012402171012402 | 2505847 | WPMDH1152401J | 6 - 42 | 5 -24 | 1.5 | |

| BQFN-39 | 171020302171020302 | 2577475 | WPMDB1200362Q | 2.95 - 6 | 0.8 - 3.6 | 2 | |

| TO263-7EP | 171020601171020601 | 2505848 | WPMDH1200601J | 6 - 42 | 0.8 - 6 | 2 | |

| BQFN-41 | 171021501171021501 | 2505851 | WPMDU1251501N | 7 - 50 | 2.5 - 15 | 2.5 | |

| TO263-7EP | 171032401171032401 | 2505849 | WPMDH1302401J | 6 - 42 | 5 - 24 | 3 | |

| BQFN-39 | 171040302171040302 | 2577476 | WPMDB1400362Q | 2.95 - 6 | 0.8 - 3.6 | 4 | |

| TO263-7EP | 171050601171050601 | 2505850 | WPMDM1500602J | 6 - 36 | 0.8 - 6 | 5 | |

| BQFN-39 | 171060302171060302 | 2577477 | WPMDB1600362Q | 2.95 - 6 | 0.8 - 3.6 | 6 |

Table 1: Input voltage, output voltage and output current ranges for the VDRM MagI³C Power modules

So for example the 171 032 401 (42 VIN / 3 A / 5 to 24 VOUT) when operating at an input of 24 V would be limited to a theoretical maximum output voltage of -18 V. In practice at least 3 V to 4 V of headroom should be left for ringing and transients, so the recommended maximum output voltage for an input of 24 V would be around 14 V to 15 V.

Buck-boost operation also has a distinctive advantage over the buck regulator: as the name implies, the absolute value of the output voltage can be higher or lower than the input voltage. As long as the minimum on-time and off-time of the modules are respected, an output of -12 V is possible from an input as low as 6 V. Furthermore, once the module is operating the input voltage can go even lower than the normal, buck mode minimum VIN of 6 V as long as the sum of (VIN + |-VOUT|) is greater than or equal to 6 V. Figure 5 shows maximum input voltage as a function of the output voltage and also maximum output voltage as a function of input voltage.

Figure 5: Graphical maximum input voltage and output voltage relationships

3.2. Maximum Output Current

In the buck-boost topology the maximum output current that the regulator can deliver is a function of the duty cycle. (It can also be considered to be a function of the ratio of input voltage to output voltage.) This is because MagI³C Power modules sense inductor current, and in the buck-boost topology the average value of inductor is not the same as the average value of the output current, as shown in EQ.1. Furthermore, MagI³C Power modules sense inductor current during the high side MOSFET on-time, when the current reaches its peak value. The over-current protection circuit monitors this peak inductor current. In order to calculate peak current the average current must first be determined. Average inductor current is a function of duty cycle (D) defined by:

| EQ.1 | |

| EQ.2 |

The low voltage drops across the power MOSFETs and the internal power inductor can be ignored because they are small in comparison to -VO and VIN for the majority of applications. In order to calculate the maximum possible output current for the buck-boost the output voltage minimum input voltage, inductance and switching frequency are needed. First, maximum duty cycle is calculated.

| EQ.3 |

Each MagI³C Power module has a fixed over-current protection threshold – for convenience these limits along with the internal power inductors are listed in Table 2.

| WE Part Number | Farnell Part Number | Minimum Current Limit, IOCP [A] | Internal Inductance, L1 [μH] |

|---|---|---|---|

| WPMDH1200601JT | 2505848 | 2.3 | 10 |

| WPMDM1500602JT | 2505850 | 5.4 | 3.3 |

| WPMDH1102401JT | 2505846 | 1.5 | 15 |

| WPMDH1152401JT | 2505847 | 2.4 | 15 |

| WPMDH1302401JT | 2505849 | 3.2 | 10 |

Table 2: Minimum over-current protection threshold over the full temperature range

Peak-to-peak inductor ripple current and peak current for buck-boost regulators are calculated as follows:

| EQ.4 | |

| EQ.5 |

Finally, the equations can be rearranged to show the maximum achievable output current for a given set of conditions:

| EQ.6 |

3.3. Duty Cycle Limits

The duty cycle in the VDRM family of MagI³C Power modules is not directly limited due to the constant on-time control, but the high side switch must turn off for at least 260 ns during each switching cycle and must stay on for at least 150 ns during every switching cycle. These limits create an effective minimum and maximum duty cycle that the modules can achieve for all topologies, and in all topologies, the limits become more and more restrictive as switching frequency increases. In general, the buck-boost is more likely to run into the maximum

Figure 5: Duty cycle limits vs. switching frequency from 100 kHz to 1 MHz

duty cycle/minimum off-time limits than the buck because the buck-boost can operate with lower input voltages than a buck regulator.

4. Design Guide

This section will guide the user through the design and external component selection of an inverting buck-boost regulator meeting the following specifications:

Input Voltage: VIN = 10 VDC to 28 VDC

Output Voltage: VOUT = -12.0 VDC, IO-MAX = 1.0 A

Estimated Power Efficiency, η = 90%

This converter can operate from 12 VDC or 24 VDC power inputs, rectified 12 VAC inputs, 12 V and 24 V batteries. The -12 V output could be used to power amplifiers, sensors or other analog functions that require a negative voltage.

Figure 6: Circuit schematic for the design example

4.1. Selecting the Right Power Module

This process will often require some iteration. To start, the maximum voltage that will be applied from the VIN pin to the VOUT pin is (28 V + 12 V) = 40 V, so the 5 A MagI³C-VDRM module with its 36 V limit can be discarded. Then, average inductor current can be calculated using EQ.1 and EQ.3. Keep in mind that the highest current occurs when input voltage is at a minimum:

If average current is more than 2.0 A then the three members of the family that deliver 1.0 A, 1.5 A and 2.0 A of output current can also be discarded, leaving only the 3.0 A version of MagI³C-VDRM. This is the part that will be used.

4.2. Select the Switching Frequency

This is a fundamental choice that will affect the power efficiency and dissipation in the module. Since the power inductor is internal, the compromise of space/size vs. efficiency is not as relevant as it is with standard switching regulators. Therefore the selection criteria are power efficiency/dissipation, the size of the input and output capacitors, the peak ripple current (so as not to run into the over-current protection) and the existence of any sensitive frequency bands. Because of the 150 ns minimum on-time requirement, the maximum possible switching frequency is calculated as follows:

| EQ.7 |

2.9 MHz is far beyond the maximum range recommended for the 3 A MagI³C-VDRM, which is 200 kHz to 800 kHz, and in fact 2.9 MHz is far beyond the practical switching frequency for a MagI³C Power module that delivers 12 W of output power – see the “Power Dissipation” section for details on the dependence of power dissipation on frequency. 500 kHz is a much more reasonable choice, and will be used.

4.3. Check the Peak Current and Over-current Protection

As discussed in the “Maximum Output Current” section, the ratio of input voltage to output voltage and the switching frequency all affect the maximum output current. With the 3.0 A module and the switching frequency selected, EQ.6 can be evaluated to make sure that the over-current protection will not engage:

Based upon this evaluation, the 3 A MagI³C-VDRM is an excellent choice.

Based upon this evaluation, the 3 A MagI³C-VDRM is an excellent choice.

4.4. Select the On-time Resistor, RON

The VDRM family of MagI³C Power modules uses a controlled on-time control system, and switching frequency is programmed by selecting a resistor that controls the time that the high-side MOSFET stays on each cycle. The on-time varies in inverse proportion to the input voltage to maintain a constant switching frequency over the input voltage range. For this reason, the selection equations are the same for buck and buck-boost regulators:

| EQ.8 |

The closest E96 value is 187 kΩ, and once the actual RON value is selected, the maximum on-time should be evaluated for use in the next set of calculations:

| EQ.9 |

4.5. Calculate the Internal Inductor Currents

Average inductor current is already known: from EQ.1 this is 2.45 A. Given the maximum on-time and the inductance the peak-to-peak ripple current and the peak inductor current can both be calculated:

| EQ.10 |

| EQ.11 |

4.6. Select the Output Capacitors

A target maximum for the peak-to-peak output voltage ripple must be defined first. If the loads do not specify their tolerance to ripple, values of 1-2% of the output voltage are typical. In this case, 1% of 12 V is 120 mV.

| EQ.12 | |

| EQ.13 |

Unlike the smooth, low-RMS output of a buck converter, the buck-boost has a high-RMS, pulsating output current similar to the output of a boost or flyback converter. It is therefore very important to calculate the RMS current seen by the output capacitor(s):

| EQ.14 |

In general, for values of capacitance less than approximately 20 μF it is possible to use purely ceramic capacitors without excessive cost. Furthermore, multi-layer ceramic capacitors (MLCCs) can withstand very high values of RMS current, making them an excellent choice for the output capacitors of buck-boost regulators. Keeping in mind the loss of capacitance of MLCCs when they operate with a DC bias, two 1210 size capacitors rated to 25 V and 10 μF each and an X7R dielectric will give about 7 μF each when the 12 V output voltage is applied across them. The typical ESR for such capacitors is around 2 to 3 mΩ, well below the calculated maximum, and hence the output voltage ripple will be much lower than the 120 mVP-P target.

4.7. Select the Input Capacitors

As with the output capacitors, the first step is to define a maximum for the input voltage peak-peak ripple. This value depends greatly upon the mechanical and electrical location of the buck-boost regulator within the application: when connected to the input power supply through a wiring harness, or in applications where regulations such as EN55025 define strict limits for conducted EMI the value for Δvin-MAX is defined precisely. In such cases, an additional L-C or ferrite-C filter is often needed to meet EMI regulations. (Note: more detailed information on filter design can be found in “Trilogy of Magnetics”, available from Würth Elektronik.) In the absence of set limits, a typical target is 1% of the minimum input voltage – in this case, 1% of 10 V is 100 mV. Input capacitance can then be calculated as:

| EQ.15 | |

| EQ.16 |

Buck-boost regulators pull high-RMS pulsating input currents just like buck regulators or flyback regulators, so again the calculation of input capacitor RMS current is critical:

| EQ.17 |

| EQ.18 |

Two Positions for the Input Capacitors

Figure 7: CIN1 is placed from VIN to –VOUT, CIN2 is placed from VIN to GND, showing the current paths

Because of the way, the inverting buck-boost topology uses a buck regulator that is referenced to the negative output voltage there are two places where input capacitance is used. CIN2 is absolutely mandatory because it supplies the heavy AC currents drawn by the converter and it holds up the input voltage while the control MOSFET is off and the sync MOSFET is on, as shown in Figures 4 and 7. CIN1 is not strictly necessary, but it is very helpful for lowering the output voltage ripple, which reduces problems with loads that are sensitive to switching ripple such as amplifiers and ADC converters. Lower output ripple also improves conducted EMI at the output of the converter.

At first, CIN1 may appear to be an additional component and an additional cost to the BOM, but in practice this component can save both money and board area by reducing the size and cost or even eliminating output filters.

CIN1 sees an average voltage of (VOUT + VIN), and for this application the worst case is at VIN,MAX where the total reaches 40 V. CIN2 is the “standard” input capacitor placed from VIN to system ground, so the maximum voltage

is equal to VIN,MAX or 28 V in this example.

Balancing the total capacitance between positions CIN1 and CIN2 affects both the input voltage ripple (taken from VIN to system ground, where conducted EMI is measured) and the output voltage ripple. In general, the best compromise comes from putting half of the total capacitance calculated in EQ.15 at CIN1 and the other half at CIN2.

MLCCs are an excellent choice for the input capacitors for inverting buck-boost regulators due to the high- RMS currents seen by both CIN1 and CIN2. The 40 V and 28 V maximum voltages seen by CIN1 and CIN2 respectively mean that a minimum of 50 V rated capacitors should be used, with X5R or X7R dielectrics. For this example 1210, X5R, 50 V rated 10 μF devices will be used. Despite the loss of capacitance due to DC

bias, one advantage to designing with MLCCs is that the worst case where the most capacitance is needed is at the minimum input voltage where the capacitance loss is lowest. For this example at 22 V for CIN1 the actual capacitance is around 6 μF, and at 10 V for CIN2 the actual capacitance is around 9 μF. One capacitor will be placed at each position. Owing to the complex interaction and the difficulty of measuring currents through capacitors in the lab, a simulation can be very helpful. Figures 8 and 9 show the input voltage ripple with respect to ground and the output voltage ripples between two cases: all of the capacitance placed at CIN2 and then the recommended split of capacitance between the two positions.

In this example the input voltage ripple is similar between the two cases but is actually slightly higher when the capacitance is split between CIN1 and CIN2. This is due to the capacitance loss from the application of (VOUT + VIN) across CIN1. The dramatic improvement is in the output voltage ripple, and this comes from the continuous AC path that CIN1 provides from the input voltage to the output voltage. Without CIN1 there is no direct energy transfer from the input to the output during either of the two switching states, but with CIN1 AC current can flow, making the output ripple closer in both wave shape and amplitude to the desirable, low output voltage ripple of a buck converter.

Figure 8: Input voltage ripple: all capacitance at CIN2 (red), 50-50 split of capacitance (green)

Figure 9: Output voltage ripple: all capacitance at CIN2 (red), 50-50 split of capacitance (green)

4.7.2. Damping to Prevent Resonance at the Input

Figure 10: Parasitic input lead inductance LPARA, input capacitors and damping capacitor CD with controlled ESR

The combination of large parasitic inductance from long input supply leads and purely ceramic input capacitors creates a high quality factor L-C filter that can oscillate when it feeds the negative input impedance of a switching converter. From a mathematical perspective a switching power supply will resonate with the input filter whenever the impedance of the input filter is higher than the absolute value of the switcher´s negative input impedance. This sub-harmonic resonance is often called “power supply interaction”, and Figure 11 shows the adverse effect on the example circuit being designed in this application note when connected to the input power supply with 30 cm leads. The worst case for power supply interaction is at the minimum input voltage and maximum output current, where the absolute value of the converter´s input impedance is lowest. This oscillation at approximately 43 kHz is a source of EMI and should be eliminated by adding a larger capacitor

with higher ESR in parallel with CIN1 to damp out the resonance.

Figure 11: Input voltage with sub-harmonic oscillation due to power supply interaction when VIN ≤ 10.5 V, IO = 1,0A

The damping capacitor CD should be 4-5 times greater in capacitance than the ceramic capacitor CIN1, and in order to critically damp, the L-C resonance the minimum ESR of the damping capacitor can be calculated as:

| EQ.19 |

For this example, the actual input inductance is purely parasitic, and in such cases, a value of 1 μH can be assumed. When an input inductor is used, this value is substituted for LF. The ESR of most large MLCCs falls in the range of 2-3 mΩ and can be ignored. Aluminum capacitors are a good choice for damping due to their high ESR, but if necessary, a discrete resistor can be added in series with CD in order to ensure enough damping resistance. For this example, assume that CIN1 has 100% of its rated capacitance when VIN = 10 V (CIN1 = 10 μF). Therefore 47 μF provides the 4-5x capacitance needed. A 47 μF, 50V aluminum electrolytic capacitor with an impedance of 300 mΩ and rated to 500 mA of RMS current is an excellent choice. Not only will this capacitor damp any potential oscillation, it will also reduce both input voltage and output voltage peak to peak ripple.

Figure 12: Input voltage ripple with damping capacitor CD in parallel with CIN1. VIN = 10,0 V, IO = 1,0 A

4.8. Output Voltage, UVLO and Soft-start

Output voltage is selected with a resistor divider pair using the same equations as the buck regulator. Select a value for the top feedback resistor RFBT between 10 kΩ and 50 kΩ. For this example, RFBT is 20 kΩ. Then the bottom resistor RFBB is calculated as:

| EQ.20 |

Soft-start is also unchanged. However, the input under-voltage lockout does require some changes. If a standard resistor divider is used extending from VIN to -VO then the rising, enable threshold stays the same as for a buck regulator. This is because the -VO net is at approximately zero volts before the buck-boost starts up. However once the regulator begins operating the voltage at the module´s GND pin drops by the output voltage, shifting the falling UVLO threshold (the disable threshold) down by an amount equal to the output voltage. Care must be taken not to exceed the 6.5 V maximum operating voltage of the EN pin once the module is operating and the total voltage between the VIN and GND pins equals (VIN + VOUT). The standard buck evaluation boards for the MagI³C Power modules include a 5.1 V zener diode connected from the EN pin to the GND pin to prevent overvoltage, and this zener diode should be included in all designs where UVLO is

done with a simple resistor divider.

4.8.1. Level Shift Circuits for Precision UVLO or Logic Enable

In some applications the large hysteresis between the rising enable UVLO threshold (VEN) and the falling, shutdown threshold (VSD) can be an advantage, but in most cases the difference between VEN and VSD is less than one volt. In order to achieve a small hysteresis a level-shifting comparator is needed. Figure 13 shows one example built with low-cost parts.

Figure 13: Level-shifting comparator for precision UVLO with controlled hysteresis

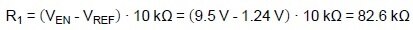

The following equations define the resistor values needed to set the desired UVLO thresholds:

VEN = 9.5 V VSD = 9.0 V

(Set R1 = 82,5 kΩ) | EQ.21 |

The logic high enable voltage at the EN pin should be set to around 3 V.

(Set R4 = 13.7 kΩ) | EQ.22 |

(Set R3 = 3.4 MΩ) | EQ.23 |

(Set R2 = 13 kΩ)

Referencing the module to the -VO net also changes the interface for a CMOS or TTTL logic level enable/shutdown from other ICs, microcontrollers, etc. A signal-level P-MOSFET and two resistors are required as shown in the left-hand image of Figure 3. RENT and RENB should both be set to 10 kΩ.

5. Using the Buck Evaluation Board for Inverting Buck-boost

Just a few steps and a soldering iron are needed to evaluate the MagI³C Power modules as buck-boost regulators. To create the circuit designed in Section 3, begin with the 3 A MagI³C-VDRM evaluation board. Then follow these steps:

1. The original input capacitors are two 1210, X5R, 50V, 10 μF MLCCs. Leave one in place as CIN1, then remove the second, stand it up and connect it with the shortest wire possible to the former “VOUT” node, which is now system ground. This will be CIN2.

- To prevent the sub-harmonic oscillation explained in Section 3.7.2, add an aluminum electrolytic capacitor rated to at least 47 μF, 50 V between the VIN and -VOUT nodes.

2. To move the enable (VIN rising) threshold to 9.5 V, replace RENB with an 18 kΩ, 1% resistor. Keep in mind that the falling threshold will be shifted upwards by the 12 V of the output voltage, such that in practice the regulator will continue operating until the input voltage falls to near zero.

- To use a logic enable: Remove RENT and connect a 12 kΩ through-hole resistor from VIN to the source of a through-hole P-MOSFET. Connect the base to system ground, and the drain to the EN pin of the module.

- To set the hysteresis as defined in Section 4.8.1, remove both RENT and RENB. Assemble the circuit of Figure 13 along with the calculated values on a small section of perforated PCB (“perfboard” or “dot PCB”) and then connect it with the shortest wiring possible to the VIN, GND, -VO and EN nodes of the evaluation board.

3. Affix stickers or cross out the original “GND” marking and re-label it as “-VOUT”. Do the same for the original “VOUT” marking and label it as “GND”. Using a different colored hookup wire such as blue will help remind the user that the output voltage is negative.

- Keep in mind that many electronic loads only work with positive voltages, so the system ground of the modified evaluation board should connect to the positive input of the e-load, and the negative output voltage of the evaluation board should connect to the negative input of the e-load.

Figure 14: 178032401178032401 evaluation board with modifications for use as an inverting buck-boost

6. Thermal Considerations

The theory from the 178032401178032401 datasheet in the section titled “Power Loss and Board thermal Requirements” can be applied to the buck-boost regulator with a few changes. Start by reviewing the following two plots from the datasheet:

Figure 15: Thermal response data from the MagI³C Power Module - VDRM (171 032 401) datasheet

In order to use the curves from Figure 15, substitute the inductor current IL-AVG calculated in EQ.1 for output current. The worst case for power dissipation is when input voltage is lowest and therefore inductor current is highest. Substitute (VIN,MIN + |VOut|) for VIN in the curve of Power Loss vs. Output Current. For this example, (10 V + 12 V) = 22 V, so the red curve for VIN = 24 V is closest. Recalling that the average inductor current is 2.45 A, the power dissipation, PD read from the curve is approximately 2.5 W. From the datasheet, the maximum thermal resistance needed to keep the module´s die temperature below the limit of 125 ºC is:

| EQ.25 |

The curve of Thermal Resistance vs. Board Area shows that approximately 55 cm2 is needed to dissipate this much power and keep the module temperature within the 125ºC limit.

7. Bill of Materials

| Index | Description | Size | Value | WE Order Code | Farnell Order Code |

|---|---|---|---|---|---|

| U1 | MagI³C Power Module | 7 PIN VDRM | UIn: 6 - 42 V, UOut: 0,8-6 V,IOut: 3 A | 171032401171032401 | 2505849 |

CIN1, CIN2, COUT1, COUT2 | Multi-layer Ceramic Capacitor | 1210 | 10 μF, 50 V, +/-20%, X5R | ||

| CD | Aluminum Electrolytic Capacitor | 8 x 11.5 mm | 100 μF, 0.87 A, 0,3 Ω | EEUFR1H101 | |

| CSS | Multi-layer Ceramic Capacitor | 0603 | 4,7 nF, 50 V, +-10%, X5R | ||

| RENB, RENT | Thick Film Resistor | 0603 | 11.8 kΩ, 1% | ||

| RFBB | Thick Film Resistor | 0603 | 1.43 kΩ, 1% | ||

| RFBT | Thick Film Resistor | 0603 | 20 kΩ, 1% | ||

| RON | Thick Film Resistor | 0603 | 187 kΩ, 1% |

8. PCB Layout

The following section provides a step-by step guide to PCB layout for best efficiency, thermal management and electromagnetic compatibility (EMC). Figure 16 shows the complete schematic, including optional input and output filters for other circuit configurations or requirements.

Figure 16: Complete circuit schematic for PCB layout

One optional component not represented on this schematic is a heatsink for the MagI³C module, a Fischer FK 244 08 D PAK heatsink. The 3.5 mm x 9 mm top layer pads on either side of the module (seen in Figures 17 and 18) are for mounting of this heatsink.

8.1. Place the Module and the Ceramic Input Capacitors

8.1.1.Switching Frequency and “Ringing” Frequency

In general, there are two fundamental noise frequencies in hard switched converters: the switching frequency and the “ringing” frequency. “Ringing” refers to the oscillation that occurs when energy stored in the parasitic capacitance of semiconductor switches releases during the switch openings and closings and then rings with the parasitic inductance present in the circuit. Ringing typically occurs at frequencies that are several orders of magnitude higher than the switching frequency, usually in the range of 50 MHz to 200 MHz. The current loop with the highest electrical noise (electromagnetic interference, EMI) is the one connecting the input capacitor(s) to the internal power MOSFETs of the MagI³C Power modules, so minimizing the area enclosed by this loop is critical for keeping radiated EMI as low as possible. Place the smallest capacitors closest to the pins/pads of the module where they can be most effective in filtering the ringing. In this context, “smaller” refers both the capacitance of the part and their physical size. The higher the frequency of a signal the more efficiently it radiates with decreasing loop size. Therefore lower capacitance will filter higher frequencies more effectively.

Just as important is the physical size of the capacitors because the smaller the device is the lower its parasitic inductance (ESL), and that also makes the physically smaller capacitor a better filter of higher frequency noise.

8.1.2.Routing the Two Input Loops

For the inverting buck-boost there are two input loops: one between VIN, the power switches and GND, and the other between VIN, the power switches and -VO. A compromise is needed, and priority should be given to the VIN-Switches-VO loop because it carries heavier peak-to-peak ripple current and therefore radiates more EMI than the VIN-Switches-GND loop.

Figure 17: Place the input capacitors in the smallest possible loops, right next to the pins/pads of the module. The VIN-Switches-VO loop is in green and the VIN-Switches-GND loop is in blue

8.1.3. Place Larger, Higher Capacitance Capacitors Farther Away

Capacitor Cd provides input filter damping and also reduces the ripple current/voltage at the switching frequency. It can be placed farther away from the module because it is a higher capacitance device with much higher ESL and therefore it has little effect on the high frequency EMI.

8.2. Place the Output Capacitors and the Input/Output Filters

The output capacitors in the buck-boost topology filter a discontinuous, high-RMS current just like the input capacitors. They should include a mixture of smaller and larger ceramic devices to filter both the high frequency ringing and the low frequency switching and noise. As with the input, the smallest devices should go in closest to the pins/pads of the module, followed by the larger ceramic capacitors and finally any bulk capacitors (aluminum electrolytic, polymer aluminum, tantalum, etc). The input filter (LIN and CF) and the output filter (LOUT and C04-C05) are both optional – by default neither filter´s components are installed – but when they are used they should be placed farther out from the module. Both filters act on the noise generated at the switching frequency and the harmonics of the switching frequency, hence it is important to route them so that all of the input current coming from the input power supply and all of the output current going out through the output

connectors flows through the pads of the filter capacitors CF and C04-C05.

Figure 18: The output capacitors and L-C filters for the input and output of the converter

8.3. Place the Analog Components

In this case, “analog” refers to all the components that set the analog functions of the MagI³C Power modules, such as the output voltage, the UVLO threshold and the soft-start time. In this case these components should all go in close to the pins of the module, but the reason is different: By minimizing the length of the connections and the loop area between the analog components and the pins of the module their susceptibility to EMI generated by the power switches, the inductor and any external noise sources is minimized.

8.3.1. Place the Output Voltage Resistor Divider Close to the Module

One common layout error is placement of the output feedback resistive divider (Rfbt and Rfbb) close to the final output capacitor (C03 or C04, depending upon the use of the output filter.) This is a mistake because the high impedance of the trace connecting the midpoint of the divider to the FB pin is of very high impedance – it´s the input to a comparator or an operational amplifier. The high impedance makes this trace very susceptible to noise pickup. Instead, minimize this trace by keeping Rfbt and Rfbb just as close to the FB pin and the AGND pin as possible.

Use a Single-Point Reference for the Analog Components

Another useful technique is to route all of the analog components that connect to the AGND pin of the module with one top-layer trace or copper shape, and then connecting that shape to the AGND pin at only one point. (Note that electrically the AGND pin is connected to the -VO node prior to the output filter. In the schematic of Figure 16 this net is referred to as “IC_COM”.) A short trace will then connect the AGND pin to the thermal pad of the module, which is analogous to the “PGND” or “Power Ground” pins of standard switching regulator or controller ICs. This single point connection helps maintain a common reference voltage for all of the analog functions. Even if electrical noise is picked up by the AGND trace or shape, the relative reference voltage between the MagI³C Power module and the analog components will stay the same.

Figure 19: Placement of the analog components, with detail in the plot on the right

8.4. Route the Top Layer Power Polygons

The high current paths that carry the input and output current and connect the input and output capacitors should use wide traces or solid shapes. For devices with high power density like the MagI³C Power modules the copper shape connected to the power pad and pin 4 of the device is also the main path for heat to dissipate. Note that for the inverting buck-boost regulator this net is the negative output voltage, -VO prior to the output filter, labelled “IC_COM”. Routing the power shapes close to one another between nets such as VIN and GND, -VO and GND and VIN and -VO increases the beneficial parasitic capacitance between them, and this typically adds 100 pF to 1 nF that is very helpful for filtering the highest frequencies of EMI.

Figure 20: VIN, IC_COM and –VO power polygons

8.5. Route the Analog Components Before the GND Polygon

Begin by placing the reference trace or shape as discussed in the “Place the Analog Components” section and shown in Figure 19.

Figure 21: Single-point connection of all the analog components to the AGND pin and then to the power pad

8.6. Route System GND

For this buck-boost converter, the GND net carries an important link on the bottom layer between the negative connections of the input capacitors and the positive connections of the output capacitors. This shape helps to lower inductance in the VIN-Switches-GND loop. In general any paths that carry switching currents should be routed without changing layers or using vias because the vias introduce unwanted resistance and, even worse, added inductance. When it is absolutely necessary, use multiple vias in parallel to reduce both the resistance and the inductance.

Figure 22: GND net routed on the top and bottom layers

8.7. Flood the Bottom Layer for Thermal Management

The power pad of the module is connected to the IC_COM net, so the maximum area on the bottom layer should be connected to this net. It is important to keep the bottom layer as solid as possible for both electrical purposes (more beneficial parasitic capacitance between VIN and GND and between VIN and -VOUT) and for thermal management (more copper area connected through the thermal vias to the exposed pad). Only the short connection on the GND net and a minimum number of Kelvin sense lines are routed on this layer, and then the rest should be flooded with copper connected to IC_COM.

Figure 23: Bottom layer showing solid plane connected to IC_COM with multiple thermal vias

9. Conclusion

With some attention to detail the VDRM family of MagI³C Power Modules make excellent inverting buck-boost regulators. They offer a compact, low-EMI solution that can deliver negative output voltage for a variety of applications with a minimum of design headaches.

IMPORTANT NOTICE

The Application Note is based on our knowledge and experience of typical requirements concerning the areas, serves as general guidance and should not be construed as a commitment for the suitability for customer applications by Würth Elektronik eiSos GmbH & Co. KG. The information in the Application note is subject to change without notice. This document and parts thereof must not be reproduced or copied without written permission, and contents thereof must not be imparted to a third party nor be used for any unauthorized purpose.

Würth Elektronik eiSos GmbH & Co. KG and its subsidiaries and affiliates (WE) are not liable for application assistance of any kind. Customers may use WE’s assistance and product recommendations for their applications and design. The responsibility for the applicability and use of WE Products in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide

whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not. The technical specifications are stated in the current data sheet of the products. Therefore the customers shall use the data sheets and are cautioned to verify that data sheets are current. The current data sheets can be downloaded at www.we-online.com. Customers shall strictly observe any product-specific notes, cautions and warnings. WE reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services.

WE DOES NOT WARRANT OR REPRESENT THAT ANY LICENSE, EITHER EXPRESS OR IMPLIED, IS GRANTED UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT RELATING TO ANY COMBINATION, MACHINE, OR PROCESS INWHICHWE PRODUCTS OR SERVICES ARE USED.

INFORMATION PUBLISHED BY WE REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE A LICENSE FROM WE TO USE SUCH PRODUCTS OR SERVICES OR A WARRANTY OR ENDORSEMENT THEREOF.

WE products are not authorized for use in safety-critical applications, or where a failure of the product is reasonably expected to cause severe personal injury or death. Moreover WE products are neither designed nor intended for use in areas such as military, aerospace, aviation, nuclear control, submarine, transportation (automotive control, train control, ship control), transportation signal, disaster prevention, medical, public information network etc. Customers shall inform WE about the intent of such usage before design-in stage. In certain customer applications requiring a very high level of safety and in which the malfunction or failure of an electronic component could endanger human life or health customers must ensure that they have all necessary expertise in the safety and regulatory ramifications of their applications. Customers acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use ofWE products in such safety-critical applications, notwithstanding any applicationsrelated information or support that may be provided by WE. CUSTOMERS SHALL INDEMNIFY WE AGAINST ANY DAMAGES ARISING OUT OF THE USE OF WE PRODUCTS IN SUCH SAFETY-CRITICAL APPLICATIONS.

USEFUL LINKS

Application Notes: http://www.we-online.com/app-notes

REDEXPERT Design Tool: http://www.we-online.com/redexpert

Toolbox: http://www.we-online.com/toolbox

Product Catalog: http://katalog.we-online.de/en/

DIRECT LINK

ANS007b: Designing an Inverting Buck-boost Converter with MagI³C Power Module

CONTACT INFORMATION

Würth Elektronik eiSos GmbH & Co. KG

Max-Eyth-Str. 1, 74638 Waldenburg, Germany

Tel.: +49 (0) 7942 / 945 – 0

Email: appnotes@we-online.de