1. Add Microblaze Core First

It is easy to start with template. But that is not FPGA born to be. I start from scratch, add soft-core, UART, GPIO, peripherals. Then coding with Verilog to make the project run.

2. Create first Block Design

2.1 Click the Create Block Design button in the IP Integrator dropdown of Vivado's Flow Navigator pane. A block design provides a visual representation of the hardware design, and can be used to easily connect and configure IP cores.The two fields should be left as defaults with your customized Project Name.

Then add a Microblaze soft-core Processor IP to a Block Designroblaze processor IP to instantiate a processor within the FPGA design, refer to Programmable Logic - Digilent Reference, find CMOD-S7 with brief specifications

An external clock should be added to the block design. Open the Board tab, and find the system clock. Right-click on it and select Connect Board Component.

An external reset port added to the design. Click the Run Connection Automation button in the green Designer Assistance toolbar.

BTN0 is set as Reset Button,

Select Polarity,

Double click to modify the Clock Property

Now, use the Add IP button ( ) to add the MicroBlaze IP to the design.

) to add the MicroBlaze IP to the design.

Run Block Automation dialog, specify settings and make right the first time or it would be better to delete the core and add again than modify it.

Find the USB UART interface in the Board tab, right click on it, and select Connect Board Component to add UART

Run Auto Block Connect , then run Auto connection

Amazingly, neccessary blocks are added and connected automatically.

Of course, function shall be verified later.

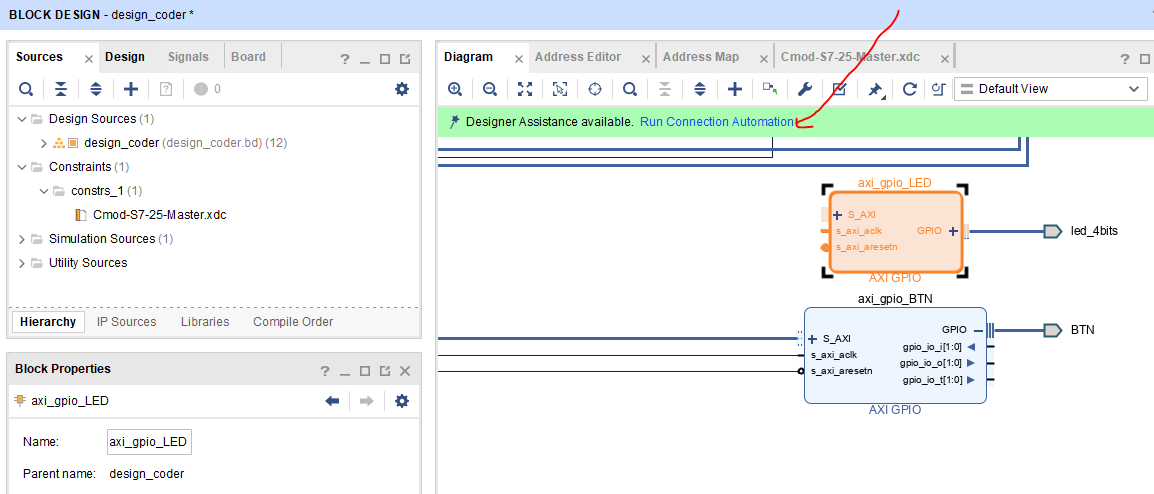

3. Add GPIO Peripherals

3.1 Find the GPIO section in Board Frame, right click on an LED interface, and select the Connect Board Interface option.

In the dialog that pops up, choose the “GPIO” interface (not GPIO2) of a new AXI GPIO IP

Manually addeda second AXI GPIO IP and manually constrained with an XDC file as Button. Click the Add IP button () and search for “AXI GPIO”. Then rename it to axi_gpio_BTN

Clicking on the text “GPIO”, right click on the highlighted text, and select Make External.

A Xilinx Design Constraint (XDC) file must be added to the project to tell Vivado which FPGA pins to connect the interface to.

3.2 Add a Master XDC File to a Vivado Project

Download and extract digilent-xdc-master.zip and click the Add Sources button ,

Un-comment the button constraints by removing the single leading '#' character in each line corresponding to the buttons in the XDC file will appear in the Sources tab.

Select the GPIO_0 external port that is connected to the AXI_GPIO_BUTTONS block. Change the name of the external interface to “btn” in the Properties pane.

Then Run Connection Automation again after setting the property of GPIOs.

Address assignment is part of work, if not automated , it has to be made manually.

If Ok, the diagram shown without errors.