Dear all,

This is my first post, so please be patient if I make any mistakes.

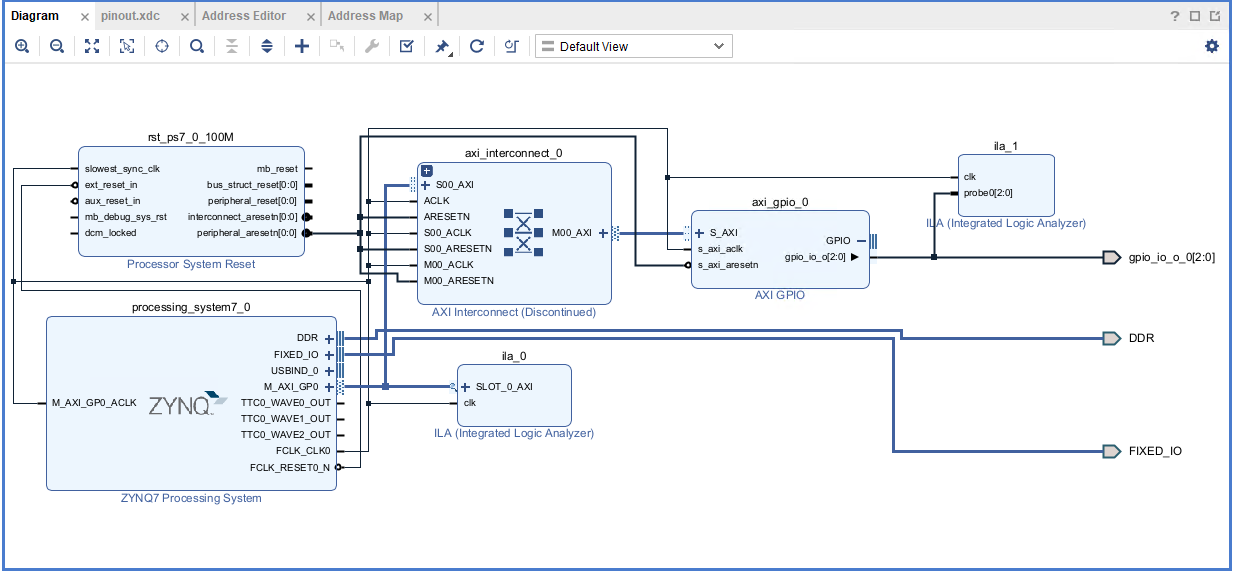

I am working with a MicroZed board, using Vivado 2024 and PetaLinux 2024. I am following some tutorials to create a simple project with:

- Zynq processor

- AXI GPIO

Goal:

I want to control a GPIO on JX2 of the MicroZed.

- The specific pin is pin 13 on JX2, which corresponds to G14 on bank 35.

My XDC file:

set_property PACKAGE_PIN G14 [get_ports gpio_io_o_0[0]]

set_property IOSTANDARD LVCMOS33 [get_ports gpio_io_o_0[0]]

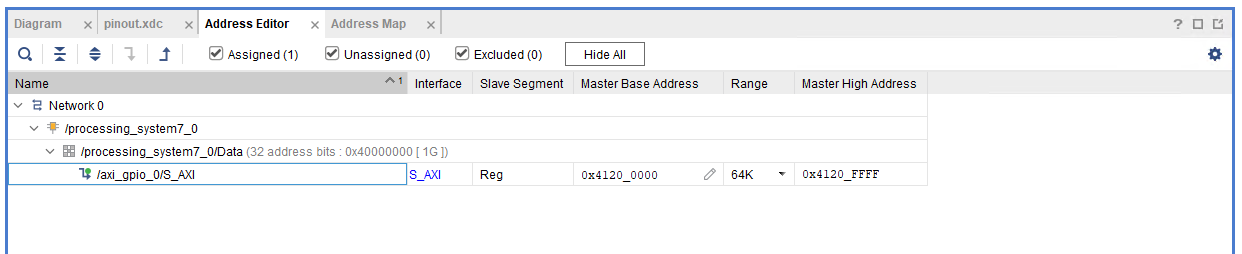

I created my Vivado project, assigned an address to the AXI GPIO interface, and built my PetaLinux project. I then booted the MicroZed using an SD card.

Everything seems to work correctly. Running the following command:

ls -lh /sys/class/gpio

I get:

--w------- 1 root root 4.0K Jan 1 1970 export

lrwxrwxrwx 1 root root 0 Jan 1 1970 gpiochip512 -> ../../devices/soc0/pl-bus/41200000.gpio/gpio/gpiochip512

lrwxrwxrwx 1 root root 0 Jan 1 1970 gpiochip515 -> ../../devices/soc0/axi/e000a000.gpio/gpio/gpiochip515

--w------- 1 root root 4.0K Jan 1 1970 unexport

This confirms that gpiochip512 is correctly mapped to my PL AXI GPIO.

I also added an ILA (Integrated Logic Analyzer) in my PL design. When I toggle the GPIO with:

echo 1 > /sys/class/gpio/gpio512/value

I can see the GPIO signal changing in the ILA.

Issue:

However, when I check the physical pin (JX2, pin 13) with an oscilloscope, I see no signal change.

Has anyone encountered a similar issue? Any suggestions on what I might be missing?

Thanks in advance for your help!