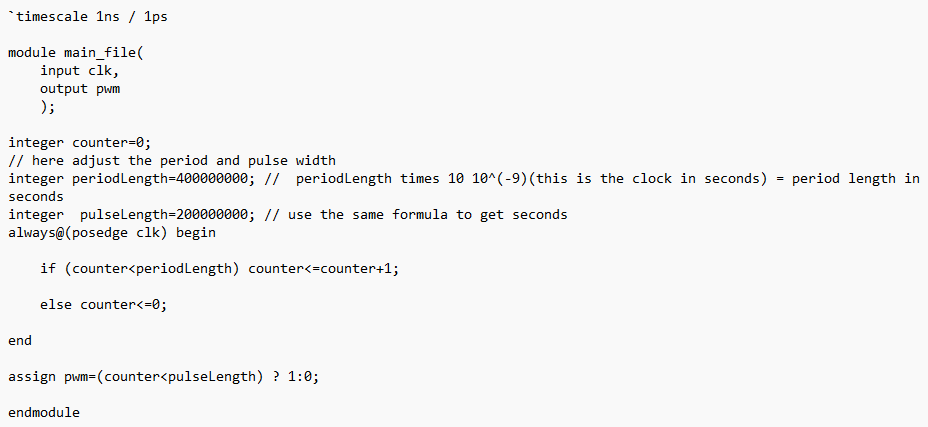

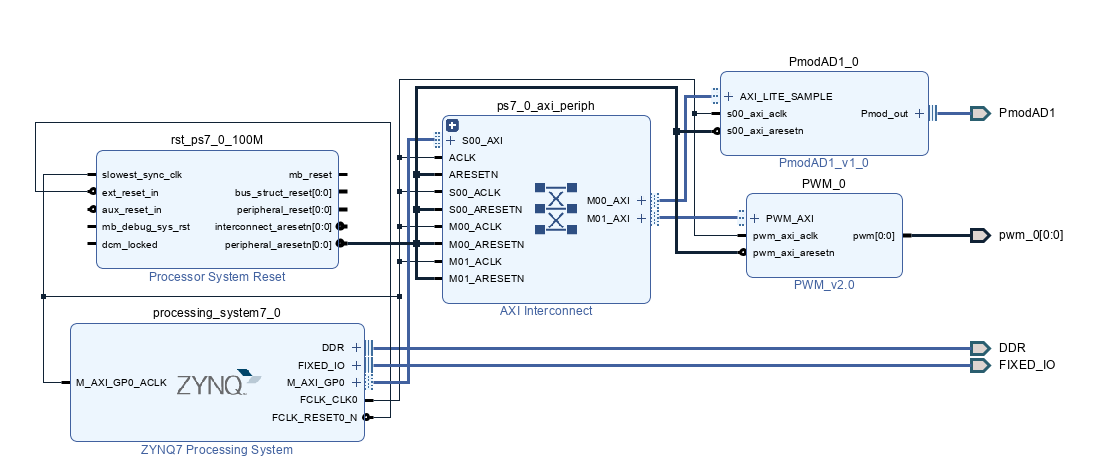

I am currently using a PmodAD1 with code in Vitis as an ADC. The code reads the digital value obtained by the Pmod and writes it to the serial monitor. I intend to utilize this value to generate a PWM signal, with the duty cycle adjusting according to the input changes. The Pmod is currently operational, and I can generate a PWM signal in Verilog in separate projects. Modifying the duty cycle in the PWM Verilog code requires regenerating a bitstream and reprogramming the device each time. How can I integrate these components to have the PWM automatically update based on the Pmod's input? I am a student and would appreciate any advice. Thanks

My block design:

My Verilog Code: