Hi,

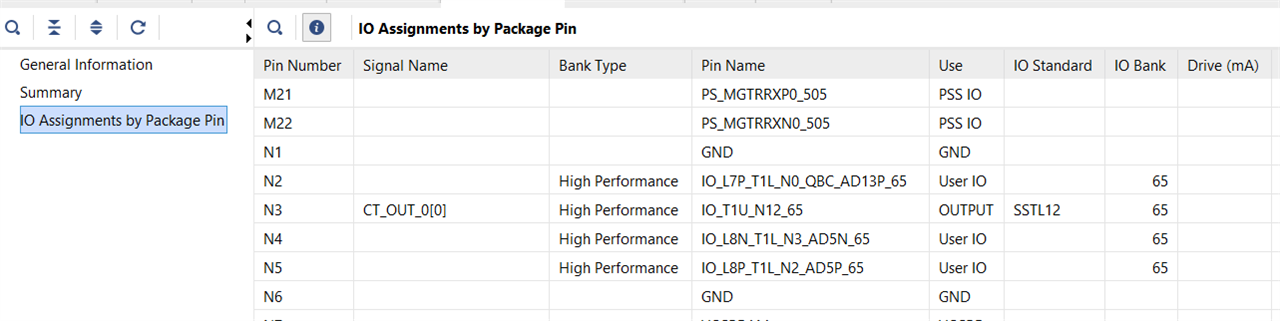

I am using AVNET ZUBoard 1CG and trying to figure out the pins compatible with I/O standard SSTL12 and i found J6 supports the standard, but when i try in vivado .xdc file making a pin SSTL12, its throwing error at bitstream.

Please help me to find out the proper IO that supports SSTL12.

Below is the command i used.

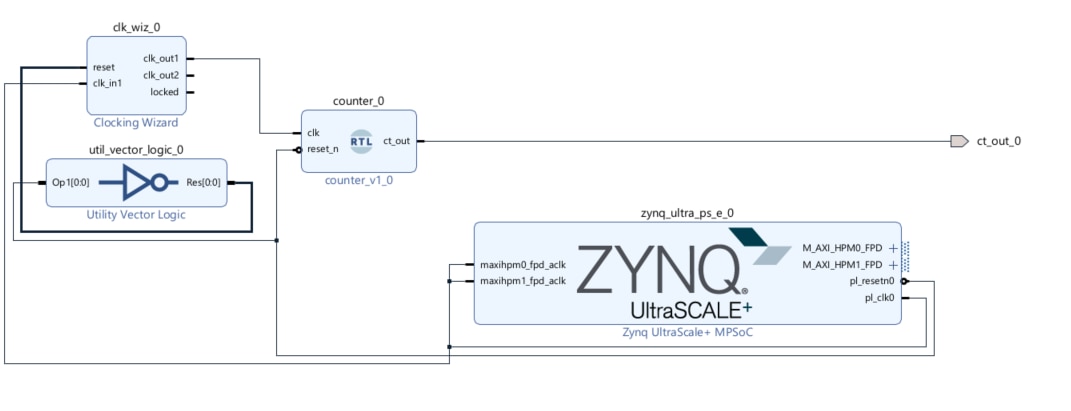

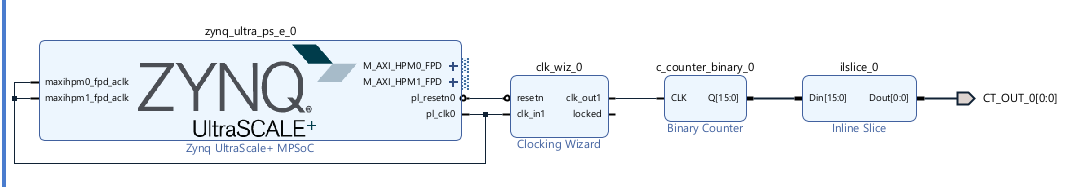

set_property PACKAGE_PIN N3 [ct_out_0]

set_property IOSTANDARD SSTL12 [ct_out_0]

Thanks,

Nirupama.T