11. Diodes

The recirculating diode for the main output (D1) and the output diode for the secondary (D2) are selected by calculating the average current carried and multiplying by the forward voltage to determine the power dissipation. The diode package is then selected based upon control of the temperature. Schottky diodes are preferred whenever they are available for their low forward voltage and near-zero reverse recovery charge, two features which combine to make them more efficient and less electrically noisy than PN diodes. For safety and margin when dealing with noise and transients, the reverse blocking voltage of the diodes should be selected at least 20% above the highest voltage in the system, which is VIN-MAX for bucks and coupled bucks. 20% above 14V is 16,8 V, hence 20 V or higher rated diodes will be used. Power dissipation is determined by the following equations:

The industry standard SMA package with a typical thermal resistance of 95ºC/W is a cost-effective choice, and 20V rated devices are available from many different manufacturers.

12. Control Loop Compensation

Peak Current Mode control (PCM) is a good choice for controlling a buck using coupled inductors for several reasons. When properly designed this control method simplifies the design of the compensation of the error amplifier. As the name implies, PCM also controls peak current in the inductor (in this case in the primary winding) naturally and on a cycle-by-cycle basis. Adding a second winding and a second load to a buck converter changes the control-to-output transfer function of the power stage, comprised of the duty cycle modulator and the output filter. The basic goal of compensating the control loop stays the same, however this is a high gain at DC (for best tolerance of the main output voltage), a high bandwidth (for fast response to load transients) and a high phase margin (for stable response to load and line transients.) There are many design philosophies for compensating control loops, and this application note will focus on a basic method that provides a conservative design that is very stable.

13. Defining the Power Stage

The inputs that are needed to develop a linear, small-signal model of the power stage of a 1:1 coupled buck regulator are as listed along with their values for this design example:

VIN-MIN = 10 V VOUT = 5,0 V IO = IO1-MAX + IO2-MAX = 0,5 A + 0,2 A = 0,7 A fSW = 500 kHz L1 = 47 μH

Power Stage Resistance, RL = RDSON of control MOSFET + DCR per winding of L1 = 200 + 600 = 800 mΩ

Total Output Capacitance, CO = CO1 + CO2 = 220 μF + 16 μF = 236 μF

ESR of Output Capacitors, RC = 40 mΩ Current Sense Resistance, RSN = 167 mΩ

Current Sense Gain, GI = 1 Reference Voltage, VFB = 0,8 V Maximum Duty Cycle, DMAX = 0,52

Load Resistance, RO = VOUT / IO Slope Compensation Ramp, VM = 0,417 V

The slope compensation ramp is used to correct for the error between the current at the point in time when it is sensed (at its peak) and the average value of that current. Without this additional slope, PCM switching converters exhibit a sub-harmonic oscillation for duty cycles of 50 % and above. Because the inductor ripple current is higher in a coupled buck than in a normal buck, a higher slope compensation ramp is needed. Very few buck control ICs allow this ramp to be adjusted, hence it is important to evaluate the ideal slope compensation ramp to foresee any possible problems.

For PCM the ideal compensation ramp is equal to the slope of the current during the off-time of the control FET. For simplicity it is assumed that the waveform is a triangle wave, but having the same peak-peak value as the actual trapezoid wave of ∆iP. The ideal compensation slope is then:

The fixed ramp of 0,417 V used in the TPS54160 is higher than the ideal ramp, eliminating the danger of sub harmonic oscillation in this example. It should be noted that VM cannot be made too high without consequences – if its value is far greater than the actual sensed slope, the converter becomes more of a voltage mode type and requires more careful compensation around the error amplifier to ensure an adequate phase margin. VL1EFF is used to correct for the difference between the slope of the triangular waveform of inductor current in a standard buck and the trapezoidal waveform of the inductor current in a coupled buck.

AFB is the gain reduction that comes from the output divider resistors. KM is the modulator gain, representing the balance between the sensed current slope (the first term in the denominator) and the compensation slope (second term in the denominator.)

The DC gain of the power stage APS can be defined as follows:

The frequency-dependent terms of the power stage are the load pole ωC , the ESR zero ωZ, and the doublepole derived from the sampling function of the inductor current with corner frequency ωL.

The control-to-output transfer function can now be written in the LaPlace domain:

The control-to-output transfer function can now be written in the LaPlace domain:

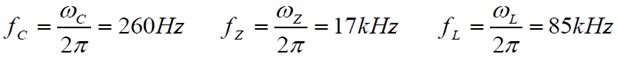

The frequencies in Hertz of the poles and zero are calculated by dividing each in term in radians/sec by (2π):

Plotting gain and phase graphically provides an intuitive way to place the gain and phase response needed for the error amplifier. Figure 6 shows the gain of GPS (s):

|

Figure 6: Power Stage Gain and Phase

From a graphical perspective, the goal of error amplifier compensation is to create a complete control loop gain that starts at a high level and rolls off at a slope of -20 dB/decade. The bandwidth or “crossover frequency” is defined as the point where the overall loop gain equals 0 dB, and in general bandwidth is made as high as possible while still maintaining a high phase margin. Phase margin turn is defined as the difference between the phase of the loop when gain equals zero dB and -360 º, the point at which the negative feedback becomes positive and implies an unstable control loop. (In practice the result is usually an unstable duty cycle and fluctuations of the output voltage.) A minimum phase margin of 45 º will ensure a transient response with little or no overshoot or oscillation while still allowing the bandwidth to be as much as 1/5 th of the switching frequency. In theory the bandwidth could be as much as 1/2 of the switching frequency, but in practice 1/5th is a good upper limit.

In this example the compensation will be Type II, consisting of a pole at 0 Hz to ensure high DC gain at low frequencies, one pole whose frequency can be set arbitrarily and a zero whose frequency can also be set as desired. A good starting point is to set the compensation zero frequency fZ1 equal to the load pole fC and to set the compensation pole frequency fP1 equal to the ESR zero frequency fZ. The compensator pole and zero effectively cancel the power stage zero and pole, leaving only the pole at the origin, and in this way the high gain and continuous -20 dB/decade slope is maintained up until the sampling double pole frequency. The remaining variable to be determined is the gain of the compensation between fZ1 and fP1, often called the “mid-band gain”. A good way to start is to set the overall control loop to cross 0 dB and define the bandwidth in this area of flat gain. This can be done by finding the gain of the power stage at the desired crossover frequency and then setting the gain of compensation to be equal in magnitude but opposite in sign, thus forcing the overall bandwidth to be zero at that point. The TPS54160 uses a transconductance error amplifier along with two external capacitors and one external resistor to set the poles, zero, and mid-band gain. Figure 7 shows the error amplifier and the external components:

Figure 7: Transconductance Error Amplifier

The transconductance of the error amplifier can be read from the datasheet of the control IC, and for the TPS54160 this is gM = 97 μS. The mid-band gain, pole and zero frequencies are as follows:

Referring to Figure 6, the gain of GPS(S) at a conservative 1/10th of the switching frequency, or 50 kHz, is around -14 dB. Here there is one detail that is sometimes overlooked – the gain reduction from the feedback divider resistors, AFB, defined in EQ.25. This term can be summed with the power stage or with the error amplifier – it makes no difference once the loop is closed. This example assumes that AFB is part of the error amplifier, and since it is a DC gain, it affects the mid-band gain:

Now that mid-band gain has been calculated, R1, C1 and C2 can be calculated:

The closest 1 % resistor value is 316 k and the closest 10 % capacitor values are 1,8 nF and 27 pF, respectively. These are substituted into the compensation transfer function:

Figure 8 shows the gain and phase of the error amplifier:

|

Figure 8: Error Amp Gain and Phase

The final step is to close the loop by multiplying the power stage and error amplifier transfer functions together. The final gain plot shows bandwidth and the final phase plot shows the phase margin:

|  |

Figure 9: Overall Control Loop Gain and Phase

The actual bandwidth is 20 kHz and the phase margin 79 º, indicating a somewhat slow but very stable control loop. The reason bandwidth and phase margin don´t match the predictions perfectly is the relatively low frequency of the compensation pole. This is typical for converters using output capacitors with high ESR such as aluminum electrolytic and tantalum. The frequency of the compensation pole can be increased up to ½ of the switching frequency if desired. In fact, for converters with purely ceramic output capacitors the ESR zero frequency is typically in the MHz range, and in such cases ½ of the switching frequency is the recommended compensation pole frequency. Increasing the mid-band gain and/or increasing the compensation pole frequency will increase the control loop bandwidth, but will also decrease the phase margin. Several iterations of incrementing the bandwidth and monitoring the phase margin can be performed until phase margin has dropped to 45 º, at which point the maximum recommended bandwidth is reached.

14. L-C Input Filter with Damping

Buck converters, buck-boost converters and flyback converters are the three principal topologies that draw a discontinuous current from the input source. Even with good quality input capacitors to supply the heavy AC current, the source will supply some current at AC, and the result is conducted electromagnetic interference (EMI) on the input lines. The longer the leads, PCB traces and wiring harnesses that connect these high ripple DC-DC converters to their input sources, the more likely that this conducted EMI also becomes radiated EMI owing to the unwanted antenna behavior of the leads. An input L-C filter placed close to the DC-DC converter is a good way to reduce conducted EMI, and by filtering before the noise can “contaminate” the input leads, radiated EMI is reduced as well.

Not every laboratory has access to dedicated equipment for measuring and testing conducted EMI, let alone the special antennas and anechoic chambers needed for radiated EMI. The following procedure is based upon correlation of time-domain current waveforms that can be predicted and measured with a common oscilloscope to differential-mode conducted noise in the frequency domain.

15. Estimating Noise Amplitude

The following equation can be used to estimate the amplitude of the first harmonic of the differential mode conducted noise based upon the input current waveform:

Figure 10 shows the input current of the example circuit during maximum load and minimum input voltage – the worst-case for EMI.

Figure 10: Primary switch node (yellow), vIN (AC-coupled, blue), IIN (pink)

VIN = 10V, IO1 = 500 mA, IO2 = 180 mA

Average input current, or the average height of the pedestals of trapezoid wave input current can be calculated as:

Maximum duty cycle was defined in EQ.5 as 0,54, and the average current is then 0,37 / 0,54 = 0,68 A. The total input capacitance CIN is 7 μF. The estimated noise of the first harmonic is:

The limit for average common mode noise in many standards for conducted EMC, e.g.: IEC55022 in the range of 500 kHz is 45 dB, hence the attenuation needed is equal to the noise A1ST minus this limit. For this example the required attenuation is then ATT = 86 – 45 = 41 dBμV.

16. Selecting L and C

Either the inductance or the capacitance of the input filter must be chosen arbitrarily, and for this example it is the inductance that will be chosen first. Values of inductance between 1 and 10 μH provide a good compromise between size, cost, and the resulting resonant frequency of the input L-C filter. The RMS current rating of the inductor must be greater than the input current IIN, and the peak current rating must be higher than the sum of the average current and one-half of the AC ripple:

The Würth Elektronik WE-TPC 2828 series 744 025 002 is a shielded 2,2 μH device in a small footprint (2,8 x 2,8 x 2,8 mm) with a DCR of 60 mΩ and current ratings of IRMS = 1,8 A and ISAT = 2,4 A that is well suited for this example. With inductance chosen, two equations exist for selecting the required capacitance. The first is based upon the resonant frequency of the filter, which should be kept to 1/10th of the switching frequency or less:

The result of EQ.41 may be negative – this would indicate that with the chosen inductor value it is not possible to attain a filter resonance frequency 10x lower than the switching frequency. The inductor value can be increased if desired, though this comes at a penalty of lower efficiency and/or a larger inductor due to the higher DCR and higher core losses that accompany higher inductance. Setting resonant frequency 10x below switching frequency is a guideline, not a hard limit.

The second equation is a hard limit, and it predicts the minimum capacitance needed to ensure that the voltage ripple at the input to the converter is below the limit set by ATT:

The capacitor chosen should be greater than the larger of the two values given by CF-MIN1 and CF-MIN2, and multi-layer ceramic capacitors are the best choice. When using MLCCs the loss in capacitance due to a DC voltage bias must be taken into account. Depending upon the case size and voltage rating it would likely take two or more 10 μF capacitors in parallel to provide a true 14 μF or more of capacitance. Before selecting the final value for CF, however, the damping of the input filter must be considered.

17. Filter Damping

Any time an L-C filter feeds into a switching regulator the potential exists for an oscillation (often called “ringing” or also “power supply interaction”) stemming from the output impedance of the filter and the input impedance of the switcher. Properly designed switchers maintain high power efficiency over a range of input voltage, and one effect of this is that as input voltage rises, input current decreases, and vice-versa. The result is effective negative input impedance. If |-ZIN| is less than or equal to ZOUT of the L-C filter, the input line is likely to oscillate, a behavior that is never beneficial. Even in the absence of an input inductor, the input leads have a parasitic inductance, and when switchers use purely MLCC input capacitors with their very low ESR the potential for oscillation is very real. In this example there is a discrete inductor whose inductance and DCR are both known. With these quantities a damping capacitor CD can be selected to go in parallel with CIN, shown in figure 11.

Figure 11: L-C filter with damping capacitor

Besides stopping any oscillations, CD reduces the ripple voltage at the input, lowering the amplitude of A1ST and ATT, and in turn reducing the capacitance needed for CF. The following two equations define the minimum capacitance and the minimum ESR needed for CD to critically damp the filter formed by LF and CIN:

A negative value for the ESR would indicate that the inductor DCR already provides enough damping resistance. The typical choice for CD is an aluminum electrolytic capacitor. Surface mount aluminum capacitors rated to 16 V or 25 V with 33 μF are available at reasonable cost from many different manufacturers. What´s more, for damping the normally “bad” characteristic, high ESR, is actually helpful. A surface mount aluminum electrolytic capacitor rated at 25 V provides 33 μF with an ESR of 0,34 in a compact 6,3 mm radius footprint, or Radial D8 Case.

18. Re-evaluate CF

The total capacitance of CIN is now equal to (7 μF + 33 μF), so another iteration of the filter capacitor design is needed. For simplicity the results will simply be stated: the final CF value needed is 5,2 μF. Another 25 V rated, nominal 10 μF MLCC identical to CIN will be used, and since the DC bias is the same, this capacitor will provide at least 7 μF of capacitance.

19. Conclusion

Using a coupled inductor can help derive a second output voltage without the cost of another complete switching power supply, but the tolerance of the secondary output voltage and the DCM threshold in the primary are difficult to predict with pure mathematical expressions. Successful 1:1 coupled buck designs should be lab tested thoroughly, over line, load and temperature. In most cases the secondary output voltage tolerance is too wide, line regulation too high and load regulation too high to be used directly. For all of these reasons a linear regulator is the recommended way to provide a well-regulated secondary output.

20. Graphs and Oscilloscope Captures

Figure 12: Steady State Waveforms. IO1 = 500 mA, IO2 = 100 mA

Ch.1 = Primary SW, Ch.2 = VOUT1 AC-coupled, Ch.3 = Secondary SW, Ch.4 = VOUT2 AC-coupled

Figure 13: Load Transient on Primary. IO1 varies from 200 to 500 mA, IO2 = 100 mA

Ch.2 = VOUT1 AC-coupled, Ch.3 = IO1, Ch.4 = VOUT2 AC-coupled

Figure 14: Load Transient on Secondary. IO1 = 500 mA, IO2 varies from 50 to 100 mA

Ch.2 = VOUT1 AC-coupled, Ch.3 = IO1, Ch.4 = VOUT2 AC-coupled

|

Power Efficiency, IO2 = 25 mA Power Efficiency, IO2 = 50 mA

|

Power Efficiency, IO2 = 100 mA Power Efficiency, IO2 = 200 mA

21. Complete Circuit Schematic

22. Bill of Materials

IMPORTANT NOTICE

Würth Elektronik eiSos GmbH & Co. KG and its subsidiaries and affiliates (WE) assume no liability for application assistance of any kind. Customers may use WE’s assistance and product recommendations for their applications and design. The responsibility for the applicability and use of WE Products in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not. Customers are cautioned to verify that data sheets are current. The current data sheets can be downloaded at www.weonline. com. Customers shall strictly observe any product-specific notes, cautions and warnings. WE reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services. WE does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which WE products or services are used. Information published by WE regarding third-party products or services does not constitute a license from WE to use such products or services or a warranty or endorsement thereof. WE products are not authorized for use in safety-critical applications (such as life support). It has to be clearly pointed out that the possibility of a malfunction of electronic components or failure before the end of the usual lifetime cannot be completely eliminated in the current state of the art, even if the products are operated within the range of the specifications. In certain customer applications requiring a very high level of safety and in which the malfunction or failure of an electronic component could endanger human life or health Customers must ensure that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of WE products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by WE. Further, Customers shall fully indemnify WE against any damages arising out of the use of WE products in such safety-critical applications. WE products are neither designed nor intended for use in automotive applications or environments unless the specific WE products are designated by WE as compliant with ISO/TS 16949 requirements. Customers acknowledge and agree that, if they use any non-designated products in automotive applications, WE will not be responsible for any failure to meet such requirements.

USEFUL LINKS

Application Notes:http://www.we-online.com/app-notes

Component Selector:http://www.we-online.com/component-selector

Toolbox:http://www.we-online.com/toolbox

Product Catalog:http://katalog.we-online.de/en/

DIRECT LINK

ANP017: Designing low-cost, multiple output DC/DC converters

CONTACTINFORMATION

Würth Elektronik eiSos GmbH & Co. KG

Max-Eyth-Str. 1, 74638 Waldenburg, Germany

Tel.: +49 (0) 7942 / 945 – 0

Email: appnotes@we-online.de