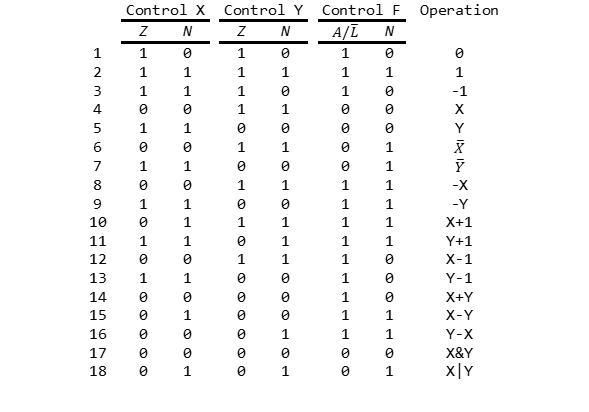

The main idea is take a basic CPU to implement in the FPGA. Nowadays, there are some advanced CPU to develop a system like MIPS, ARM, RISC V, Microblaze and so on. Despite the availability of this components, the concept could be obscure for undergraduates or people that want understand the computer architecture. For these reasons, there is a small CPU called HACK. This CPU, developed in the NAND to Tetris courseware, has the following Instuction Set Architecture (ISA)

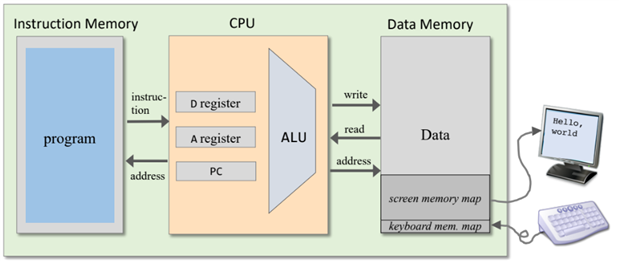

This ISA could be limited or incomplete for actual processors because there are instructions like load immediate, add immediate, rigth shift and more advanced. But for understanding purposes, we will find this ISA useful to implement small assembly programs with the author's provided tools. At this point, the ISA metion which instructions will be executed in the processor, but trere is not information about how the instructions are implemented still. The basic HACK Computer System has program memory, data memory, processor and the peripheral memory map. According to courseware, available in https://www.nand2tetris.org/course, the following diagram illustrates the abstract implementation of this system.

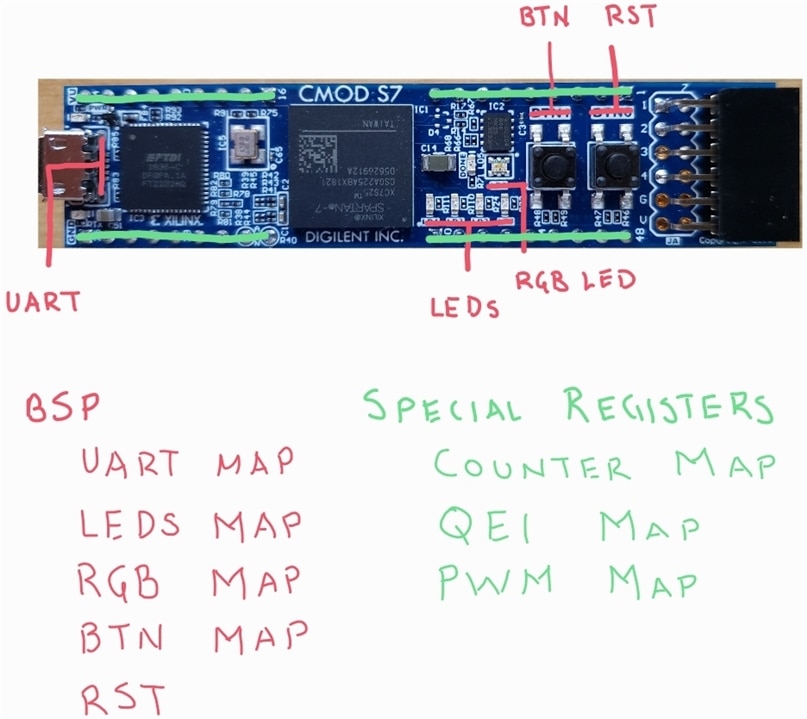

The processor, in my opinion, solve all that problems that could be not defined by Hardware or the Hardware resources are limited. Let's consider the Floating-Point operations, the processor consider the IEEE-754 to synthetize the number arithmetics but it will take a lot of clock cycles compared with the Hardware implementations. Both solutions are good, but time restrictions must be accomplish in some applications.The Hardware solution depends only in the processors data transfer, requiring some clock cycles according to hardware approaches. Finally, Board Support Package (BSP) and Special Registers (SR) will be added to the implementation to add peripherals as co-processors in some tasks like PWM and Counters.

Some of the interfacing components that will be considered for the BSP and Interfacing are the following:

Some of them cannot be configured with only one register or could be confusing package the configuration and data bits in the same register. Consequently, a Memory Map is needed to configure and share data with the peripherals.

All the above is a brief of what are the challenges to implement a CPU with peripheral support. At the end of the challenge, we will obtain a tiny microcontroller.

-

michaelkellett

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

-

pandoramc

in reply to michaelkellett

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Comment-

pandoramc

in reply to michaelkellett

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Children