As you know SD Cards are bigger Divas than me! With latencies of up to several hundreds of milliseconds and the complexity of a file they can be trying to deal with at times. Not to mention, I don’t usually need gigabytes of storage.

Today there are so many memory chips with a simple SPI interface available. You can get several megabytes of flash/f-ram/psram in an 8-pin package for a dollar or two.

So, I am just trying to learn more about these QSPI memory chips.

I guess the best place to start is by probing known working designs, like the many RP2040 development boards like the RPI Pico or Adafruit’s RP2040 feather.

When the RP2040 comes out of reset it begins execution of its internal bootrom code:

https://github.com/raspberrypi/pico-bootrom/blob/master/bootrom/bootrom_main.c

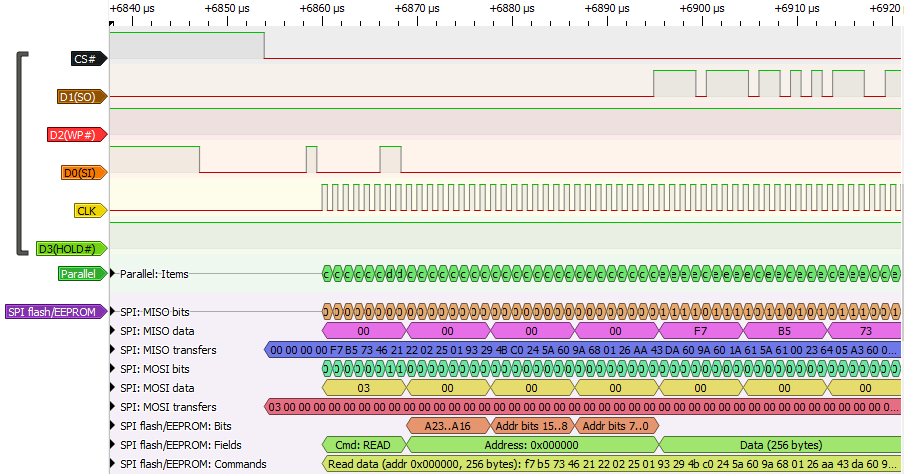

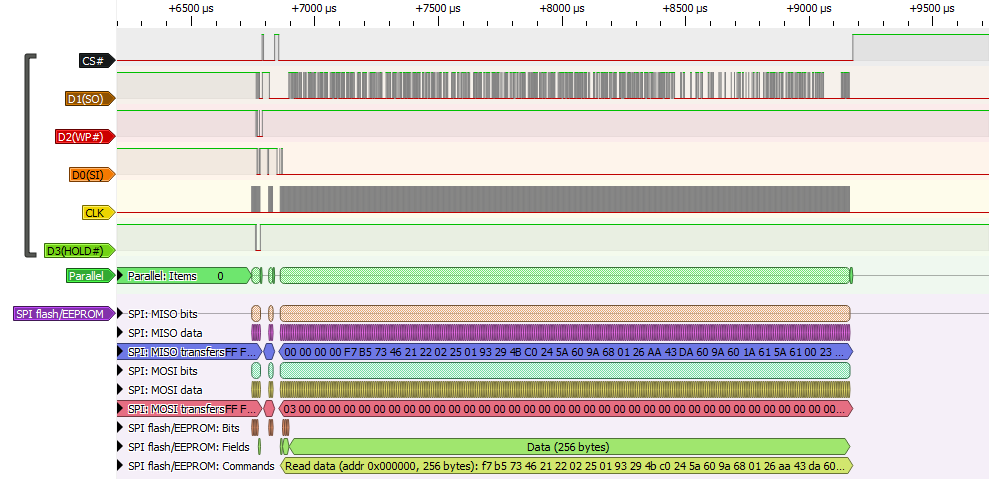

Where it tries to initialize an SPI memory IC over its SSI interface. It does this by trying to read the first 256 bytes with different CPOL CPHA combinations and looking for a valid second stage bootloader image.

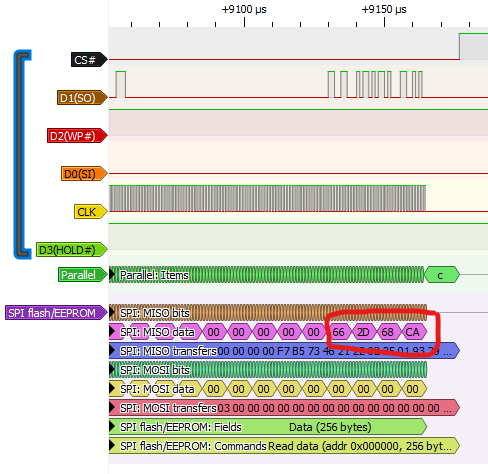

The last 4 bytes of the 256 byte page are a checksum that the Rp2040 uses to validate that a second stage boot image was found.

The RP2040 starts executing the loaded second stage bootloader image and eventually gets ready to start running of external flash.

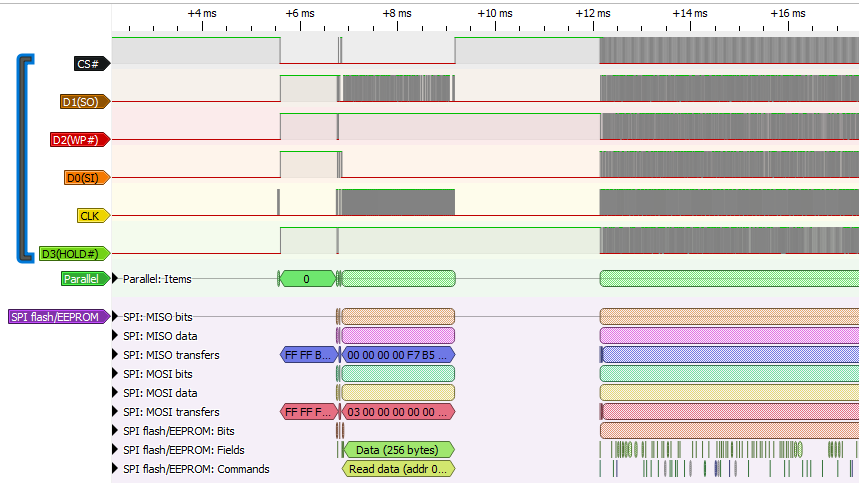

Just before switching over from the 1-bit xx25 interface to QuadSPI the firmware reads status register 2:

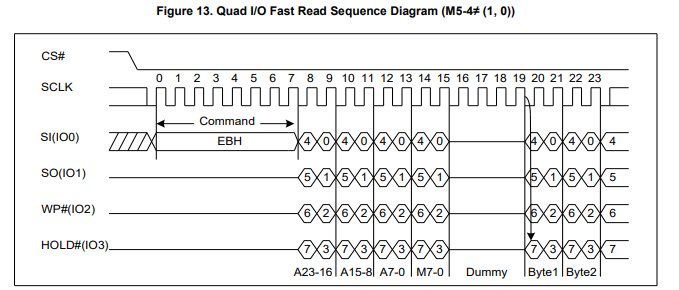

To switch over to using “Quad I/O Fast Read with Continuous Read Mode” The 0xEB command is sent:

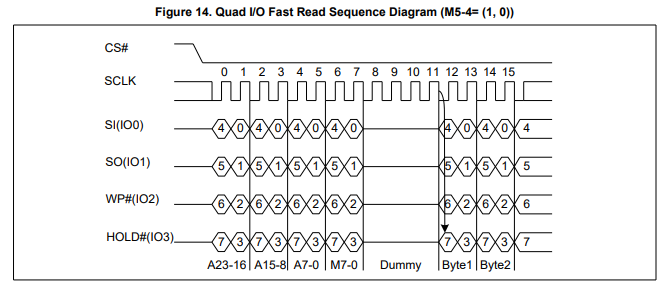

With command bits M5-4 = (1,0) subsequent flash reads can omit the command portion:

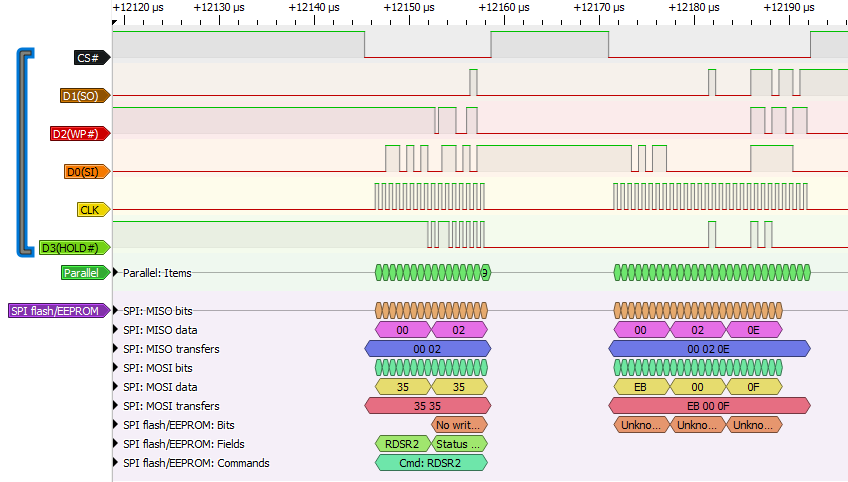

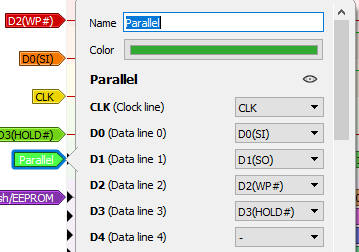

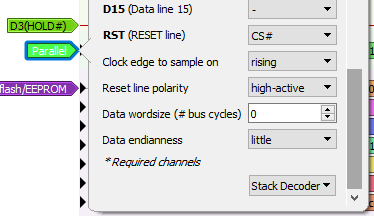

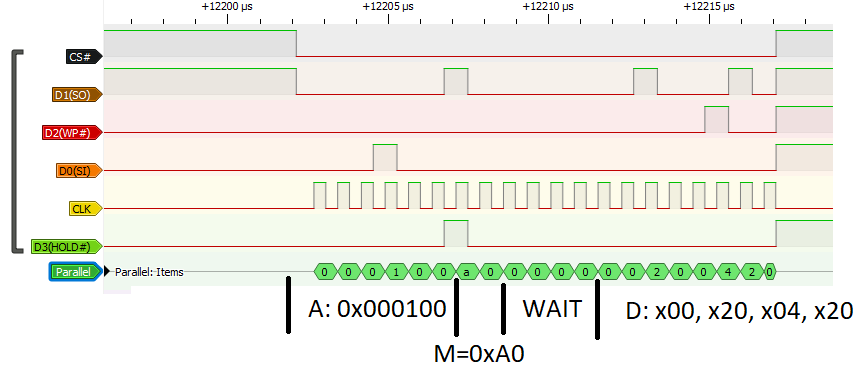

The unfortunate part for me is, I don’t have a QSPI protocol decoder (though it appears neither does a $20,000 oscilloscope *shakes head*). Using a clocked parallel bus decoder gets me close enough I suppose:

It isn’t too difficult to follow along:

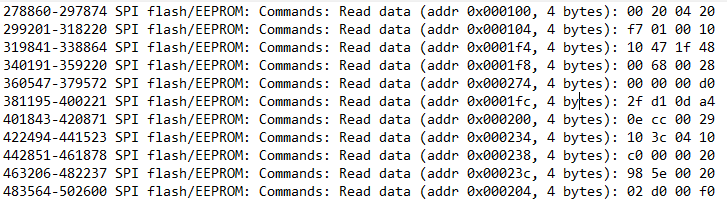

For some reason micropython compiled for an Adafruit feather never switches over to QSPI, So in that case I get a nice tabular report using a SPI memory protocol decoder:

It is looking quite likely I might be able to boot an RP2040 off an 8MB PSRAM chip in 1-bit SPI mode.

I don’t know enough yet to know how common the QuadIO mode commands and wait cycle counts are between chips.

Thanks for reading

Onwards and upwards!