Hello,

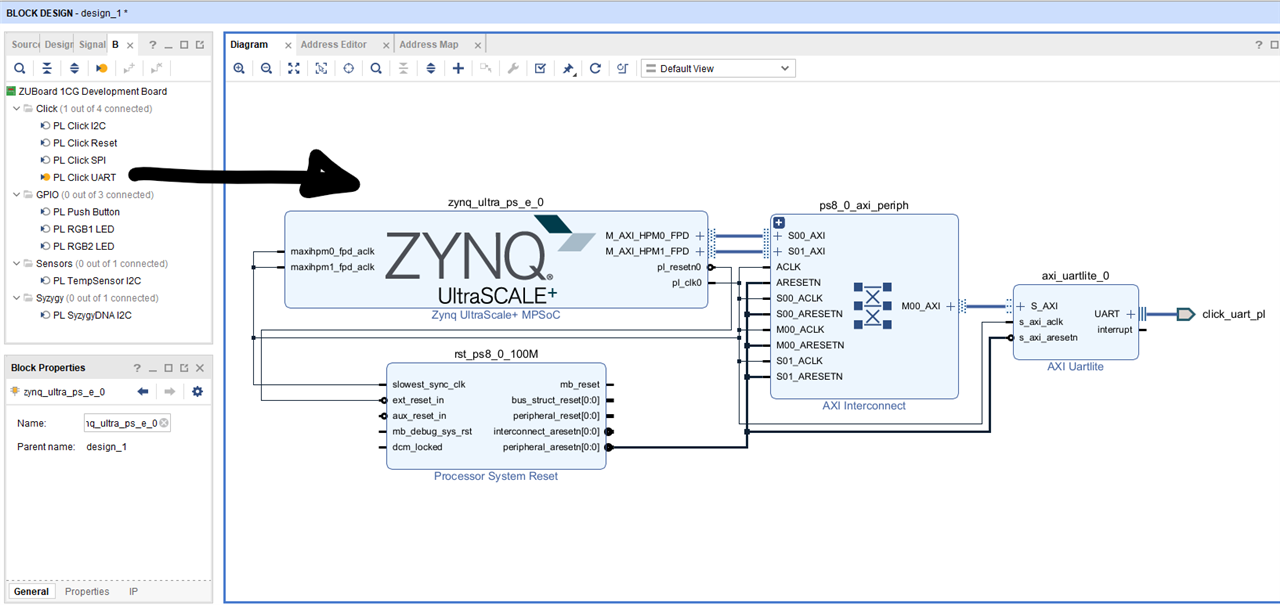

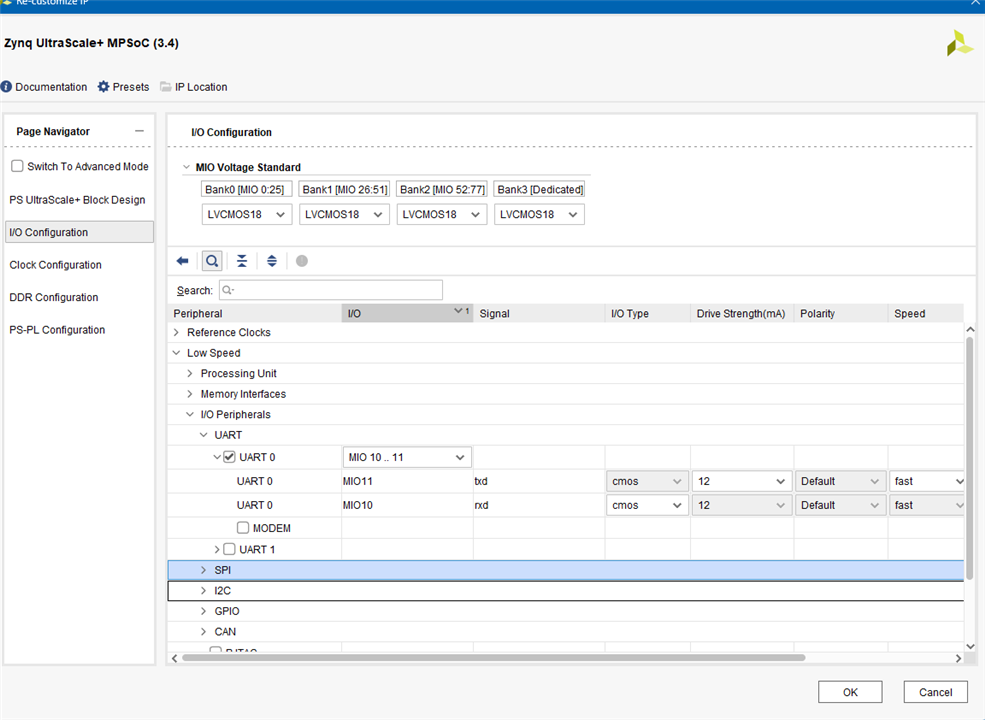

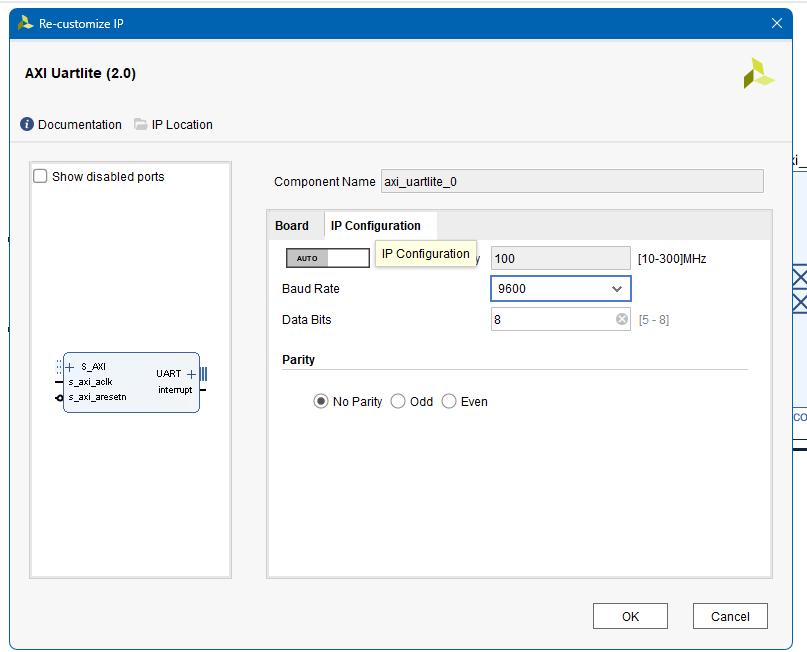

I am creating a custom IP for a UART for my ZuBoard 1CG. I am not sure how to complete the AXI4 files both the wrapper and the slave file. I have looked for guides and none have helped me. I tried the ZuBoard training and that did not help either. Does anyone have any examples? or any guides to help me please?

Thank you