1. Minized Synth I Introduction

|

|

In a music studio, a newbie synth designer is given a complex sound synthesizer and told to bring out the sound of a 'Grand Piano' using subtractive synthesis. After some tweaking, all that's left is a basic sine wave. The senior sound engineer asks, "Is it done?" The newbie grins and says, "Don't worry, if the 'Grand Piano' is in there, I'll bring it out with subtractive synthesis!" Image generated with comicsmaker.ai |

The joke is my adaptation of a joke in Spanish in which a cabinetmaker's apprentice is commissioned to try to extract a "San José" from a piece of wood and when he barely has a splinter left he exclaims that if the "San José" is inside from the billet of wood it will come out at any moment. Subtractive synthesis is about, sculpting a sound starting from a sound full of harmonics through filtering and envelopes.

One of the primary forms of synthesis is subtractive synthesis. This technique involves removing undesirable frequencies to create the desired sound. It operates under the assumption that a basic oscillator can produce waveforms with varying frequency spectrums that mimic the sound of an acoustic instrument. The signal then passes through a filter that compensates for the frequency-dependent losses and resonances in the body of the instrument. The amplifier section of the synthesizer shapes the filtered (or unfiltered) signal over time.

MiniZed Synth I

As part of my "Path to Programmable III Program" final project, I selected DSP from the Core Technology Path. My project involved creating a digital version of a classic analog synthesizer from the 1960s, which utilized the AVNET MiniZed development board. This board is powered by an AMD Zynq 7Z007S single-core development board, which contains an "All Programmable System-On-Chip" (APSoC) that integrates most computer components into one chip. Additionally, it includes FPGA technology that can be utilized.

AVNET MiniZed Development Board. The AMD Zynq 7Z007S (Formerly Xilinx Zynq) chip is in the center with the sticker on it.

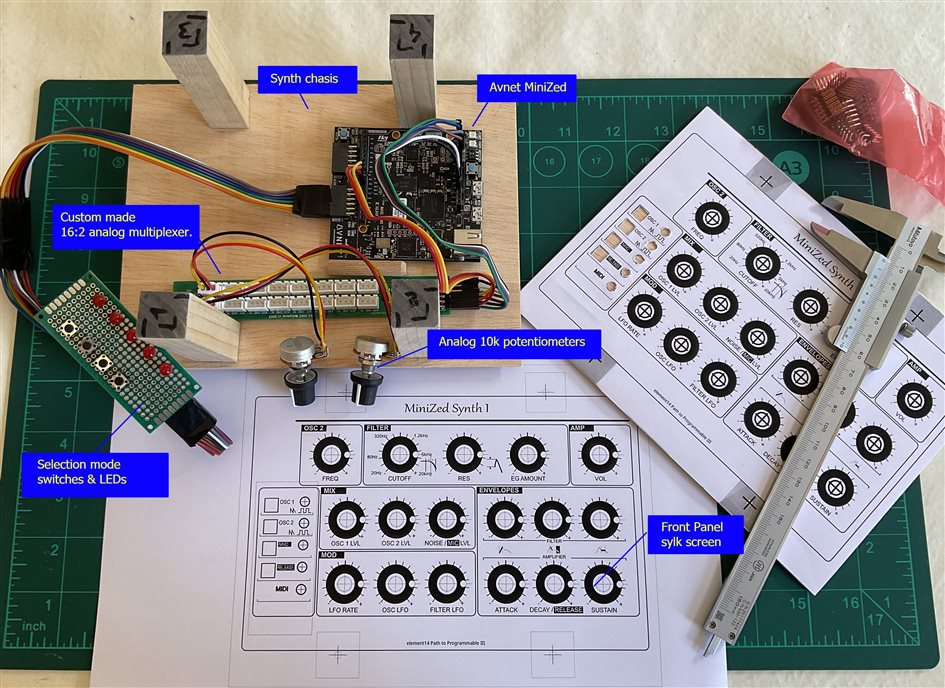

During the project, several extension boards to the MiniZed board have been designed and built:

- A sound editing panel with 17 analog potentiometers,

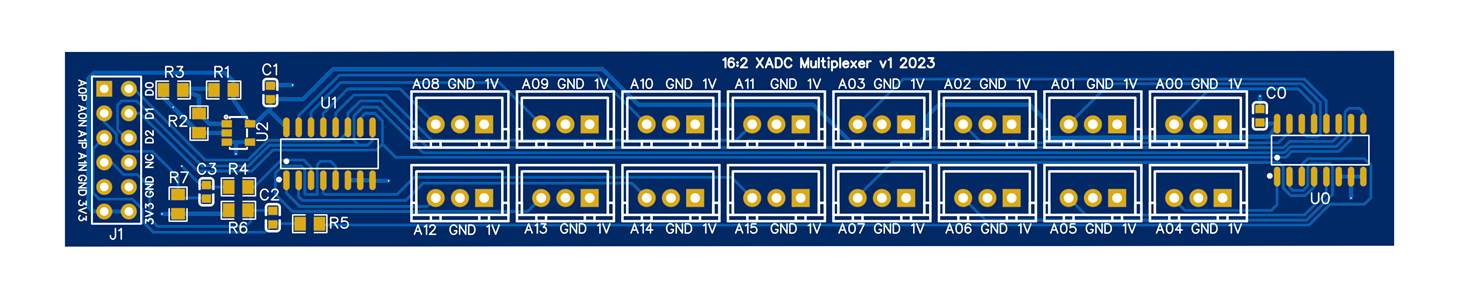

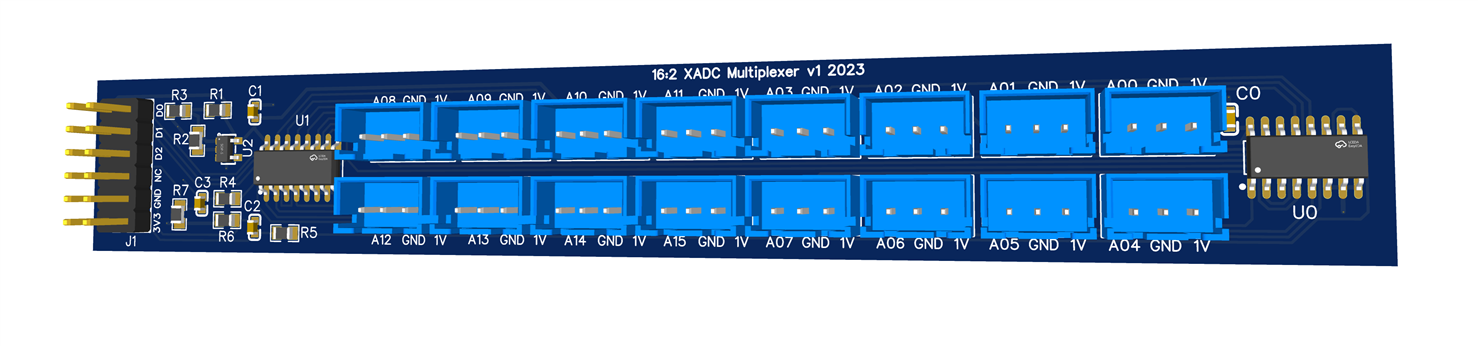

- a board with an external analog multiplexer from 2 to 16 channels,

- an extension board with user buttons and indicator LEDs.

- a low-pass filter board for digital-to-analog conversion with an analog audio amplifier

- and a MIDI interface board, this last is designed but not yet built pending receipt of PCBs.

The majority of the work on this project was accomplished using SystemVerilog, a language for describing and verifying hardware used in the creation, design, simulation, testing, and implementation of electronic systems. The MiniZed development board features an AMD Zynq chip, which includes both a microcontroller and a network of Field Programmable Gate Arrays (FPGAs). These FPGAs are semiconductor devices made up of configurable logic blocks (CLBs) that are connected through programmable interconnects. As a result, FPGAs can be reprogrammed after manufacturing to meet specific application or functionality needs. AMD provides a development tool called VIVADO ML that allows the hardware description language to be translated into an interconnect configuration file for the FPGA fabric.

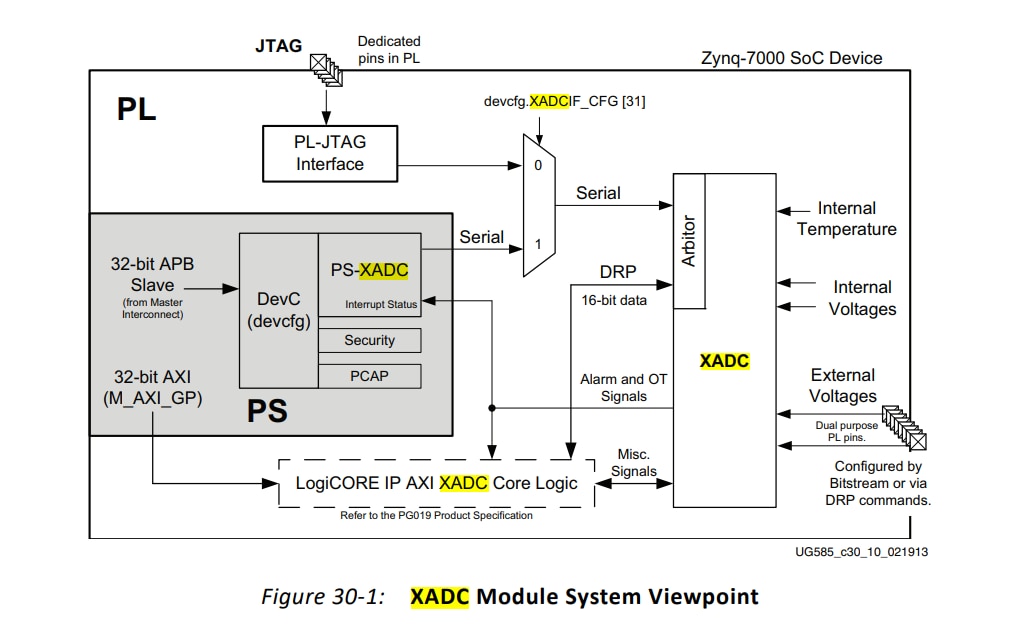

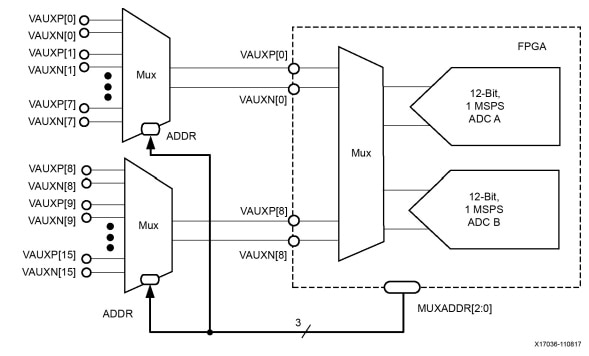

Throughout the past five blog posts, I have been documenting the necessary research and learning required for the successful completion of this project. The blogs covered various aspects such as hardware and software development flow, interfaces and ports of the AVNET Minized development board, and the development of IP blocks in Zynq's FPGA fabric programmable logic for the Vivado development tool. These IP blocks are like Lego pieces that allow bundling and reuse, and there was also a focus on the use of digital filters and hardware-accelerated conversion between Pulse Coded Modulation and Pulse Density Modulation formats. One of the blogs was dedicated to designing an external multiplexer for the Zynq XADC Analog Digital Converter, which is now also a part of the Minized Synth I. At the end of this blog post, you can find references to all the previous posts.

2. Index

Table of Contents

- 1. Minized Synth I Introduction

- 2. Index

- 3. Minized Synth I: Overview and Features

- 4. High-Level Design

- 5. Hardware Accelerated Synth Module IP

- 5.1. Custom Synth Module AXI4 Lite Peripheral IP

- 5.2. What's under the hood of the Synth module?

- 5.3. Oscillators

- 5.4. Sine Wave Generator

- 5.5. Noise Generator Module

- 5.6. Square Wave Generator

- 5.7. Triangle Wave Generator

- 5.8. Saw-Tooth Wave Generator Module

- 5.9. Attack-Decay-Sustain-Release (ADSR) Envelope Modulation

- 5.10. One-bit delta-sigma DAC

- 5.11. Mixer Module

- 5.12. Filter Module

- 5.13. Amplifier Module

- 5.14 Low Frequency Oscillator. Pitch Frequency Modulation

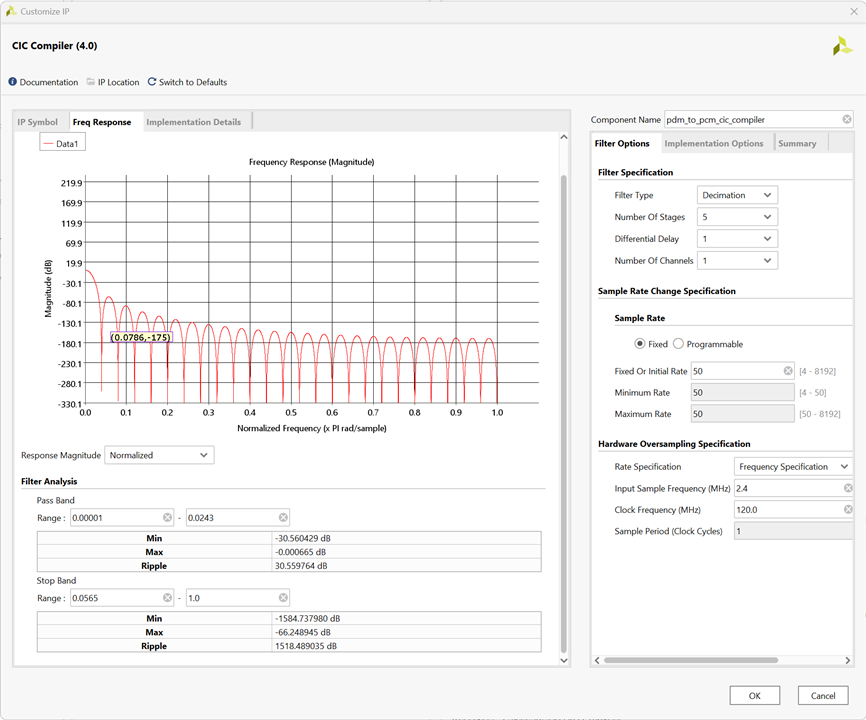

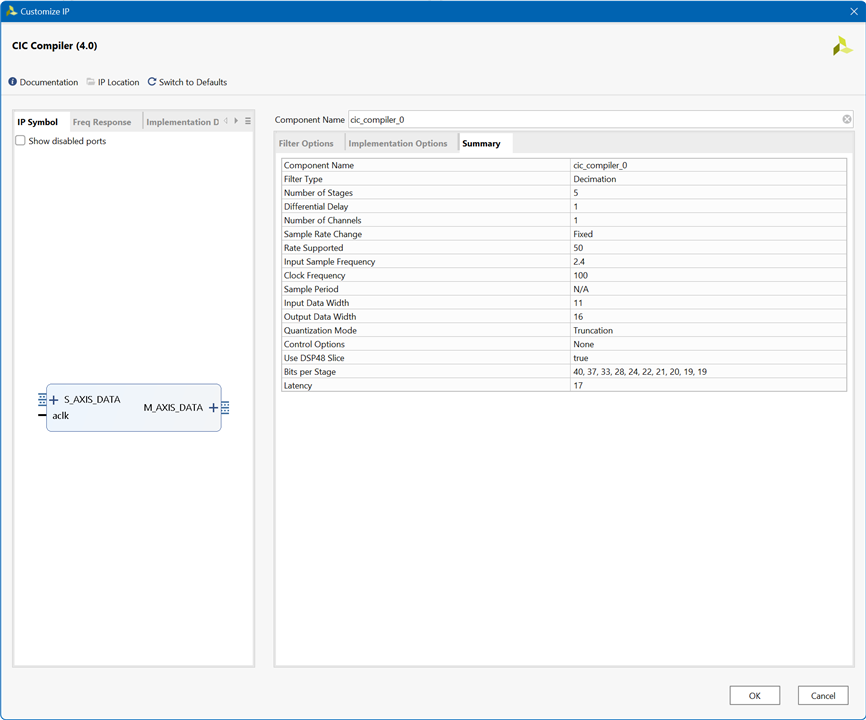

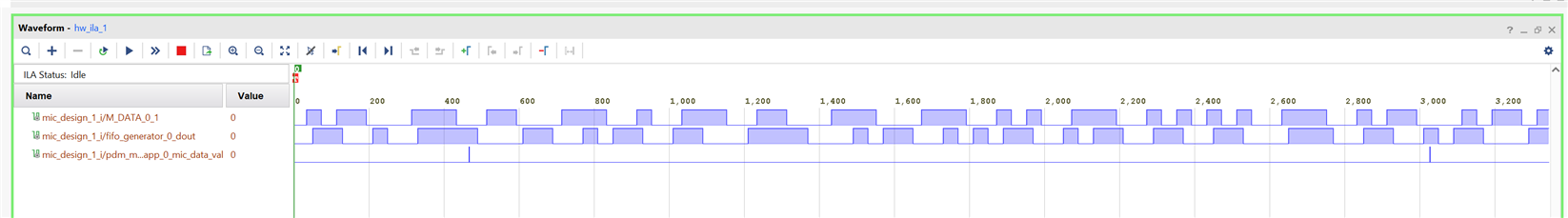

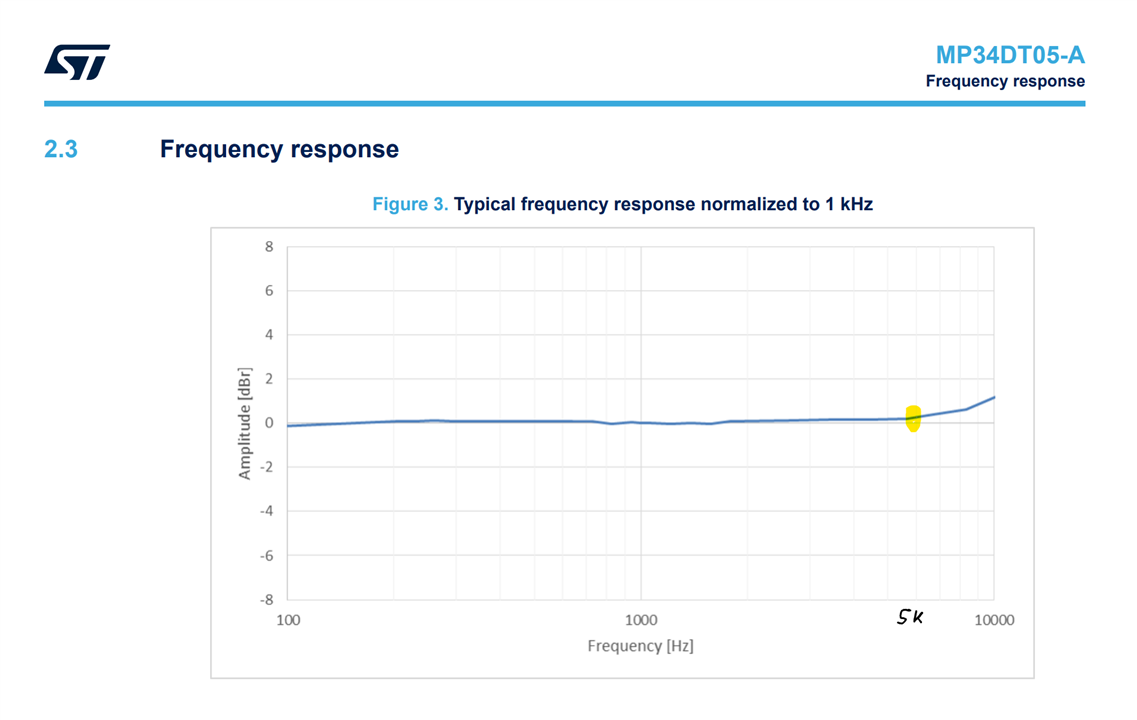

- 6. Minized Microphone Input PDM to PCM via Decimation

- 7. Indicator LEDs and Control Switches Auxiliary Expansion Board

- 8. Low Pass Filter and Sound Amplifier Expansion Boards

- 9. Multiplexer Expansion Board

- 10. ARM 9 Bare Metal Software App. MIDI Control

- 11. Creating the prototype

- 12. Code Repository and References

- 13. Conclusion and next steps

- 14. Path to Programmable III Training Blog Series

3. Minized Synth I: Overview and Features

The MiniZed Synth I is a Monophonic Digital Synthesizer. It features 2 digitally controlled oscillators, a pseudo-random noise generator, a microphone input, a low pass filter, 2 envelope generators, a mixer, and a modulation circuit. The MiniZed Synth has a classic one-knob-per-function design.

Although this first version is monophonic, thanks to the versatility of FPGAs the design can become polyphonic with very little effort by replicating the monophonic module of the synthesizer and creating a dispatcher that assigns the different voices and a new voice mixer module.

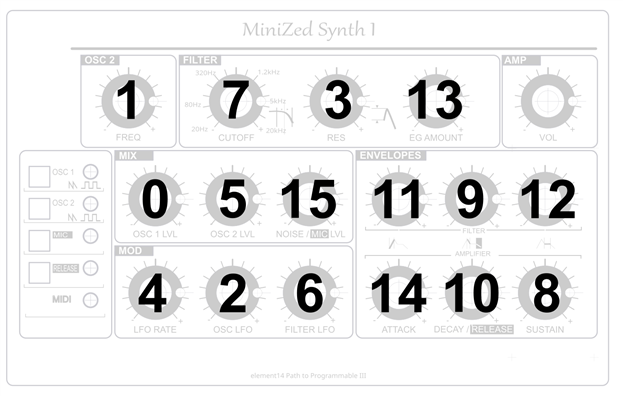

FRONT PANEL

MiniZed Synth I Front Panel. It has seventeen analog knobs, four-mode selection pushbuttons, and five-mode or action indicator LEDs.

OSCILLATORS

Two Digital Controlled Oscillators with selectable Sawtooth and Square waveshapes.

NOISE GENERATOR

Shapeable Pseudo Random Noise Generator.

MIC Input

The signal picked up by the MiniZed's microphone can be used as an alternate sound source.

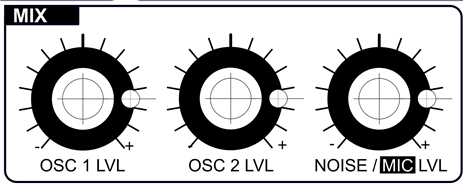

MIX

Mixer for adjusting signal levels independently.

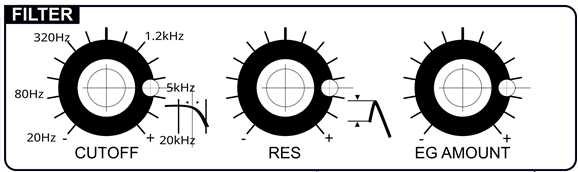

FILTER

12 dB/Octave Digital Low Pass Filter with Adjustable Resonance.

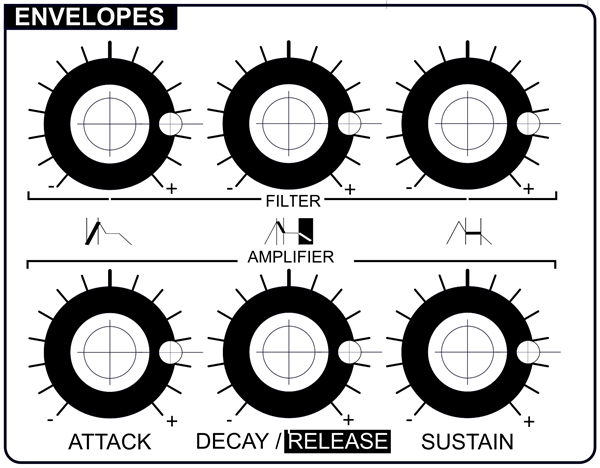

ENVELOPES

Two Attack-Decay-Sustain-Release (ADSR) envelope generators for modulating the filter and amplifier.

The Envelope Decay and Release segments are controlled by the DECAY knob, while the Release segments are enabled or disabled via the RELEASE switch

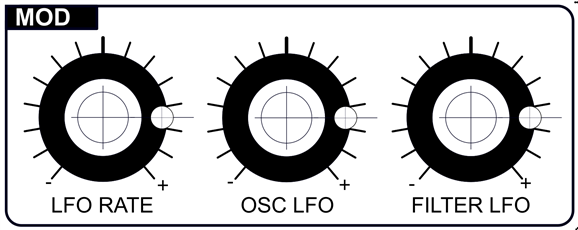

MOD

MIDI-syncable Low Frequency Oscillator (LFO) with Rate and individual control for the oscillators LFO amount and the filter LFO amount.

AUDIO OUT

1/8" Headphone Output

MIDI

DIN MIDI and USB UART/MIDI bridge

3.1. Signal Flow

The below diagram shows how the MiniZed Synth generates sound. It shows the flow of Audio, Digital Control, and Modulation signals in the MiniZed Synth. Heavy lines indicate 16-bit Pulse Code Modulation (PCM) audio signals flowing from left to right. Lighter lines indicate Digital Control Signals which flow from the bottom. Dotted lines indicate Modulation routings. Spaced-dotted lines indicate 1-bit Pulse Density Modulation (PDM) digital signals

MiniZed Synth Signal Flow Diagram. The diagram shows the different signals used by the synthesizer: control lines, PCM and PDM digital audio signal lines, the modulation routing of the signals, and the final analog sound signal.

The MiniZed Synth's source signals are created by two direct digital frequency synthesis oscillators and a digital Pseudo-Random Noise Generator which are mixed with the MiniZed built-in microphone 1-bit Pulse Density Modulation (PDM) signal previously converted to 16-bit Pulse Coded Modulation (PCM) via decimation.

The Mixer Output is routed to the Filter, where the tone is sculpted according to the Filter parameters and the Filter Attack-Decay-Sustain-Release (ADSR) Envelope.

The signal is then passed to the amplifier stage, where the Volume ADSR envelope shapes it. The Attack-Decay-Sustain-Release (ADSR) envelope modulation scheme is based on the observation that when a real instrument generates a note, the volume of the musical note changes over time. It rises rapidly from zero and then steadily decays.

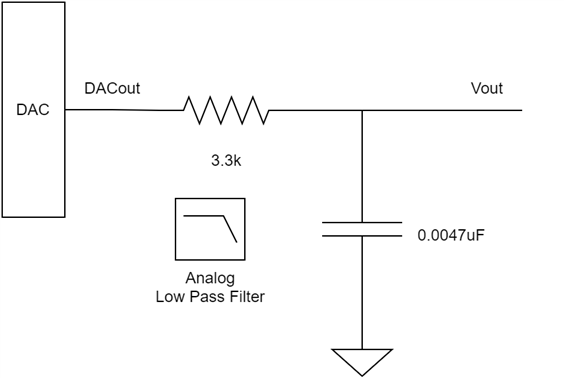

Finally, the PCM signal is routed to the 1-bit Delta Sigma Digital to Analog Converter and routed to an RC Low Pass Filter. The final level is set by the Analog Volume Control Knob.

Each time the MiniZed Synth receives a MIDI "Note On" command, it produces a Pitch control signal and Gate signal in response. The Pitch control signal sets the Pitch of the Oscillators, while the Gate signal triggers the Filter and Volume ADSR envelopes.

3.2. Basic Operation

The MiniZed Synth I responds to MIDI messages. In addition, Minized Synth has an LED MIDI indicator that indicates MIDI activity on either the DIN MIDI or the USB / UART connector. Additional parameters can be accessed via MIDI control.

3.3. The components

Oscillators

The Oscillators together with the Pseudo-Random Noise Generator are the main source of the MiniZed Synth. They use Direct digital synthesis (DDS) a method employed for creating arbitrary waveforms from a single, fixed-frequency reference that can be tuned and amplified into sound that we can hear. The Mnized Synth can produce a total musical range of 8 octaves.

The OSCILLATOR 1 serves as a master Oscillator to which OSCILLATOR 2 is tuned. Two independent switches select the waveform for each Oscillator (Sawtooth or Square). The MiniZed is not limited to these two waveforms but it can also be programmed to generate sinusoidal, triangle, and PWM square waves.

Panel controls for the Oscillators

OSCILLATOR 1 Switch (CC# 70):

Selects a Sawtooth (LED OFF) or Square wave (LED ON) for OSC 1.

OSCILLATOR 2 Switch (CC# 71):

Selects a Sawtooth (LED OFF) or Square wave (LED ON) for OSC 2.

VCO 2 FREQ (CC# 17):

Sets the frequency offset of OSC 2 from OSC 1.

The offset range is +/-1 octave.

Center position tunes OSC 2 in unison with OSC 1.

Mixer (Source Levels)

![]()

Each Oscillator (OSC1 & OSC2) has a dedicated level knob that allows you to control the relative strength of each oscillator from 0 to 100%. Another knob allows you to control the relative strength of the other two sound sources, the pseudo-random noise generator, and the MiniZed's internal microphone. A switch selects the third sound source (Mic or Noise). The signal begins to clip the filter at about 2 o’clock creating more aggressive sounds.

Panel Controls for the Mixer

OSC1 LVL (CC# 15):

Sets the level of OSC 1.

OSC 2 LVL (CC# 16):

Sets the level of OSC 2.

NOISE / MIC LVL (CC# 17 / CC# 18)

Sets the level of NOISE or MIC.

Filter

The FILTER is a 12dB/Octave Low Pass Filter design with resonance. It has controls for CUTOFF frequency which determines the range of frequencies the filter will affect, as well as RESONANCE, which determines how much emphasis is applied to the harmonics near the Cutoff frequency.

Frequency response of a Low Pass Filter with Resonance

The FILTER provides either fixed or dynamic timbre modifications. Dynamic changes are provided by the Filter Envelope Generator (EG) and a Low Frequency Oscillator (LFO).

Panel Controls for the Filter

CUTOFF (CC# 19):

Adjusts the CUTOFF frequency of the Low Pass Filter from 20 Hz to 20 KHz. As the knob is rotated clockwise, the cutoff frequency is increased, allowing more harmonics to pass through the filter, resulting in a brighter sound. Conversely, as the knob is rotated counterclockwise, the sounds get darker.

RESONANCE (RES) (CC# 21):

Sets the amount of signal sent from the FILTER output to be fed back into its input. This creates a peak in the frequency that can be increased to self-oscillation.

EG AMOUNT (CC# 22):

Determines how much the Filter Envelope Generator (EG) adds to or subtracts from the Filter Cutoff control setting.

When the EG AMOUNT knob is set to positive (+), turn the FILTER CUTOFF knob left to hear the effect.

When the EG AMOUNT knob is set to negative (-), turn the FILTER CUTOFF knob right to hear the effect.

Envelopes

ENVELOPE GENERATORS (EGs) add motion to a sound after a note is played. The MiniZed Synth has two separate Envelope Generators that affect the brightness and loudness of

the MiniZed Synth's sound by modulating the Filter Cutoff and Volume.

The EGs are started by a Gate or MIDI Note message. Once started, their shape in time is set by the ATTACK, DECAY/RELEASE, and SUSTAIN controls, as well as the Release switch and length of the Note played.

Panel Controls for the Envelopes

FILTER ATTACK (CC# 23):

Sets the time it takes for the Attack portion of the Filter EG to rise from zero to maximum. The Attack time ranges from 1 msec to 30 seconds.

FILTER DECAY/RELEASE (CC# 24):

Sets the time for the Decay and Release portion of the Filter EG. When a note is held, and the Attack time end is reached, the Decay portion of the EG starts. During the Decay portion, the EG moves to the Sustain level. When a note is released, the EG moves back to zero at the rate set by this control. This time ranges from 1 msec to 30 seconds. The Release segment of the

The envelope is determined by the state of the RELEASE switch (ON/OFF).

FILTER SUSTAIN (CC# 25):

Sets the Filter EG level after the Decay and before the Release portion. A note must be held longer than both the Attack and Decay time to reach the Sustain level. The level is adjustable from 0 to 100%.

AMPLIFIER ATTACK (CC# 28):

Sets the time it takes for the Attack portion of the Amplifier EG to rise from zero to maximum. The Attack time ranges from 1 msec to 30 seconds.

AMPLIFIER DECAY/RELEASE (CC# 29):

Sets the time for the Decay and Release portion of the Amplifier EG.

When a note is held, and the Attack time end is reached, the Decay portion of the EG starts. During the decay portion, the EG moves to the Sustain level.

When a note is released, the EG moves back to zero at the rate set by this control. The time ranges from 1 msec to 30 seconds.

The Release segment of the Envelope is determined by the state of the RELEASE switch (ON/OFF).

AMPLIFIER SUSTAIN (CC# 30):

Sets the Amplifier EG level after the Decay and before the Release portion. A note must be held longer than both the Attack and Decay time to reach the Sustain level. The level is adjustable from 0 to 100%.

RELEASE

The RELEASE switch enables or disables the Release segment of both Envelope Generators.

When enabled, the Envelope Release time is the same as the Envelope Decay time, and the DECAY control adjusts the time for both segments.

When disabled, the Release segment does not occur and the Envelope stops abruptly in response to a “Note Off” message (or when the Gate goes to zero).

Modulation (MOD)

The MiniZed Synth's MODULATION section provides an LFO with adjustable RATE and AMOUNT controls for the oscillators and the Filter. The Low-Frequency Oscillator (LFO) is a signal used to move the pitch of Oscillators and the Filter Cutoff up and down automatically. An LFO can be used to simulate vibrato, create wobbling filter sweeps, or make interesting synthesizer sounds.

Panel Controls for the Modulation

LFO RATE (CC# 3):

Sets the frequency of LFO Modulation. The range is from 0.1Hz to 100Hz.

OSC LFO AMOUNT (CC# 13):

Sets the maximum amount the LFO moves the OSCILLATORS pitch up and down, up to +/- 1 octave. Modulation affects both Oscillators.

If using a MIDI controller, the Mod Wheel (CC# 1) is used to fade the LFO Pitch Modulation in and out.

FILTER LFO AMOUNT (CC# 12):

Sets the maximum amount the LFO moves the Filter Cutoff up and down, up to +/- 5 octaves. Amounts above 20KHz or below 20 Hz are clipped.

If using a MIDI controller, the Mod Wheel (CC# 1) is used to fade the LFO Filter Modulation in and out.

Amplifier Volume

The MiniZed Synth features a monophonic Audio Output that is adjusted by the VOLUME control.

This is an external analog control to the MiniZed development board, intended to control an amplified output.

Panel Controls for the Amplifier Volume

VOLUME:

Adjusts the output of an amplified analog output.

Rotating the control fully clockwise produces the maximum output.

Rotating the control fully counterclockwise silences the MiniZed Synth.

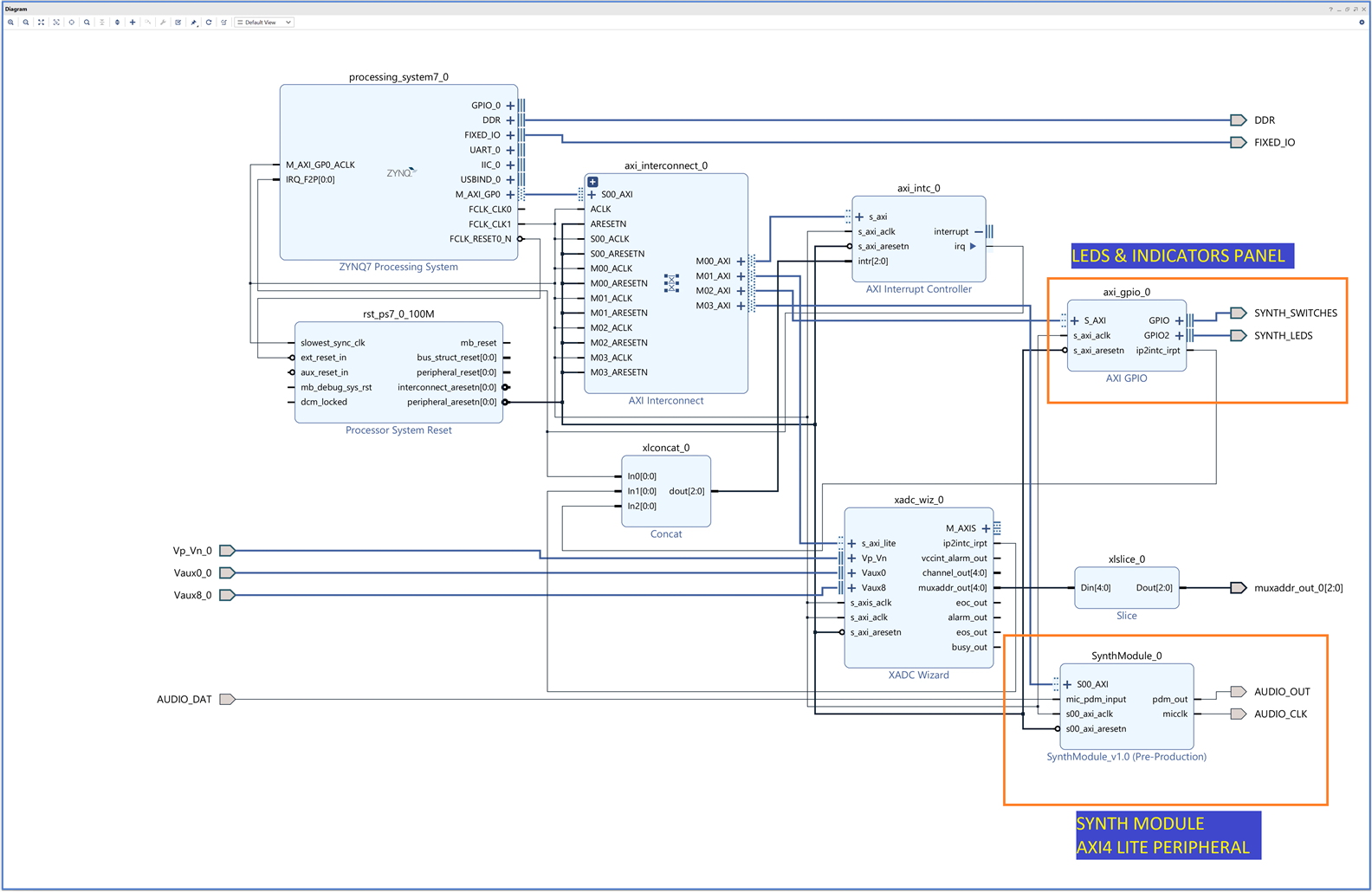

4. High-Level Design

High-level MiniZed Synth Block Diagram. Heavy Blocks are custom blocks

The core of the synthesizer is the AVNET MiniZed development board. The kernel is divided into two main parts. A software program that runs on the Processing System (PS) part, based on the ARM 9 microcontroller, and a design built on top of the FPGA fabric.

The software program is in charge of configuring the oscillators, responding to user inputs from the front panel, and processing the MIDI orders, it interfaces between the MIDI controller devices and the synthesizer module created in the FPGA fabric as an accelerated hardware module.

To expand the user interface there are three new modules external to the MiniZed development board: an additional board with a 16:2 analog multiplexer that allows reading 16 analog potentiometers, a sound editing panel with 16 user-controlled analog potentiometers control, and an expansion board with 4 push buttons and 5 indicator LEDs.

Finally, there is another expansion board that allows the connection of standard MIDI controllers via a 5-pin DIN connector and another one with a Low Pass Filter plus amplifier to convert the Pulse Density Modulated (PDM ) signal generated by a 1-bit Delta Sigma Digital filter module into an analog signal. and amplify the signal sent to the speaker.

Communication with MIDI controllers can be done either through the DIN connector or a USB UART bridge taking advantage of the MiniZed's mini USB connector.

5. Hardware Accelerated Synth Module IP

The Synth Module IP is controlled from a bare metal application written in C that runs on Zynq's ARM 9 Microcontroller Processing System.

The system uses an AXI4 Lite Bus to communicate from the bare metal C app, without the support of a known operating system as FreeRTOS or Linux, to the Synth Module.

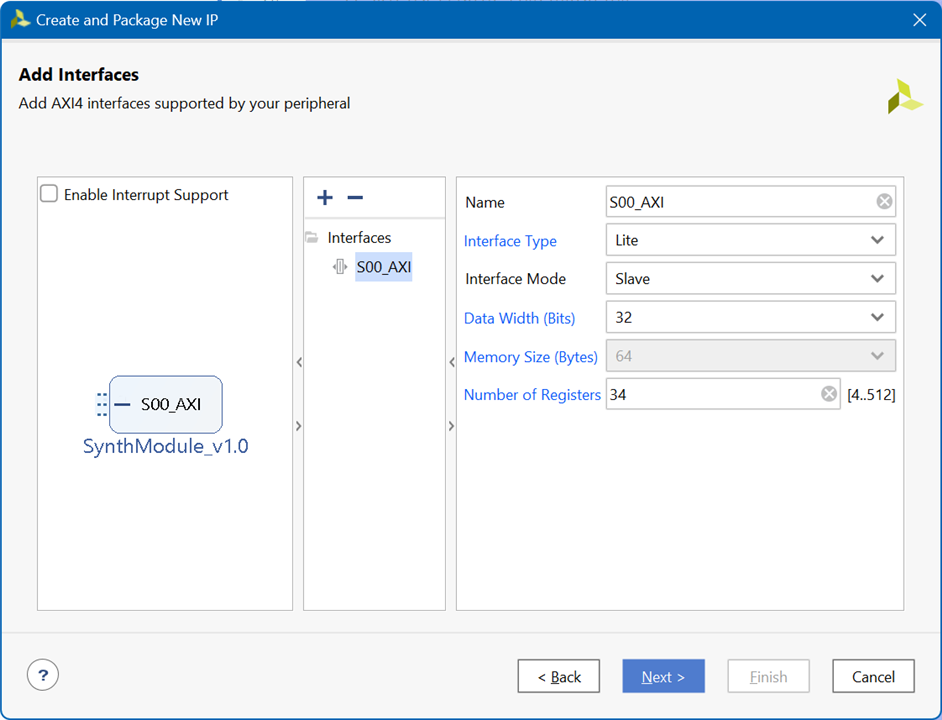

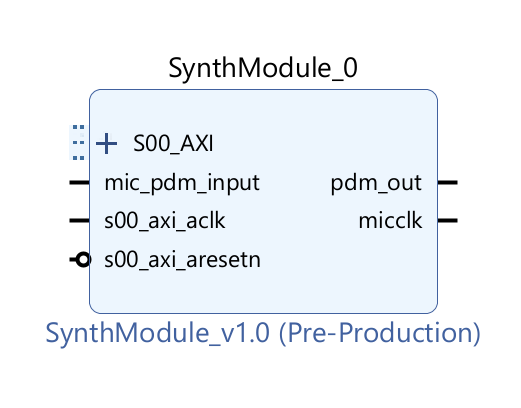

5.1. Custom Synth Module AXI4 Lite Peripheral IP

The Synth Module is packaged as a Vivado IP Block and is fully configured from the bare metal software application using AXI Lite 4 bus protocol.

It has one input for the 1-bit PDM built-in microphone and two outputs. One output with the 2.4 MHz generated microphone clock and the other is 1 bit PDM output sound signal.

If the reader is interested in the complete creation of an AXI4 Lite peripheral, I made a complete tutorial, see Arty S7 50 ArtyBot Custom AXI4 Lite IP Peripheral for Sensing Motor Rotational Speed

The Synth Module is coded in SystemVerilog:

`timescale 1ns / 1ps

module synth_module #(PHASE_ACC_WIDTH = 30)(

input logic clk,

input logic reset,

// oscillator 1 configuration

input logic [PHASE_ACC_WIDTH-1:0] osc1_fccw, // Pitch, oscillator 1 frequency carrier ctrl word

input logic [PHASE_ACC_WIDTH-1:0] osc1_focw, // Detune, oscillator 1 frequency offset ctrl word

input logic [PHASE_ACC_WIDTH-1:0] osc1_pho, // Phase shift, oscillator 1 phase offset ctrl word

input logic [2:0] osc1_wt, // oscillator 1 wave type

input logic [15:0] mix_lvl_osc1, // oscillator 1 volume level

// oscillator 2 configuration

input logic [PHASE_ACC_WIDTH-1:0] osc2_fccw, // Pitch, oscillator 1 frequency carrier ctrl word

input logic [PHASE_ACC_WIDTH-1:0] osc2_focw, // Detune, oscillator 1 frequency offset ctrl word

input logic [PHASE_ACC_WIDTH-1:0] osc2_pho, // Phase shift, oscillator 1 phase offset ctrl word

input logic [2:0] osc2_wt, // oscillator 2 wave type

input logic [15:0] mix_lvl_osc2, // oscillator 2 volume level

// oscillator 3 / noise oscillator configuration

input logic [PHASE_ACC_WIDTH-1:0] osc3_fccw, // Pitch, oscillator 1 frequency carrier ctrl word

input logic [PHASE_ACC_WIDTH-1:0] osc3_focw, // Detune, oscillator 1 frequency offset ctrl word

input logic [PHASE_ACC_WIDTH-1:0] osc3_pho, // Phase shift, oscillator 1 phase offset ctrl word

input logic [2:0] osc3_wt, // oscillator 3 wave type

input logic [15:0] mix_lvl_osc3, // oscillator 3 volume level

// LFO oscillator configuration

input logic [PHASE_ACC_WIDTH-1:0] lfoo_fccw, // LFO oscillator frequency carrier ctrl word

input logic [PHASE_ACC_WIDTH-1:0] lfoo_focw, // LFO oscillator frequency offset ctrl word

input logic [PHASE_ACC_WIDTH-1:0] lfoo_pho, // LFO oscillator phase offset ctrl word

input logic [2:0] lfoo_wt, // LFO oscillator wave type

input logic [15:0] lfoo_lvl, // Sets the maximum amount the LFO moves the VCOs pitch up and down, up to +/- 1 octave.

// LFO filter configuration

input logic [PHASE_ACC_WIDTH-1:0] lfof_fccw, // LFO filter frequency carrier ctrl word

input logic [PHASE_ACC_WIDTH-1:0] lfof_focw, // LFO filter frequency offset ctrl word

input logic [PHASE_ACC_WIDTH-1:0] lfof_pho, // LFO filter phase offset ctrl word

input logic [2:0] lfof_wt, // LFO filter wave type

input logic [15:0] lfof_lvl, // Sets the maximum amount the LFO moves the Filter Cutoff up and down, up to +/- 5 octaves.

// Amplifier ADSR configuration

input logic adsra_start, // generate a pulse to start the envelope generation

input logic [31:0] adsra_a, // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

input logic [31:0] adsra_d, // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

input logic [31:0] adsra_sl, // amplitude for the sustain segment

input logic [31:0] adsra_r, // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

input logic [31:0] adsra_st, // tsustain / t_sys steps for the sustain

// Filter ADSR configuration

input logic adsrf_start, // generate a pulse to start the envelope generation

input logic [31:0] adsrf_a, // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

input logic [31:0] adsrf_d, // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

input logic [31:0] adsrf_sl, // amplitude for the sustain segment

input logic [31:0] adsrf_r, // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

input logic [31:0] adsrf_st, // tsustain / t_sys steps for the sustain

// Filter configuration

input logic [31:0] fcut, // filter cutoff frequency

input logic [31:0] fres, // filter resonance level

input logic [31:0] feg, // filter envelope generator amount

// PDM Microphone

input logic mic_pdm_input, // Input external P1-bit DM MiniZed Signal AUDIO_DAT

input logic [15:0] mix_lvl_mic, // oscillator 3 volume level

output logic pdm_out, // 1-bit PDM sound output

output logic mic_clk, // generated microphone clock signal route to Minized external AUDIO_CLK

output logic adsra_idle,

output logic [15:0] adsra_amp

);

// signal declarations

localparam BIAS = 2 ** (15); // {1'b1, (W-2){1'b0}};

// constants for envelopes

localparam MAX = 32'h8000_0000; // MAX volume

localparam BYPASS = 32'hffff_ffff; // Bypass envelope

localparam ZERO = 32'h0000_0000; // mute

// constants for oscillators

localparam SINE = 3'b000;

localparam SQUARE = 3'b001;

localparam SAW = 3'b010;

localparam TRIANGLE = 3'b011;

localparam NOISE = 3'b100;

// lfo oscillator outputs

logic [15:0] lfoo_output; // LFO oscillator output

logic lfoo_pulse_out; // LFO Oscillator pulse output

// // lfo filter outputs

logic [15:0] lfof_output; // lfo filter output

logic lfof_pulse_out; // Oscillator 1 pulse output

// Oscillator 1 outputs

logic [15:0] osc1_pcm_out; // Oscillator 1 PCM output

logic osc1_pulse_out; // Oscillator 1 pulse output

// // Oscillator 2 outputs

logic [15:0] osc2_pcm_out; // Oscillator 2 PCM output

logic osc2_pulse_out; // Oscillator 2 pulse output

// // Noise / Oscillator 3 outputs

logic [15:0] osc3_pcm_out; // Oscillator 3 PCM output

logic osc3_pulse_out; // Oscillator 3 pulse output

// Microphone Outputs

logic [15:0] mic_pcm_out; // Microphone PCM output

logic mic_data_valid; // Microphone PDM to PCM conversion data valid

// Mixer outputs

logic [15:0] mix_pcm_out; // Mixer PCM output

// amplifier ADSR amplitude output

logic [15:0] adsra_amp;

logic [15:0] adsra_rt_amp;

logic [15:0] adsra_selected;

// filter ADSR amplitude output

logic [15:0] adsrf_amp;

logic [15:0] adsrf_rt_amp;

logic [15:0] adsrf_selected;

// Amplifier outputs

logic [15:0] amp_pcm_out;

// filter outputs

logic [15:0] filter_pcm_out;

logic [PHASE_ACC_WIDTH-1:0] lfoo_extended;

logic [PHASE_ACC_WIDTH-1:0] lfof_extended;

logic adsrf_idle;

logic adsrf_rt_idle;

logic adsrf_nrt_idle;

logic adsra_rt_idle;

logic adsra_nrt_idle;

// // Keep The range is from 0.01Hz to 100Hz

// // instantiate lfo oscillator

ddfs #(.PHASE_ACC_WIDTH(PHASE_ACC_WIDTH)) lfoo(.clk(clk),

.reset(reset),

.freq_carrier_ctrl_word(lfoo_fccw),

.freq_offset_ctrl_word(lfoo_focw),

.phase_offset(lfoo_pho),

.envelope(lfoo_lvl), // Amplitude modulation: envelope, digitized value of A(t) in Q2.14 format

.pcm_out(lfoo_output),

.pulse_out(lfoo_pulse_out),

.wave_type( lfoo_wt)

);

// extend sign to 30 bits

assign lfoo_extended = {{ 14{lfoo_output[15]}},lfoo_output};

// extend sign to 30 bits

assign lfof_extended = {{ 14{lfof_output[15]}},lfof_output};

// // Keep The range is from up to +/- 5 octaves. Amounts above 20KHz or below 20 Hz are clipped

// // instantiate lfo filter

ddfs #(.PHASE_ACC_WIDTH(PHASE_ACC_WIDTH)) lfof(.clk(clk),

.reset(reset),

.freq_carrier_ctrl_word(lfof_fccw),

.freq_offset_ctrl_word(lfof_focw),

.phase_offset(lfof_pho),

.envelope(lfof_lvl), // Amplitude modulation: envelope, digitized value of A(t) in Q2.14 format

.pcm_out(lfof_output),

.pulse_out(lfof_pulse_out),

.wave_type( lfof_wt)

);

// instantiate oscillator 1 osc_1

ddfs #(.PHASE_ACC_WIDTH(PHASE_ACC_WIDTH)) osc1(.clk(clk),

.reset(reset),

.freq_carrier_ctrl_word(osc1_fccw),// 4.724 .freq_carrier_ctrl_word(osc1_fccw),

.freq_offset_ctrl_word(lfoo_extended), // .freq_offset_ctrl_word(lfoo_output), // LFO moves the VCOs pitch up and down, up to +/- 1 octave

.phase_offset(osc1_pho), // .phase_offset(osc1_pho),

.envelope(16'h4000), // Amplitude modulation: envelope, digitized value of A(t) in Q2.14 format

.pcm_out(osc1_pcm_out),

.pulse_out(osc1_pulse_out),

.wave_type(osc1_wt)//.wave_type( 3'b001)

);

// // instantiate oscillator 2 osc_2

ddfs #(.PHASE_ACC_WIDTH(PHASE_ACC_WIDTH)) osc2(.clk(clk),

.reset(reset),

.freq_carrier_ctrl_word(osc2_fccw),

.freq_offset_ctrl_word(lfoo_extended), // LFO moves the VCOs pitch up and down, up to +/- 1 octave

.phase_offset(osc2_pho),

.envelope(16'h4000), // Amplitude modulation: envelope, digitized value of A(t) in Q2.14 format

.pcm_out(osc2_pcm_out),

.pulse_out(osc2_pulse_out),

.wave_type( osc2_wt)

);

// instantiate oscillator 3 osc_3 usually noise

ddfs #(.PHASE_ACC_WIDTH(PHASE_ACC_WIDTH)) osc3(.clk(clk),

.reset(reset),

.freq_carrier_ctrl_word(osc3_fccw),

.freq_offset_ctrl_word(lfoo_extended),

.phase_offset(osc3_pho),

.envelope(16'h4000), // Amplitude modulation: envelope, digitized value of A(t) in Q2.14 format

.pcm_out(osc3_pcm_out),

.pulse_out(osc3_pulse_out),

.wave_type( osc3_wt)

);

// instantiate PDM to PCM converter for the microphone input

pdm_microphone microphone(

.clk(clk),

.reset(reset),

.mic_pdm_data(mic_pdm_input),

.mic_pcm_data(mic_pcm_out),

.mic_data_valid(mic_data_valid),

.mic_clk(mic_clk)

);

// instantiate mixer

mixer mix(.clk(clk),

.reset(reset),

.input_1(osc1_pcm_out),

.lvl_1(mix_lvl_osc1),

.input_2(osc2_pcm_out),

.lvl_2(mix_lvl_osc2),

.input_3(osc3_pcm_out),// .input_3(osc3_pcm_out),

.lvl_3(mix_lvl_osc3),

.input_4(mic_pcm_out),

.lvl_4(mix_lvl_mic),

.pcm_out(mix_pcm_out)

);

// if sustain time is 32'hffff_fff select real time mode ADSR

always_comb begin

if (adsra_st == 32'hffff_ffff) begin

adsra_selected = adsra_rt_amp;

adsrf_selected = adsrf_rt_amp;

end else begin

adsra_selected = adsra_amp;

adsrf_selected = adsrf_amp;

end

end

assign adsra_idle = adsra_nrt_idle & adsra_rt_idle & adsrf_nrt_idle & adsrf_rt_idle;

// instantiate amplifier ADSR amplitude generator

adsr adsra(

.clk(clk),

.reset(reset),

.start(adsra_start), // generate a pulse to start the envelope generation

.attack_step_value(adsra_a), // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

.decay_step_value(adsra_d), // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

.sustain_level(adsra_sl), // amplitude for the sustain segment

.release_step_value(adsra_r), // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

.sustain_time(adsra_st), // tsustain / t_sys steps for the sustain

.envelope(adsra_amp),

.adsr_idle(adsra_nrt_idle)

);

// instantiate amplifier ADSR real time mode amplitude generator

adsr_rt adsra_rt(

.clk(clk),

.reset(reset),

.start(adsra_start), // g adsr sustain active when start asserted

.attack_step_value(adsra_a), // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

.decay_step_value(adsra_d), // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

.sustain_level(adsra_sl), // amplitude for the sustain segment

.release_step_value(adsra_r), // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

.envelope(adsra_rt_amp),

.adsr_idle(adsra_rt_idle)

);

// // instantiate filter ADSR amplitude generator

adsr adsrf(

.clk(clk),

.reset(reset),

.start(adsrf_start), // generate a pulse to start the envelope generation

.attack_step_value(adsrf_a), // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

.decay_step_value(adsrf_d), // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

.sustain_level(adsrf_sl), // amplitude for the sustain segment

.release_step_value(adsrf_r), // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

.sustain_time(adsrf_st), // tsustain / t_sys steps for the sustain

.envelope(adsrf_amp),

.adsr_idle(adsrf_nrt_idle)

);

adsr_rt adsrf_rt(

.clk(clk),

.reset(reset),

.start(adsrf_start), // adsr sustain active when start asserted

.attack_step_value(adsrf_a), // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

.decay_step_value(adsrf_d), // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

.sustain_level(adsrf_sl), // amplitude for the sustain segment

.release_step_value(adsrf_r), // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

.envelope(adsrf_rt_amp),

.adsr_idle(adsrf_rt_idle)

);

// instantiate Amplifier

amplifier amp(

.clk(clk),

.reset(reset),

.pcm_input(mix_pcm_out),

.envelope(adsra_selected),

.pcm_out(amp_pcm_out));

// // instantiate filter

filter filter_unit(

.clk(clk),

.reset(reset),

.fccw(osc1_fccw),

.pcm_in(amp_pcm_out),

.cutoff_freq(fcut),

.resonance_lvl(fres),

.eg_amount(feg), //EG AMOUNT Determines how much the Filter Envelope Generator (EG) adds to or subtracts from the Filter Cutoff control setting.

.envelope(adsrf_rt_amp),

.modulation(lfof_output),

.pcm_out(filter_pcm_out)

);

// instantiate 1 bit delta sigma DAC

ds_1bit_dac dac(

.clk(clk),

.reset(reset),

.pcm_in(filter_pcm_out),

.pdm_out(pdm_out)

);

endmodule

SynthModuleAxi

`timescale 1 ns / 1 ps

module SynthModule_v1_0_S00_AXI #

(

// Users to add parameters here

// User parameters ends

// Do not modify the parameters beyond this line

// Width of S_AXI data bus

parameter integer C_S_AXI_DATA_WIDTH = 32,

// Width of S_AXI address bus

parameter integer C_S_AXI_ADDR_WIDTH = 8

)

(

// Input external P1-bit DM MiniZed Signal AUDIO_DAT

input wire mic_pdm_input,

// 1-bit PDM sound output

output wire pdm_out, // 1-bit PDM sound output

// generated microphone clock signal route to Minized external AUDIO_CLK

output wire micclk,

output wire [31:0] osc1Freq,

// User ports ends

// Do not modify the ports beyond this line

// Global Clock Signal

input wire S_AXI_ACLK,

// Global Reset Signal. This Signal is Active LOW

input wire S_AXI_ARESETN,

// Write address (issued by master, acceped by Slave)

input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_AWADDR,

// Write channel Protection type. This signal indicates the

// privilege and security level of the transaction, and whether

// the transaction is a data access or an instruction access.

input wire [2 : 0] S_AXI_AWPROT,

// Write address valid. This signal indicates that the master signaling

// valid write address and control information.

input wire S_AXI_AWVALID,

// Write address ready. This signal indicates that the slave is ready

// to accept an address and associated control signals.

output wire S_AXI_AWREADY,

// Write data (issued by master, acceped by Slave)

input wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_WDATA,

// Write strobes. This signal indicates which byte lanes hold

// valid data. There is one write strobe bit for each eight

// bits of the write data bus.

input wire [(C_S_AXI_DATA_WIDTH/8)-1 : 0] S_AXI_WSTRB,

// Write valid. This signal indicates that valid write

// data and strobes are available.

input wire S_AXI_WVALID,

// Write ready. This signal indicates that the slave

// can accept the write data.

output wire S_AXI_WREADY,

// Write response. This signal indicates the status

// of the write transaction.

output wire [1 : 0] S_AXI_BRESP,

// Write response valid. This signal indicates that the channel

// is signaling a valid write response.

output wire S_AXI_BVALID,

// Response ready. This signal indicates that the master

// can accept a write response.

input wire S_AXI_BREADY,

// Read address (issued by master, acceped by Slave)

input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_ARADDR,

// Protection type. This signal indicates the privilege

// and security level of the transaction, and whether the

// transaction is a data access or an instruction access.

input wire [2 : 0] S_AXI_ARPROT,

// Read address valid. This signal indicates that the channel

// is signaling valid read address and control information.

input wire S_AXI_ARVALID,

// Read address ready. This signal indicates that the slave is

// ready to accept an address and associated control signals.

output wire S_AXI_ARREADY,

// Read data (issued by slave)

output wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_RDATA,

// Read response. This signal indicates the status of the

// read transfer.

output wire [1 : 0] S_AXI_RRESP,

// Read valid. This signal indicates that the channel is

// signaling the required read data.

output wire S_AXI_RVALID,

// Read ready. This signal indicates that the master can

// accept the read data and response information.

input wire S_AXI_RREADY

);

// AXI4LITE signals

reg [C_S_AXI_ADDR_WIDTH-1 : 0] axi_awaddr;

reg axi_awready;

reg axi_wready;

reg [1 : 0] axi_bresp;

reg axi_bvalid;

reg [C_S_AXI_ADDR_WIDTH-1 : 0] axi_araddr;

reg axi_arready;

reg [C_S_AXI_DATA_WIDTH-1 : 0] axi_rdata;

reg [1 : 0] axi_rresp;

reg axi_rvalid;

// Example-specific design signals

// local parameter for addressing 32 bit / 64 bit C_S_AXI_DATA_WIDTH

// ADDR_LSB is used for addressing 32/64 bit registers/memories

// ADDR_LSB = 2 for 32 bits (n downto 2)

// ADDR_LSB = 3 for 64 bits (n downto 3)

localparam integer ADDR_LSB = (C_S_AXI_DATA_WIDTH/32) + 1;

localparam integer OPT_MEM_ADDR_BITS = 5;

//----------------------------------------------

//-- Signals for user logic register space example

//------------------------------------------------

//-- Number of Slave Registers 34

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg0;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg1;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg2;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg3;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg4;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg5;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg6;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg7;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg8;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg9;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg10;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg11;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg12;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg13;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg14;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg15;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg16;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg17;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg18;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg19;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg20;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg21;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg22;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg23;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg24;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg25;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg26;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg27;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg28;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg29;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg30;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg31;

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg32;

wire [C_S_AXI_DATA_WIDTH-1:0] slv_reg33;

wire slv_reg_rden;

wire slv_reg_wren;

reg [C_S_AXI_DATA_WIDTH-1:0] reg_data_out;

integer byte_index;

reg aw_en;

// I/O Connections assignments

assign S_AXI_AWREADY = axi_awready;

assign S_AXI_WREADY = axi_wready;

assign S_AXI_BRESP = axi_bresp;

assign S_AXI_BVALID = axi_bvalid;

assign S_AXI_ARREADY = axi_arready;

assign S_AXI_RDATA = axi_rdata;

assign S_AXI_RRESP = axi_rresp;

assign S_AXI_RVALID = axi_rvalid;

// Implement axi_awready generation

// axi_awready is asserted for one S_AXI_ACLK clock cycle when both

// S_AXI_AWVALID and S_AXI_WVALID are asserted. axi_awready is

// de-asserted when reset is low.

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_awready <= 1'b0;

aw_en <= 1'b1;

end

else

begin

if (~axi_awready && S_AXI_AWVALID && S_AXI_WVALID && aw_en)

begin

// slave is ready to accept write address when

// there is a valid write address and write data

// on the write address and data bus. This design

// expects no outstanding transactions.

axi_awready <= 1'b1;

aw_en <= 1'b0;

end

else if (S_AXI_BREADY && axi_bvalid)

begin

aw_en <= 1'b1;

axi_awready <= 1'b0;

end

else

begin

axi_awready <= 1'b0;

end

end

end

// Implement axi_awaddr latching

// This process is used to latch the address when both

// S_AXI_AWVALID and S_AXI_WVALID are valid.

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_awaddr <= 0;

end

else

begin

if (~axi_awready && S_AXI_AWVALID && S_AXI_WVALID && aw_en)

begin

// Write Address latching

axi_awaddr <= S_AXI_AWADDR;

end

end

end

// Implement axi_wready generation

// axi_wready is asserted for one S_AXI_ACLK clock cycle when both

// S_AXI_AWVALID and S_AXI_WVALID are asserted. axi_wready is

// de-asserted when reset is low.

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_wready <= 1'b0;

end

else

begin

if (~axi_wready && S_AXI_WVALID && S_AXI_AWVALID && aw_en )

begin

// slave is ready to accept write data when

// there is a valid write address and write data

// on the write address and data bus. This design

// expects no outstanding transactions.

axi_wready <= 1'b1;

end

else

begin

axi_wready <= 1'b0;

end

end

end

// Implement memory mapped register select and write logic generation

// The write data is accepted and written to memory mapped registers when

// axi_awready, S_AXI_WVALID, axi_wready and S_AXI_WVALID are asserted. Write strobes are used to

// select byte enables of slave registers while writing.

// These registers are cleared when reset (active low) is applied.

// Slave register write enable is asserted when valid address and data are available

// and the slave is ready to accept the write address and write data.

assign slv_reg_wren = axi_wready && S_AXI_WVALID && axi_awready && S_AXI_AWVALID;

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

slv_reg0 <= 0;

slv_reg1 <= 0;

slv_reg2 <= 0;

slv_reg3 <= 0;

slv_reg4 <= 0;

slv_reg5 <= 0;

slv_reg6 <= 0;

slv_reg7 <= 0;

slv_reg8 <= 0;

slv_reg9 <= 0;

slv_reg10 <= 0;

slv_reg11 <= 0;

slv_reg12 <= 0;

slv_reg13 <= 0;

slv_reg14 <= 0;

slv_reg15 <= 0;

slv_reg16 <= 0;

slv_reg17 <= 0;

slv_reg18 <= 0;

slv_reg19 <= 0;

slv_reg20 <= 0;

slv_reg21 <= 0;

slv_reg22 <= 0;

slv_reg23 <= 0;

slv_reg24 <= 0;

slv_reg25 <= 0;

slv_reg26 <= 0;

slv_reg27 <= 0;

slv_reg28 <= 0;

slv_reg29 <= 0;

slv_reg30 <= 0;

slv_reg31 <= 0;

slv_reg32 <= 0;

// slv_reg33 <= 0; // assigned in user logic

end

else begin

if (slv_reg_wren)

begin

case ( axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

6'h00:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 0

slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h01:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 1

slv_reg1[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h02:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 2

slv_reg2[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h03:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 3

slv_reg3[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h04:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 4

slv_reg4[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h05:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 5

slv_reg5[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h06:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 6

slv_reg6[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h07:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 7

slv_reg7[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h08:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 8

slv_reg8[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h09:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 9

slv_reg9[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h0A:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 10

slv_reg10[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h0B:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 11

slv_reg11[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h0C:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 12

slv_reg12[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h0D:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 13

slv_reg13[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h0E:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 14

slv_reg14[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h0F:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 15

slv_reg15[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h10:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 16

slv_reg16[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h11:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 17

slv_reg17[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h12:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 18

slv_reg18[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h13:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 19

slv_reg19[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h14:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 20

slv_reg20[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h15:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 21

slv_reg21[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h16:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 22

slv_reg22[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h17:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 23

slv_reg23[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h18:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 24

slv_reg24[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h19:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 25

slv_reg25[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h1A:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 26

slv_reg26[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h1B:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 27

slv_reg27[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h1C:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 28

slv_reg28[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h1D:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 29

slv_reg29[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h1E:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 30

slv_reg30[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h1F:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 31

slv_reg31[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h20:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 32

slv_reg32[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

end

6'h21:

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 )

if ( S_AXI_WSTRB[byte_index] == 1 ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 33

// slv_reg33[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8]; // assigned in user logic

end

default : begin

slv_reg0 <= slv_reg0;

slv_reg1 <= slv_reg1;

slv_reg2 <= slv_reg2;

slv_reg3 <= slv_reg3;

slv_reg4 <= slv_reg4;

slv_reg5 <= slv_reg5;

slv_reg6 <= slv_reg6;

slv_reg7 <= slv_reg7;

slv_reg8 <= slv_reg8;

slv_reg9 <= slv_reg9;

slv_reg10 <= slv_reg10;

slv_reg11 <= slv_reg11;

slv_reg12 <= slv_reg12;

slv_reg13 <= slv_reg13;

slv_reg14 <= slv_reg14;

slv_reg15 <= slv_reg15;

slv_reg16 <= slv_reg16;

slv_reg17 <= slv_reg17;

slv_reg18 <= slv_reg18;

slv_reg19 <= slv_reg19;

slv_reg20 <= slv_reg20;

slv_reg21 <= slv_reg21;

slv_reg22 <= slv_reg22;

slv_reg23 <= slv_reg23;

slv_reg24 <= slv_reg24;

slv_reg25 <= slv_reg25;

slv_reg26 <= slv_reg26;

slv_reg27 <= slv_reg27;

slv_reg28 <= slv_reg28;

slv_reg29 <= slv_reg29;

slv_reg30 <= slv_reg30;

slv_reg31 <= slv_reg31;

slv_reg32 <= slv_reg32;

// slv_reg33 <= slv_reg33; // assigned in user logic

end

endcase

end

end

end

// Implement write response logic generation

// The write response and response valid signals are asserted by the slave

// when axi_wready, S_AXI_WVALID, axi_wready and S_AXI_WVALID are asserted.

// This marks the acceptance of address and indicates the status of

// write transaction.

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_bvalid <= 0;

axi_bresp <= 2'b0;

end

else

begin

if (axi_awready && S_AXI_AWVALID && ~axi_bvalid && axi_wready && S_AXI_WVALID)

begin

// indicates a valid write response is available

axi_bvalid <= 1'b1;

axi_bresp <= 2'b0; // 'OKAY' response

end // work error responses in future

else

begin

if (S_AXI_BREADY && axi_bvalid)

//check if bready is asserted while bvalid is high)

//(there is a possibility that bready is always asserted high)

begin

axi_bvalid <= 1'b0;

end

end

end

end

// Implement axi_arready generation

// axi_arready is asserted for one S_AXI_ACLK clock cycle when

// S_AXI_ARVALID is asserted. axi_awready is

// de-asserted when reset (active low) is asserted.

// The read address is also latched when S_AXI_ARVALID is

// asserted. axi_araddr is reset to zero on reset assertion.

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_arready <= 1'b0;

axi_araddr <= 32'b0;

end

else

begin

if (~axi_arready && S_AXI_ARVALID)

begin

// indicates that the slave has acceped the valid read address

axi_arready <= 1'b1;

// Read address latching

axi_araddr <= S_AXI_ARADDR;

end

else

begin

axi_arready <= 1'b0;

end

end

end

// Implement axi_arvalid generation

// axi_rvalid is asserted for one S_AXI_ACLK clock cycle when both

// S_AXI_ARVALID and axi_arready are asserted. The slave registers

// data are available on the axi_rdata bus at this instance. The

// assertion of axi_rvalid marks the validity of read data on the

// bus and axi_rresp indicates the status of read transaction.axi_rvalid

// is deasserted on reset (active low). axi_rresp and axi_rdata are

// cleared to zero on reset (active low).

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_rvalid <= 0;

axi_rresp <= 0;

end

else

begin

if (axi_arready && S_AXI_ARVALID && ~axi_rvalid)

begin

// Valid read data is available at the read data bus

axi_rvalid <= 1'b1;

axi_rresp <= 2'b0; // 'OKAY' response

end

else if (axi_rvalid && S_AXI_RREADY)

begin

// Read data is accepted by the master

axi_rvalid <= 1'b0;

end

end

end

// Implement memory mapped register select and read logic generation

// Slave register read enable is asserted when valid address is available

// and the slave is ready to accept the read address.

assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid;

always @(*)

begin

// Address decoding for reading registers

case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

6'h00 : reg_data_out <= slv_reg0;

6'h01 : reg_data_out <= slv_reg1;

6'h02 : reg_data_out <= slv_reg2;

6'h03 : reg_data_out <= slv_reg3;

6'h04 : reg_data_out <= slv_reg4;

6'h05 : reg_data_out <= slv_reg5;

6'h06 : reg_data_out <= slv_reg6;

6'h07 : reg_data_out <= slv_reg7;

6'h08 : reg_data_out <= slv_reg8;

6'h09 : reg_data_out <= slv_reg9;

6'h0A : reg_data_out <= slv_reg10;

6'h0B : reg_data_out <= slv_reg11;

6'h0C : reg_data_out <= slv_reg12;

6'h0D : reg_data_out <= slv_reg13;

6'h0E : reg_data_out <= slv_reg14;

6'h0F : reg_data_out <= slv_reg15;

6'h10 : reg_data_out <= slv_reg16;

6'h11 : reg_data_out <= slv_reg17;

6'h12 : reg_data_out <= slv_reg18;

6'h13 : reg_data_out <= slv_reg19;

6'h14 : reg_data_out <= slv_reg20;

6'h15 : reg_data_out <= slv_reg21;

6'h16 : reg_data_out <= slv_reg22;

6'h17 : reg_data_out <= slv_reg23;

6'h18 : reg_data_out <= slv_reg24;

6'h19 : reg_data_out <= slv_reg25;

6'h1A : reg_data_out <= slv_reg26;

6'h1B : reg_data_out <= slv_reg27;

6'h1C : reg_data_out <= slv_reg28;

6'h1D : reg_data_out <= slv_reg29;

6'h1E : reg_data_out <= slv_reg30;

6'h1F : reg_data_out <= slv_reg31;

6'h20 : reg_data_out <= slv_reg32;

6'h21 : reg_data_out <= slv_reg33;

default : reg_data_out <= 0;

endcase

end

// Output register or memory read data

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_rdata <= 0;

end

else

begin

// When there is a valid read address (S_AXI_ARVALID) with

// acceptance of read address by the slave (axi_arready),

// output the read dada

if (slv_reg_rden)

begin

axi_rdata <= reg_data_out; // register read data

end

end

end

// Add user logic here

//Register 0: Gates Register {30'b0, adsrf_start,adsra_start}

//bit 0: adsra_start, generate a pulse to start the oscillator envelope generation

wire adsra_start;

assign adsra_start = slv_reg0[0];

//bit 1: adsrf_start, generate a pulse to start the filter envelope generation

wire adsrf_start;

assign adsrf_start = slv_reg0[1];

//Register 1 :osc1_fccw

//bits 29 to 0: osc1_fccw 30-bits Pitch, oscillator 1 frequency carrier ctrl word

wire [29:0] osc1_fccw;

assign osc1_fccw = slv_reg1[29:0];

//Register 2 :osc1_focw

//bits 29 to 0: osc1_focw 30-bits Detune, oscillator 1 frequency offset ctrl word

wire [29:0] osc1_focw;

assign osc1_focw = slv_reg2[29:0];

//Register 3: osc1_pho:

//bits 29 to 0: osc1_pho, Phase shift, oscillator 1 phase offset ctrl word

wire [29:0] osc1_pho;

assign osc1_pho = slv_reg3[29:0];

//Register 4 :osc2_fccw:

//bits 29 to 0: osc2_fccw 30-bits Pitch, oscillator 2 frequency carrier ctrl word

wire [29:0] osc2_fccw;

assign osc2_fccw = slv_reg4[29:0];

//Register 5 :osc2_focw

//bits 29 to 0: osc2_focw 30-bits Detune, oscillator 2 frequency offset ctrl word

wire [29:0] osc2_focw;

assign osc2_focw = slv_reg5[29:0];

//Register 6: osc2_pho

//bits 29 to 0: osc2_pho, Phase shift, oscillator 2 phase offset ctrl word

wire [29:0] osc2_pho;

assign osc2_pho = slv_reg6[29:0];

//Register 7 :osc3_fccw

//bits 29 to 0: osc3_fccw 30-bits Pitch, oscillator 3 frequency carrier ctrl word

wire [29:0] osc3_fccw;

assign osc3_fccw = slv_reg7[29:0];

//Register 8 :osc3_focw

//bits 29 to 0: osc3_focw 30-bits Detune, oscillator 3 frequency offset ctrl word

wire [29:0] osc3_focw;

assign osc3_focw = slv_reg8[29:0];

//Register 9: osc3_pho

//bits 29 to 0: osc3_pho, Phase shift, oscillator 3 phase offset ctrl word

wire [29:0] osc3_pho;

assign osc3_pho = slv_reg9[29:0];

//Register 10 :lfoo_fccw

//bits 29 to 0: lfoo_fccw 30-bits Pitch, LFO oscillator frequency carrier ctrl word

wire [29:0] lfoo_fccw;

assign lfoo_fccw = slv_reg10[29:0];

//Register 11 :lfoo_focw

//bits 29 to 0: lfoo_focw 30-bits Detune, LFO oscillator frequency offset ctrl word

wire [29:0] lfoo_focw;

assign lfoo_focw = slv_reg11[29:0];

//Register 12: lfoo_pho

//bits 29 to 0: lfoo_pho, Phase shift, LFO oscillator phase offset ctrl word

wire [29:0] lfoo_pho;

assign lfoo_pho = slv_reg12[29:0];

//Register 13 :lfof_fccw

//bits 29 to 0: lfof_fccw 30-bits Pitch, LFO filter frequency carrier ctrl word

wire [29:0] lfof_fccw;

assign lfof_fccw = slv_reg13[29:0];

//Register 14 :lfof_focw

//bits 29 to 0: lfof_focw 30-bits Detune, LFO filter frequency offset ctrl word

wire [29:0] lfof_focw;

assign lfof_focw = slv_reg14[29:0];

//Register 15: lfof_pho

//bits 29 to 0: lfof_pho, Phase shift, LFO filter phase offset ctrl word

wire [29:0] lfof_pho;

assign lfof_pho = slv_reg15[29:0];

//Register 16: adsra_a, Amplifier ADSR configuration attack step

//bits 31 to 0: adsra_a, precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

wire [31:0] adsra_a;

assign adsra_a = slv_reg16[31:0];

//Register 17: adsra_d, Amplifier ADSR configuration decay step

//bits 31 to 0: adsra_d, precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

wire [31:0] adsra_d;

assign adsra_d = slv_reg17[31:0];

//Register 18: adsra_sl, Amplifier ADSR configuration sustain level

//bits 31 to 0: adsra_sl, amplitude for the sustain segment

wire [31:0] adsra_sl;

assign adsra_sl = slv_reg18[31:0];

//Register 19: adsra_r, Amplifier ADSR configuration, steps for the release segment

//bits 31 to 0: adsra_r, precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

wire [31:0] adsra_r;

assign adsra_r = slv_reg19[31:0];

//Register 20: adsra_st, Amplifier ADSR configuration, time for the sustain segment

//bits 31 to 0: adsra_st, tsustain / t_sys steps for the sustain

wire [31:0] adsra_st;

assign adsra_st = slv_reg20[31:0];

//Register 21: adsrf_a, Filter ADSR configuration attack step

//bits 31 to 0: adsrf_a, precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

wire [31:0] adsrf_a;

assign adsrf_a = slv_reg21[31:0];

//Register 22: adsrf_d, Filter ADSR configuration decay step

//bits 31 to 0: adsrf_d, precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

wire [31:0] adsrf_d;

assign adsrf_d = slv_reg22[31:0];

//Register 23: adsrf_sl, Filter ADSR configuration sustain level

//bits 31 to 0: adsrf_sl, amplitude for the sustain segment

wire [31:0] adsrf_sl;

assign adsrf_sl = slv_reg23[31:0];

//Register 24: adsrf_r, Filter ADSR configuration, steps for the release segment

//bits 31 to 0: adsrf_r, precalculated (A_sus - 0)/(t_release - t_sys) steps for the release segment

wire [31:0] adsrf_r;

assign adsrf_r = slv_reg24[31:0];

//Register 25: adsrf_st, Filter ADSR configuration, time for the sustain segment

//bits 31 to 0: adsrf_st, tsustain / t_sys steps for the sustain

wire [31:0] adsrf_st;

assign adsrf_st = slv_reg25[31:0];

//Register 26: fcut filter cutoff frequency

//bits 31 to 0: fcut, filter cutoff frequency

wire [31:0] fcut;

assign fcut = slv_reg26[31:0];

//Register 27: fres, filter resonance level

//bits 31 to 0: fres, filter resonance level

wire [31:0] fres;

assign fres = slv_reg27[31:0];

//Register 28: feg, filter envelope generator amount

//bits 31 to 0: feg, filter envelope generator amount

wire [31:0] feg;

assign feg = slv_reg28[31:0];

//Register 29: wave types:

//bits 2 to 0: osc1_wt, oscillator 1 wave type

wire [2:0] osc1_wt;

assign osc1_wt = slv_reg29[2:0];

//bits 5 to 3: osc2_wt, oscillator 2 wave type

wire [2:0] osc2_wt;

assign osc2_wt = slv_reg29[5:3];

//bits 8 to 6: osc3_wt, oscillator 3 wave type

wire [2:0] osc3_wt;

assign osc3_wt = slv_reg29[8:6];

//bits 11 to 9: lfoo_wt, LFO oscillator wave type

wire [2:0] lfoo_wt;

assign lfoo_wt = slv_reg29[11:9];

//bits 14 to 12: lfof_wt, LFO filter wave type

wire [2:0] lfof_wt;

assign lfof_wt = slv_reg29[14:12];

//Register 30: Mix levels osc1 & osc2

//bits 15 to 0: mix_lvl_osc1, oscillator 1 volume level

wire [15:0] mix_lvl_osc1;

assign mix_lvl_osc1 = slv_reg30[15:0];

//bits 31 to 16: mix_lvl_osc2, oscillator 2 volume level

wire [15:0] mix_lvl_osc2;

assign mix_lvl_osc2 = slv_reg30[31:16];

//Register 31: Mix levels osc3 & mic

//bits 15 to 0: mix_lvl_osc3, oscillator 3 volume level

wire [15:0] mix_lvl_osc3;

assign mix_lvl_osc3 = slv_reg31[15:0];

//bits 31 to 16: mix_lvl_mic, mic volume level

wire [15:0] mix_lvl_mic;

assign mix_lvl_mic = slv_reg31[31:16];

//Register 32: LFO amounts configurations

//bits 15 to 0: lfoo_lvl, Sets the maximum amount the LFO moves the Oscillators pitch up and down, up to +/- 1 octave.

wire [15:0] lfoo_lvl;

assign lfoo_lvl = slv_reg32[15:0];

//bits 31 to 16: lfof_lvl, Sets the maximum amount the LFO moves the Filter Cutoff up and down, up to +/- 5 octaves.

wire [15:0] lfof_lvl;

assign lfof_lvl = slv_reg32[31:16];

//Read Registers

//Register 33: idle status and amplifier envelope amplitude data

//bits 31 to 16: 16 bit envelope data

wire [15:0] adsra_amp;

//bit 0: idle status

wire adsra_idle;

assign slv_reg33 = {adsra_amp, 15'b0, adsra_idle};

assign osc1Freq = slv_reg1;

// instantiate synth module

synth_module synth_module_1 (

.clk(S_AXI_ACLK),

.reset(~S_AXI_ARESETN), // S_AXI_ARESETN is active low

.osc1_fccw(slv_reg1), // Pitch(), oscillator 1 frequency carrier ctrl word

.osc1_focw(osc1_focw), // Detune(), oscillator 1 frequency offset ctrl word

.osc1_pho(osc1_pho), // Phase shift(), oscillator 1 phase offset ctrl word

.osc1_wt(osc1_wt), // oscillator 1 wave type

.mix_lvl_osc1(mix_lvl_osc1), // oscillator 1 volume level

.osc2_fccw(slv_reg4), // Pitch(), oscillator 1 frequency carrier ctrl word

.osc2_focw(osc2_focw), // Detune(), oscillator 1 frequency offset ctrl word

.osc2_pho(osc2_pho), // Phase shift(), oscillator 1 phase offset ctrl word

.osc2_wt(osc2_wt), // oscillator 2 wave type

.mix_lvl_osc2(mix_lvl_osc2), // oscillator 2 volume level

.osc3_fccw(osc3_fccw), // Pitch(), oscillator 1 frequency carrier ctrl word

.osc3_focw(osc3_focw), // Detune(), oscillator 1 frequency offset ctrl word

.osc3_pho(osc3_pho), // Phase shift(), oscillator 1 phase offset ctrl word

.osc3_wt(osc3_wt), // oscillator 3 wave type

.mix_lvl_osc3(mix_lvl_osc3), // oscillator 3 volume level

.lfoo_fccw(lfoo_fccw), // LFO oscillator frequency carrier ctrl word

.lfoo_focw(lfoo_focw), // LFO oscillator frequency offset ctrl word

.lfoo_pho(lfoo_pho), // LFO oscillator phase offset ctrl word

.lfoo_wt(lfoo_wt), // LFO oscillator wave type

.lfoo_lvl(lfoo_lvl), // Sets the maximum amount the LFO moves the VCOs pitch up and down(), up to +/- 1 octave.

.lfof_fccw(lfof_fccw), // LFO filter frequency carrier ctrl word

.lfof_focw(lfof_focw), // LFO filter frequency offset ctrl word

.lfof_pho(lfof_pho), // LFO filter phase offset ctrl word

.lfof_wt(lfof_wt), // LFO filter wave type

.lfof_lvl(lfof_lvl), // Sets the maximum amount the LFO moves the Filter Cutoff up and down(), up to +/- 5 octaves.

.adsra_start(adsra_start), // generate a pulse to start the envelope generation

.adsra_a(adsra_a), // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

.adsra_d(adsra_d), // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

.adsra_sl(adsra_sl), // amplitude for the sustain segment

.adsra_r(adsra_r), // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

.adsra_st(adsra_st), // tsustain / t_sys steps for the sustain

.adsrf_start(adsrf_start), // generate a pulse to start the envelope generation

.adsrf_a(adsrf_a), // precalculated (Amax - 0)/(t_attack - t_sys) steps for the attack segment

.adsrf_d(adsrf_d), // precalculated (A_max-A_sus) / (t_sustain / t_sys) steps for the decay segment

.adsrf_sl(adsrf_sl), // amplitude for the sustain segment

.adsrf_r(adsrf_r), // precalculated (A_sus - 0)/(t_release - t_sys) steps fot the release segment

.adsrf_st(adsrf_st), // tsustain / t_sys steps for the sustain

.fcut(fcut), // filter cutoff frequency

.fres(fres), // filter resonance level

.feg(feg), // filter envelope generator amount

.mic_pdm_input(mic_pdm_input), // Input external P1-bit DM MiniZed Signal AUDIO_DAT

.mix_lvl_mic(mix_lvl_mic), // oscillator 3 volume level

.pdm_out(pdm_out), // 1-bit PDM sound output

.mic_clk(micclk), // generated microphone clock signal route to Minized external AUDIO_CLK

.adsra_idle(adsra_idle),

.adsra_amp(adsra_amp)

);

// User logic ends

endmodule

SynthModule IP Wrapper

`timescale 1 ns / 1 ps

module SynthModule_v1_0 #

(

// Users to add parameters here

// User parameters ends

// Do not modify the parameters beyond this line

// Parameters of Axi Slave Bus Interface S00_AXI

parameter integer C_S00_AXI_DATA_WIDTH = 32,

parameter integer C_S00_AXI_ADDR_WIDTH = 8

)

(

// Users to add ports here

// Input external P1-bit DM MiniZed Signal AUDIO_DAT

input wire mic_pdm_input,

// 1-bit PDM sound output

output wire pdm_out, // 1-bit PDM sound output

// generated microphone clock signal route to Minized external AUDIO_CLK

output wire micclk,

output wire [31:0] osc1Freq,

// User ports ends

// Do not modify the ports beyond this line

// Ports of Axi Slave Bus Interface S00_AXI

input wire s00_axi_aclk,

input wire s00_axi_aresetn,

input wire [C_S00_AXI_ADDR_WIDTH-1 : 0] s00_axi_awaddr,

input wire [2 : 0] s00_axi_awprot,

input wire s00_axi_awvalid,

output wire s00_axi_awready,

input wire [C_S00_AXI_DATA_WIDTH-1 : 0] s00_axi_wdata,

input wire [(C_S00_AXI_DATA_WIDTH/8)-1 : 0] s00_axi_wstrb,

input wire s00_axi_wvalid,

output wire s00_axi_wready,

output wire [1 : 0] s00_axi_bresp,

output wire s00_axi_bvalid,

input wire s00_axi_bready,

input wire [C_S00_AXI_ADDR_WIDTH-1 : 0] s00_axi_araddr,

input wire [2 : 0] s00_axi_arprot,

input wire s00_axi_arvalid,

output wire s00_axi_arready,

output wire [C_S00_AXI_DATA_WIDTH-1 : 0] s00_axi_rdata,

output wire [1 : 0] s00_axi_rresp,

output wire s00_axi_rvalid,

input wire s00_axi_rready

);

// Instantiation of Axi Bus Interface S00_AXI

SynthModule_v1_0_S00_AXI # (

.C_S_AXI_DATA_WIDTH(C_S00_AXI_DATA_WIDTH),

.C_S_AXI_ADDR_WIDTH(C_S00_AXI_ADDR_WIDTH)

) SynthModule_v1_0_S00_AXI_inst (

.mic_pdm_input(mic_pdm_input),

.pdm_out(pdm_out),

.micclk(micclk),

.osc1Freq(osc1Freq),

.S_AXI_ACLK(s00_axi_aclk),

.S_AXI_ARESETN(s00_axi_aresetn),

.S_AXI_AWADDR(s00_axi_awaddr),

.S_AXI_AWPROT(s00_axi_awprot),

.S_AXI_AWVALID(s00_axi_awvalid),

.S_AXI_AWREADY(s00_axi_awready),

.S_AXI_WDATA(s00_axi_wdata),

.S_AXI_WSTRB(s00_axi_wstrb),

.S_AXI_WVALID(s00_axi_wvalid),

.S_AXI_WREADY(s00_axi_wready),

.S_AXI_BRESP(s00_axi_bresp),

.S_AXI_BVALID(s00_axi_bvalid),

.S_AXI_BREADY(s00_axi_bready),

.S_AXI_ARADDR(s00_axi_araddr),

.S_AXI_ARPROT(s00_axi_arprot),

.S_AXI_ARVALID(s00_axi_arvalid),

.S_AXI_ARREADY(s00_axi_arready),

.S_AXI_RDATA(s00_axi_rdata),

.S_AXI_RRESP(s00_axi_rresp),

.S_AXI_RVALID(s00_axi_rvalid),

.S_AXI_RREADY(s00_axi_rready)

);

// Add user logic here

// User logic ends

endmodule

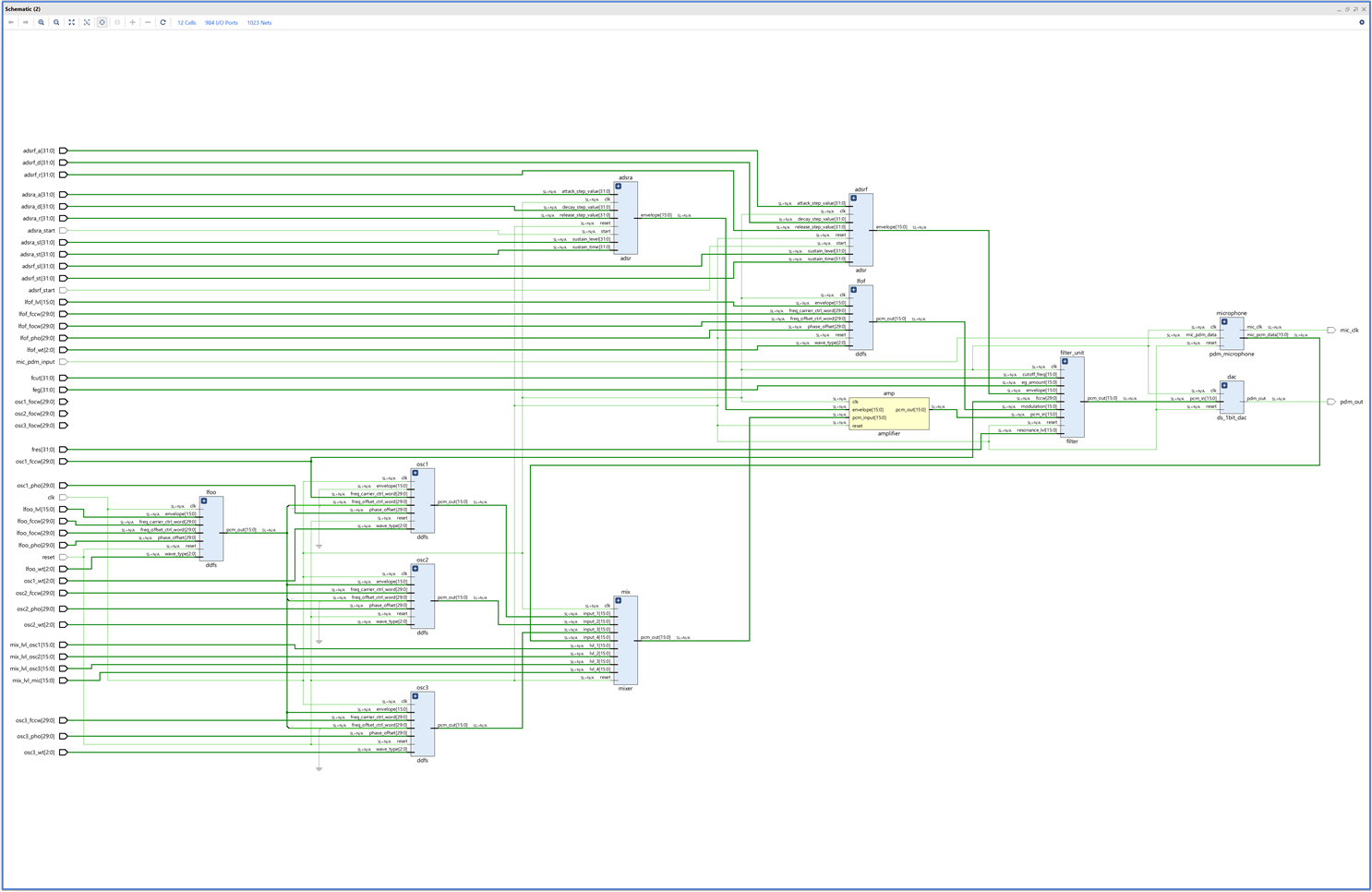

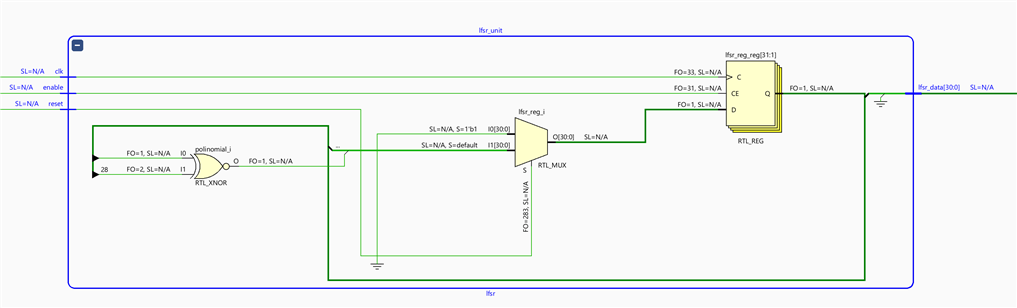

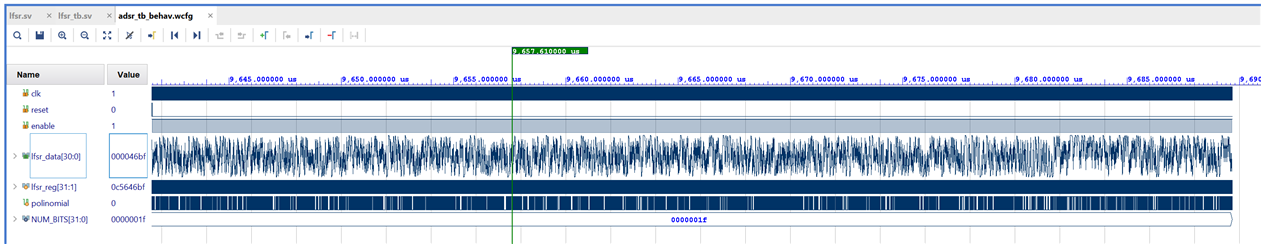

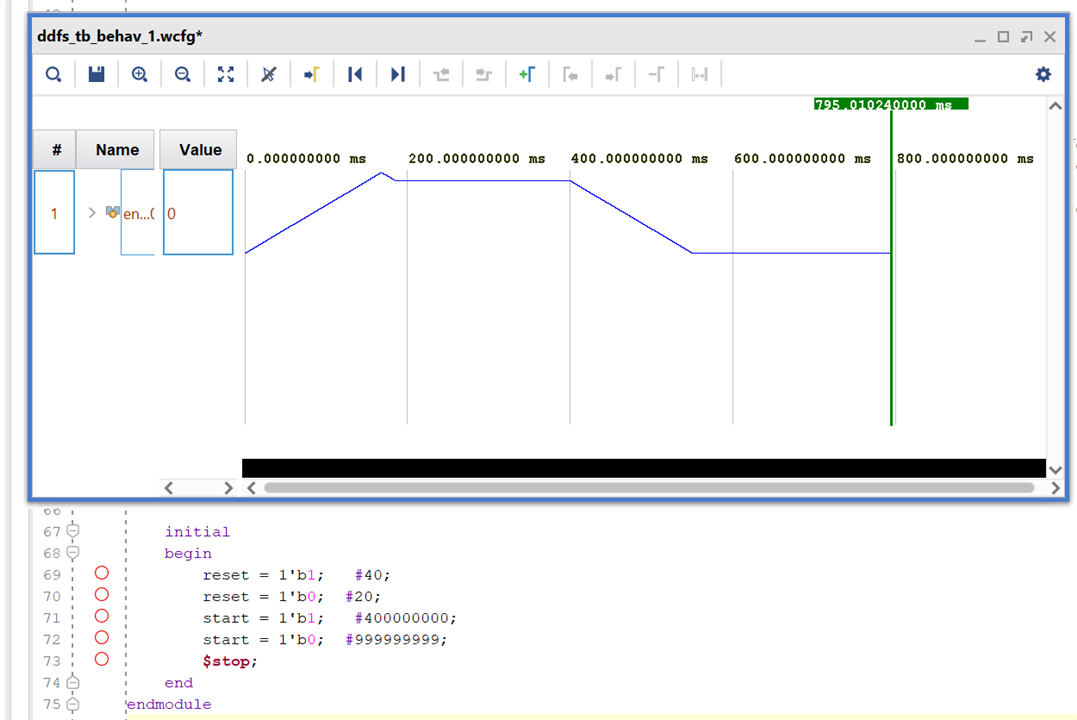

The following schematic is the result of the Vivado Elaborated Design after the RTL Analysis.

To set or read the status of the synth module, the C software application writes or reads to the registers of the Synth module.

Register map

The different registers controlled by the C application are grouped to save MiniZed resources.

The processor interacts with the Synth Module as follows:

- Generate (i.e., write) a pulse to start the amplifier envelope ADSR generation.

- Generate (i.e., write) a pulse to start the filter envelope ADSR generation.

- set (i.e., write) the value of the Oscillator 1 frequency carrier control word osc1_fccw

- set (i.e., write) the value of the Oscillator 1 frequency offset control word osc1_focw

- set (i.e., write) the value of the Oscillator 1 phase offset control word osc1_pho

- set (i.e., write) the value of the Oscillator 2 frequency carrier control word osc2_fccw

- set (i.e., write) the value of the Oscillator 2 frequency offset control word osc2_focw

- set (i.e., write) the value of the Oscillator 3 phase offset control word osc2_pho

- set (i.e., write) the value of the Oscillator 3 frequency carrier control word osc3_fccw

- set (i.e., write) the value of the Oscillator 3 frequency offset control word osc3_focw

- set (i.e., write) the value of the Oscillator 3 phase offset control word osc3_pho

- set (i.e., write) the value of the Oscillators Low-Frequency Oscillator (LFO) frequency carrier control word lfoo_fccw

- set (i.e., write) the value of the Oscillators Low-Frequency Oscillator (LFO) frequency offset control word lfoo_focw

- set (i.e., write) the value of the Oscillators Low-Frequency Oscillator (LFO) phase offset control word lfoo_pho

- set (i.e., write) the value of the Filter Low-Frequency Oscillator (LFO) frequency carrier control word lfof_fccw

- set (i.e., write) the value of the Filter Low-Frequency Oscillator (LFO) frequency offset control word lfof_focw

- set (i.e., write) the value of the Filter Low-Frequency Oscillator (LFO) phase offset control word lfof_pho

- set (i.e., write) the value of the Amplifier ADSR envelope generator configuration attack step adsra_a

- set (i.e., write) the value of the Amplifier ADSR envelope generator configuration decay step adsra_d

- set (i.e., write) the value of the Amplifier ADSR envelope generator configuration sustain level adsra_sl

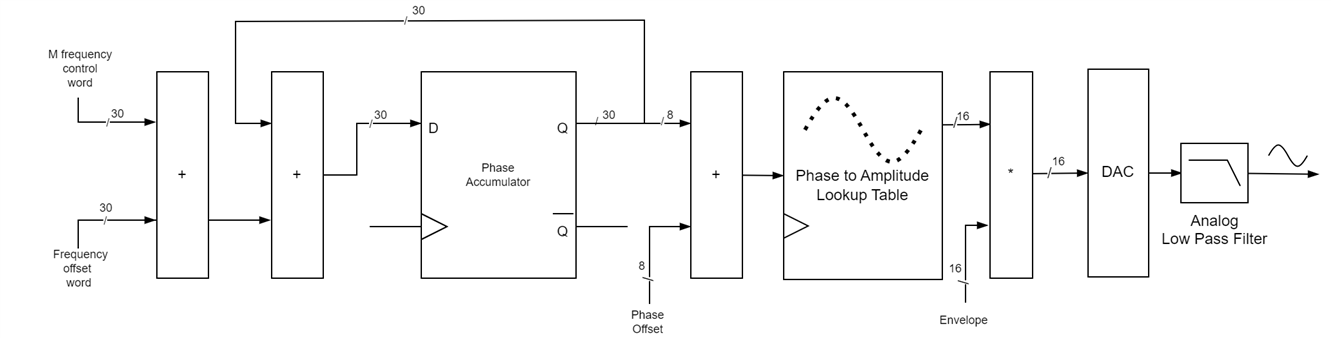

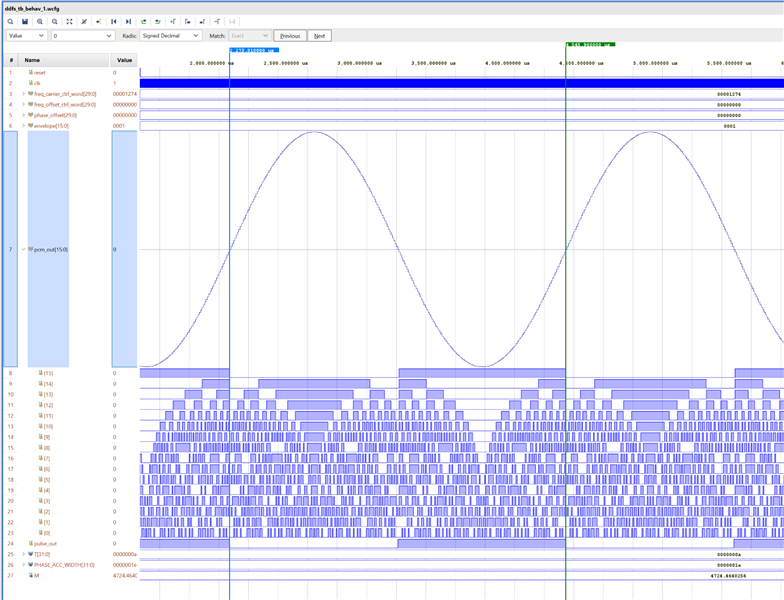

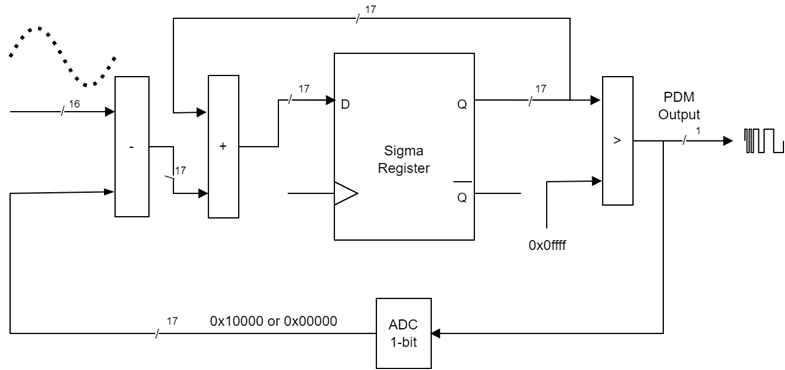

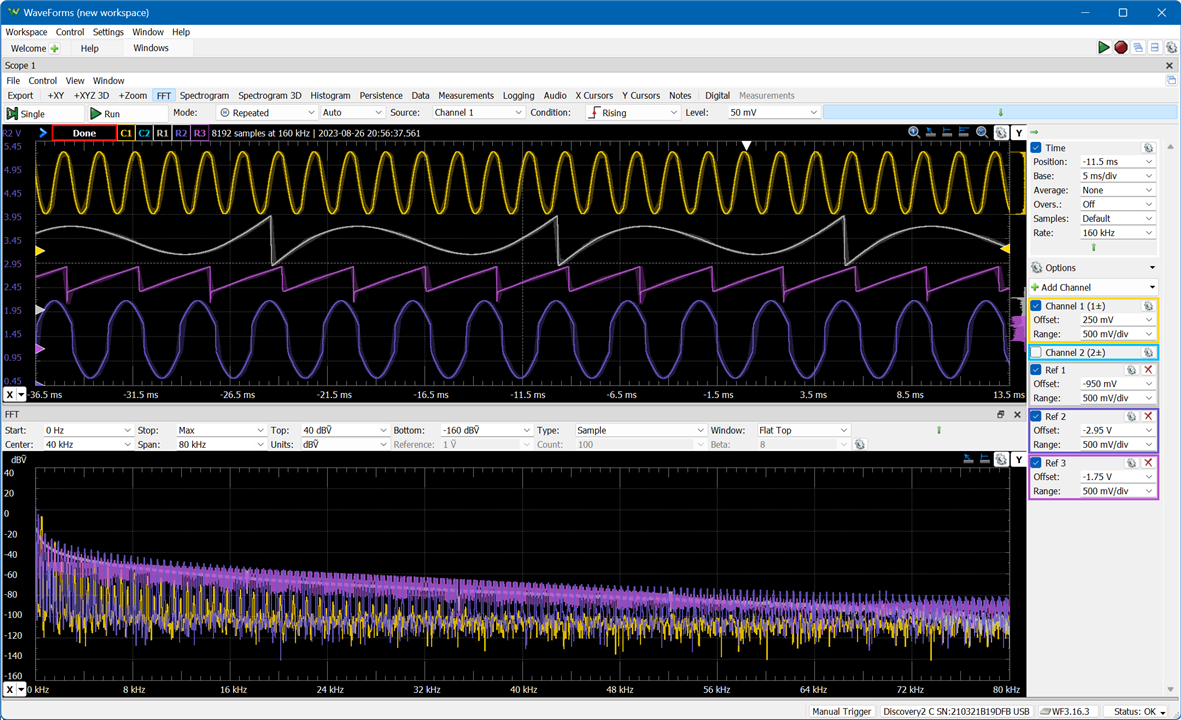

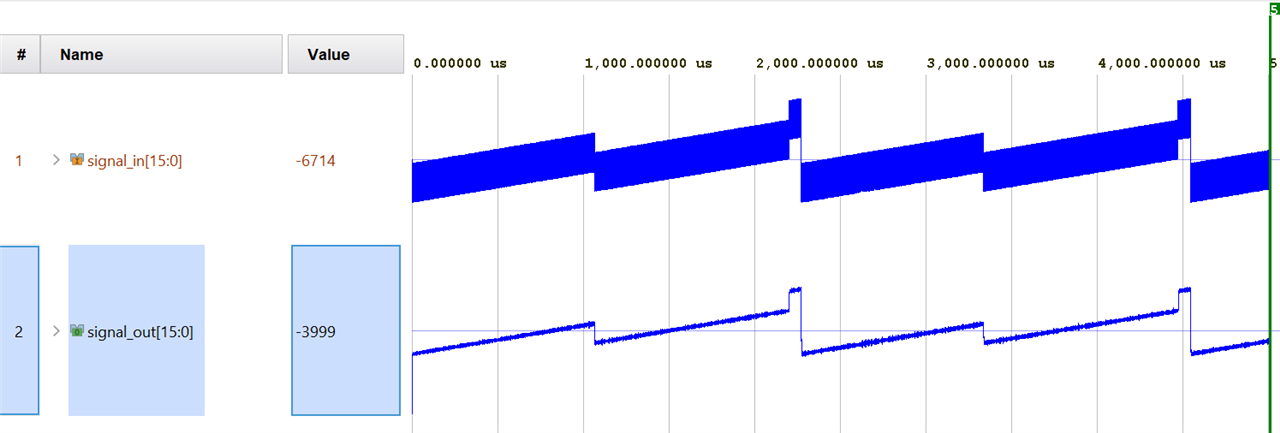

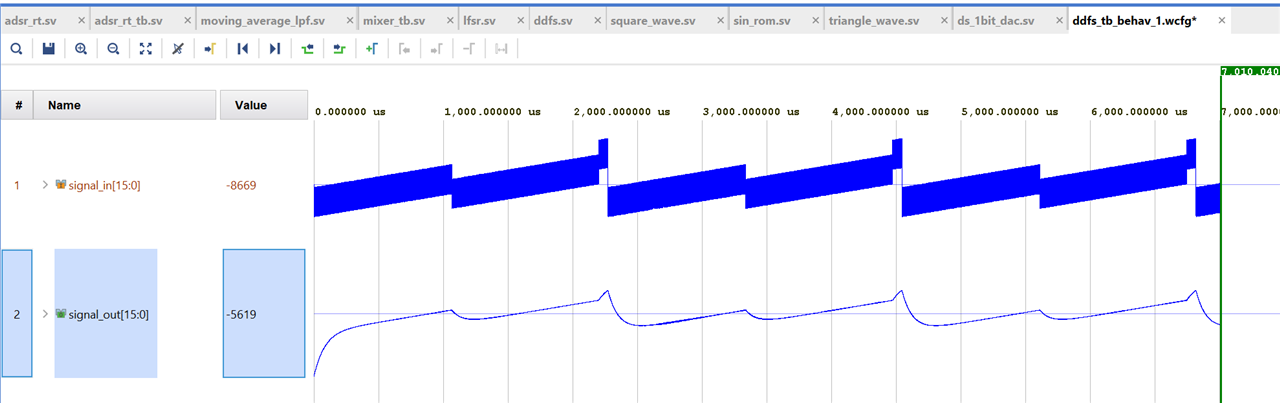

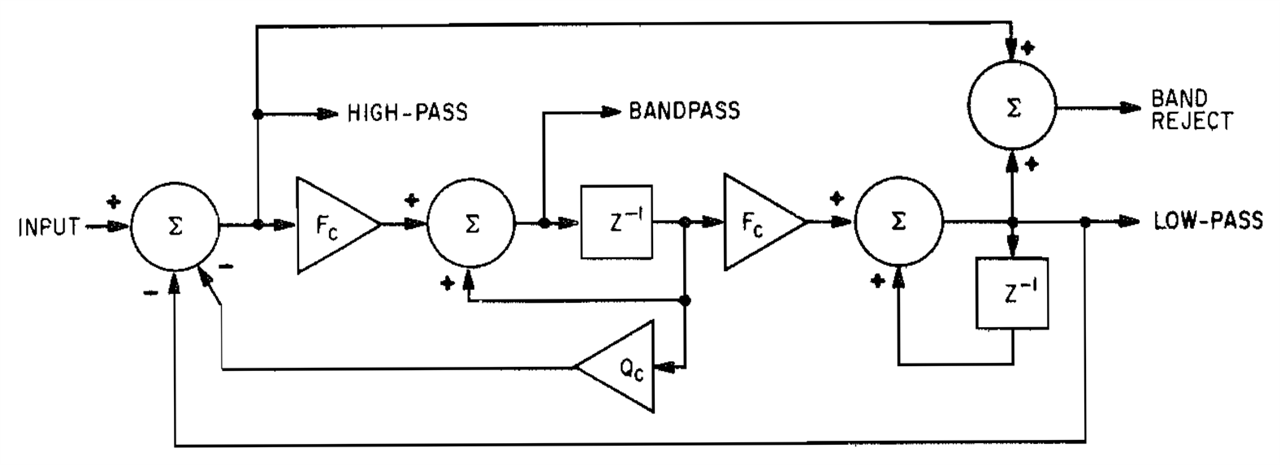

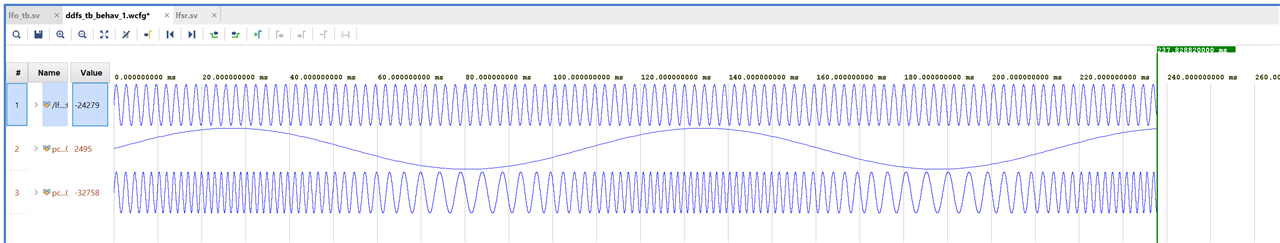

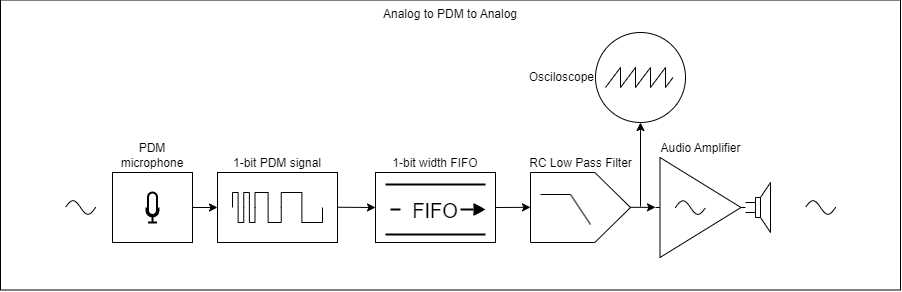

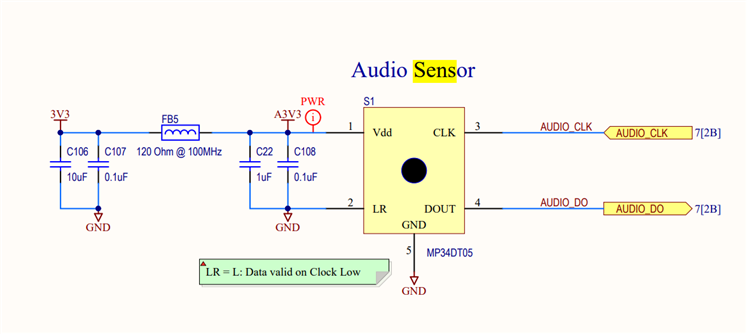

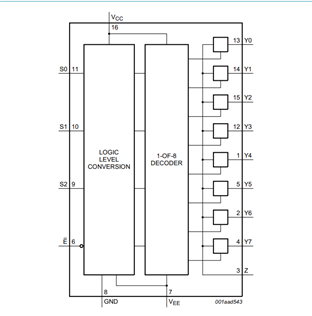

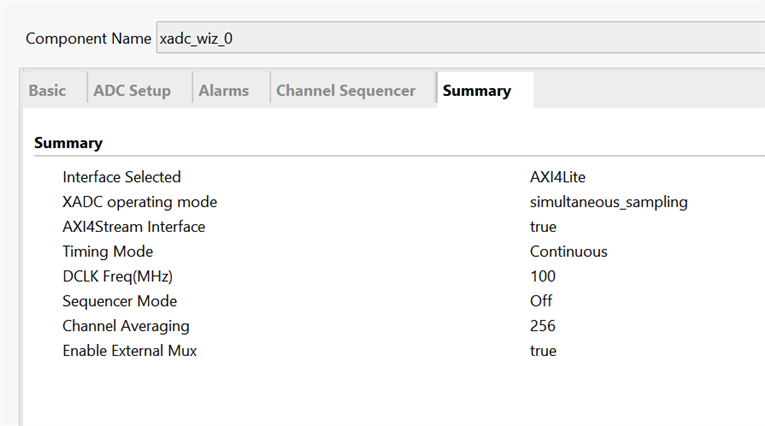

- set (i.e., write) the value of the Amplifier ADSR envelope generator configuration, steps for the release segment, adsra_r