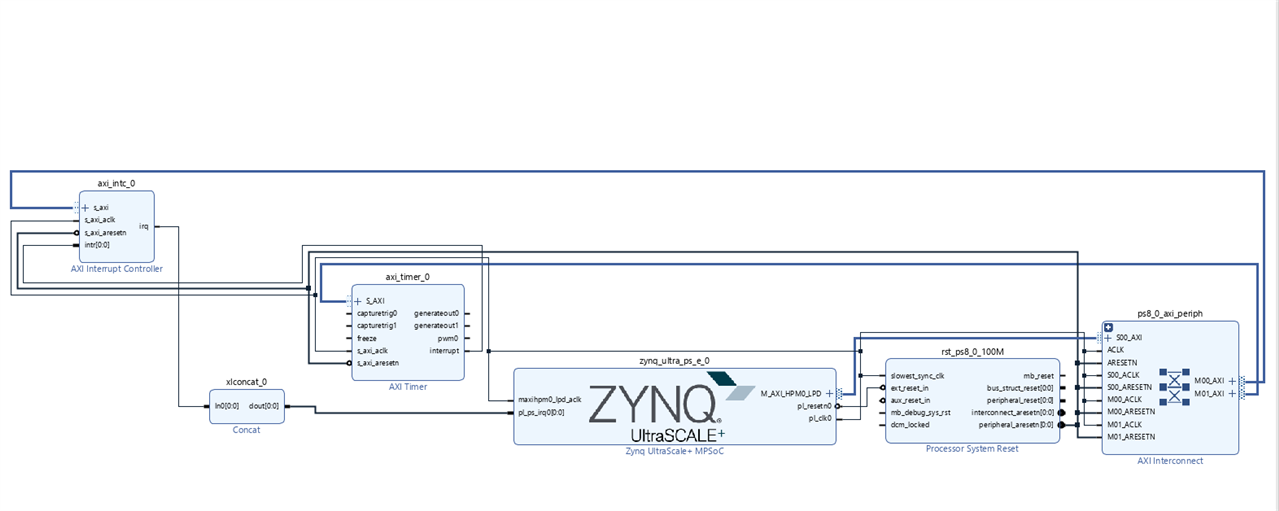

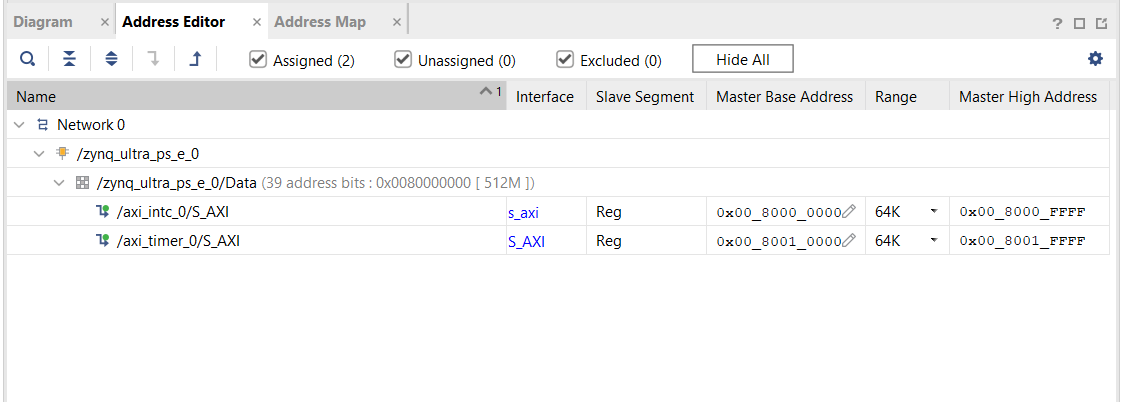

I ran sample code from the "Using GPIO, Timers and Interrupts" on my Utra96v2 board. It worked ok, with the timer pulsing at 1 Hz connected to the IRQ input of the Zynq US+ Processing System block triggering an interrupt. My understanding is that this is using the GIC, which is the interrupt hardware present on the ARM processor (I was running it bare metal on the R5). I also know that there's an AXI Interrupt Controller IP and was wondering when I would use one approach - connect to the Zynq processor system directly - versus connecting to the AXI Intc and then to the PS. This is more of a design question than problem.