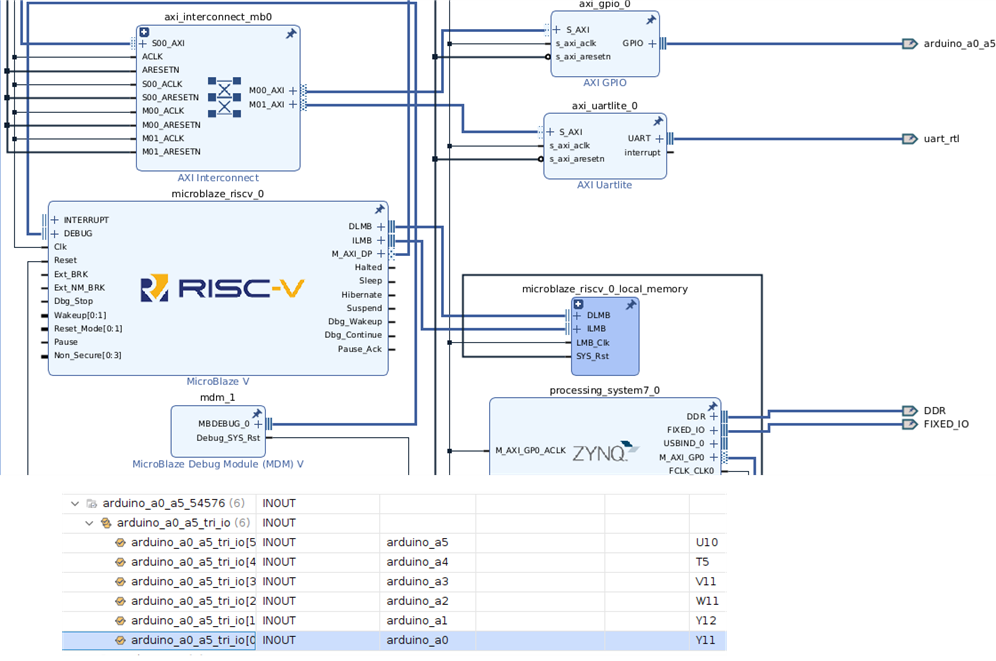

I've made a Vivado 2024.1 design with a Microblaze RISC-V. With debug functionality. I have done similar activities in the past, With Vivado 2022.1.

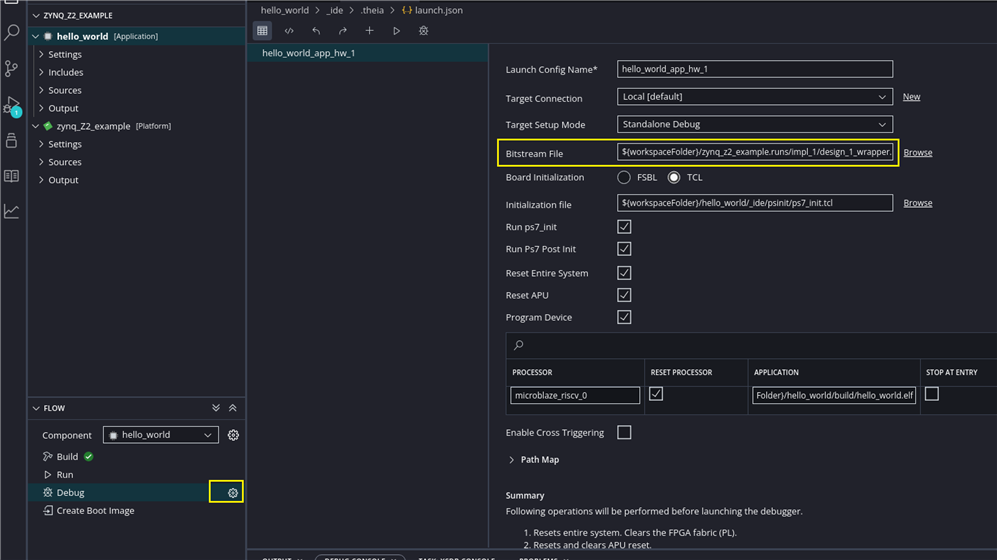

I exported the hardware design, started a Vitis project, and created a simple microblaze Hello application.

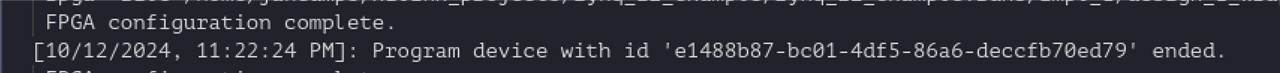

Vitis knows the Microblaze is there. The application builds in Vitis without issues. I also can load the bitstream file to the FPGA, over JTAG.

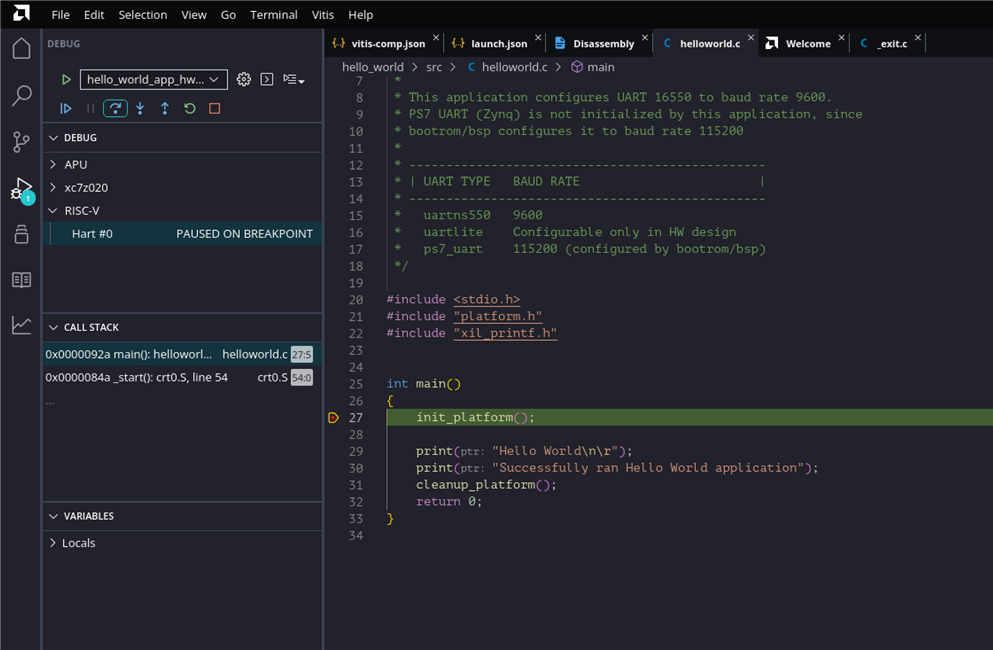

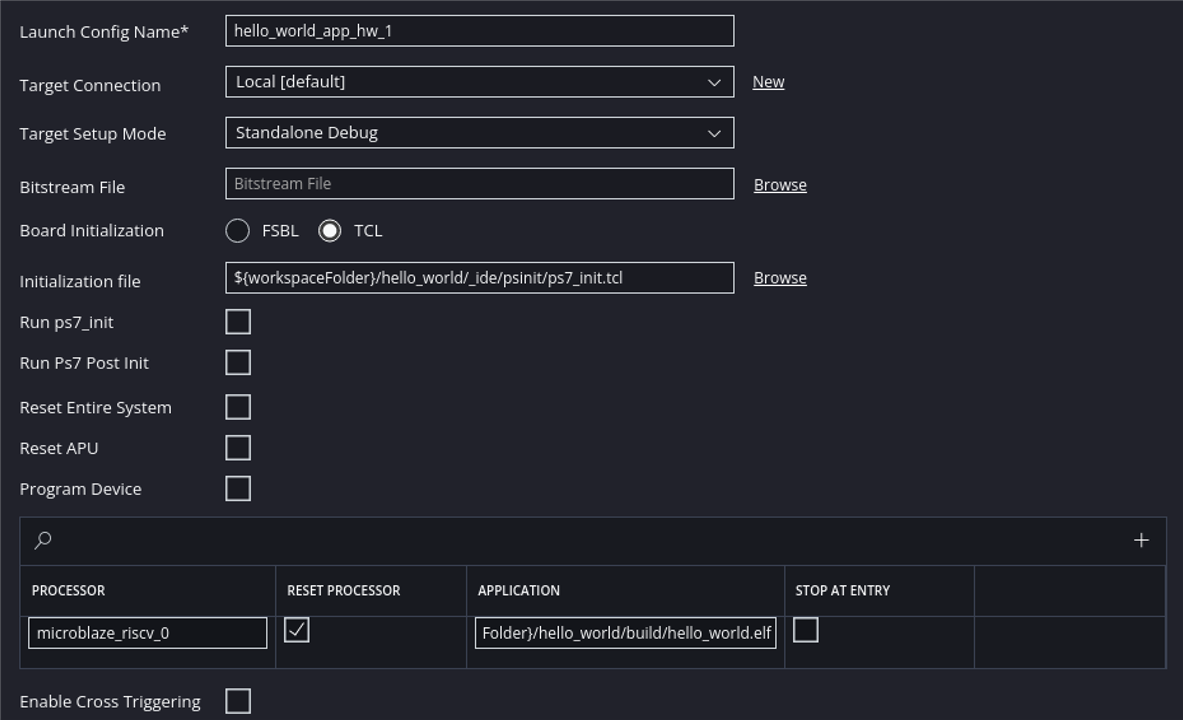

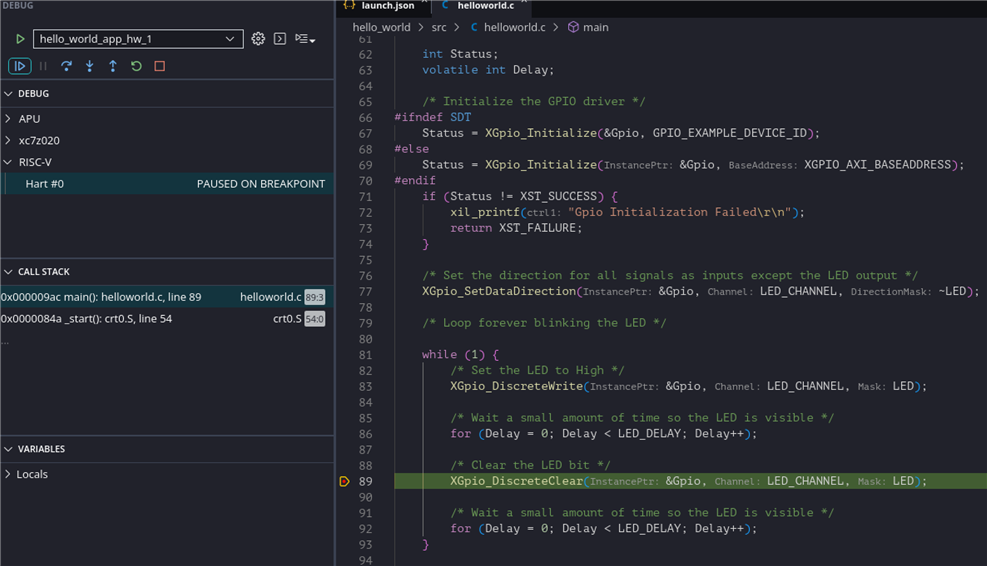

But when I want to program the MicroBlaze, or debug it, the debugger doesn't find the core. It finds the two ARM cores inside the Zinq, but not the MB I designed in fabric.

I have this working in Viado / Vitis 2022.1, where they aren't using the Unified IDE yet.

Vitis can load the bitfile without issues, over JTAG:

But when starting the programmer or debugger, it doesn't find the MicroBlaze in the JTAG chain.

Error:

no targets found with "name =~ "Hart*"". available targets: 1* APU 2 ARM Cortex-A9 MPCore #0 (Running) 3 ARM Cortex-A9 MPCore #1 (Running) 4 xc7z020

I found same errors on google, but no solutions that worked ...