As promised in my post about USB PD - CC decoding adventures, here is the conclusion of my journey to a usable tool to debug USB-PD messages on the CC interface. It also shows that picking the correct opamp characteristics is not only a good idea, but makes the circuit work.

I decided to build a board to pick up the CC1/CC2 signals and amplify them from a 1.2 V to ~3.3 V high level through a simple non-inverting op-amp with a gain of 2.5. The op-amp is a ST Micro TSV992 dual op-amp with 20 MHz GBW and 10 V/usec slew rate. I still made a mistake picking this particular part, as the datasheet clearly states it is stable for gain >4 only. I might have gotten lucky as I don't see any instability/oscillation in my setup. The part is a standard pinout for a dual op-amp, so the board is still useful and rev 1.1 will use a different op-amp.

Here is the schematic, board and pictures of the setup.

| {gallery}CC Monitor |

|---|

|

CC Monitor Schematic |

|

Bare board front (who has good eyes?) |

|

Bare board back |

|

Populated board |

|

|

| Test setup |

The test setup is straight forward with a ON Semi 60W PD eval board as source (not pictured), USB-C cable, the CC Monitor/ a TC66/C and my trusted CYPD3177 sink board. The sink is configured to request a fixed voltage contract of 5V / 1A. The CC Monitor has 2 dual pin headers to connect an oscilloscope and logic analyzer as CC decoder at the same time. It also has 2 linear regulators, because my standard part was out of stock everywhere and this gave me options. Of course, there are different pinouts for a simple linear regulator in SOT-89 package, magic smoke shall be expected. Both regulators are high voltage input up to 20V to be useful for the full USB-PD standard range and only one should be connected through a 0 Ohm resistor. As you can see, I like symmetry.

To show correct functionality, below is a scope capture of a CC transmission. Blue channel 2 is the CC signal as it appears on the USB-C interface with a voltage level of ~1.2V. Yellow channel 1 is the amplified signal that is used as the input to the logic analyzer. It replicates the nice slope at the rising and falling edges as a result of the sufficient slew rate and the overall 1s and 0s are also present with good symmetry, so the overall bandwidth is not exceeded as well.

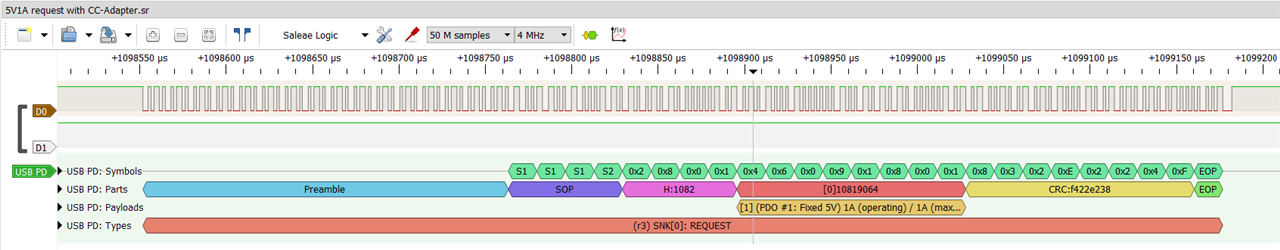

And because I really like the Pulseview/Sigrok PD decoder here is another image of a decoded packet showing the sink request for a fixed 5V/ 1A contract.

Now I have a nice tool to debug my attempt to design a USB-C PD source. As usual, I will write in more detail when I have a working design.

Useful links:

If anybody is interested, the board can be ordered at OSHpark. Did I mention that I find the afterdark option really useful and sexy.

shabaz's USB PD recent blog posts:

USB Type-C and Power Delivery: Any Interest?

100W USB Type-C Power Delivery Source: Getting Started

baldengineer's post about opamp characteristics