Introduction

Switching between hardware devices doesn't just involve making improvements, or fixing bugs. in this case we are talking about changes in the architecture. This blog will help you to better understand how the new device works and how to take advantage of its best advantages. For example, sometimes we want more speed because we are working with signal or image processing. Other times we want to connect with other hardware devices more easily, to have flexibility in solutions. Even, we must have a basic knowledge to migrate an old code to its new version of software.

Spartan®-6 devices offer industry-leading connectivity features such as high logic-to-pin ratios, small form-factor packaging, MicroBlaze soft processor, and a diverse number of supported I/O protocols. Ideally suited for a range of advanced bridging applications found in consumer, automotive infotainment, and industrial automation. Below I show you a Spartan-6 series device.

Spartan®-7 devices, the newest addition to the Cost-Optimized Portfolio, offer the best in class performance per watt, along with small form factor packaging to meet the most stringent requirements. These devices feature a MicroBlaze soft processor running over 200 DMIPs with 800Mb/s DDR3 support built on 28nm technology. Additionally, Spartan-7 devices offer an integrated ADC, dedicated security features, and Q-grade (-40 to +125°C) on all commercial devices. These devices are ideally suited for industrial, consumer, and automotive applications including any-to-any connectivity, sensor fusion, and embedded vision. Some of the most popular devices in the Spartan-7 family are shown below:

Logic

- Both the Spartan-6 and 7 series have a function generator which consists of a six input Look Up Table (LUT) with two associated flip flops. Several of these function generators and flip flop structures are combined to create a slice. Each slice contains eight function generators and 16 flip flops. Within 7 series devices, there are two types of slices -- Slice_M and Slice_L.

- While Slice_M and Slice_L are identical between the Spartan-6 and 7 series devices, Spartan-6 devices also have a Slice_X. Functions that were implemented using a Slice_X can be easily accommodated within the Slice_L, which are available within the 7 series. Migration to Slice_L in 7 series devices can result in performance improvement.

RAM

- Spartan-6 block RAMs are arranged as 18Kb blocks which can be configured as two 9Kb memories. In comparison, 7 series devices provide 36Kb blocks which can be configured as two 18Kb memories.

- 7 series block RAM offers the designer several significant improvements which can be very useful. This includes capabilities like providing build in FIFO, cascading block RAMs, and built-in error correction codes.

DSP

- Being able to leverage the parallelism of programmable logic to implement filters, FFTs, and arithmetic algorithms is a key benefit of FPGA implementation. Both Spartan-6 and Spartan-7 provide dedicated DSP (Digital Signal Processor) slices that enable the developer to implement multiply accumulate functions.

- In the Spartan-6, the developer is provided with a DSP48A1 which provides 18x18 signed multiplication while 7 series devices play DSP48E1 which implements a 25x18 signed multiply.

- To implement advanced modes such as SIMD ( Single Instruction/Multiple Data,), language templates are provided in the Vivado editor to allow ease of implementation to achieve the best performance.

Clock

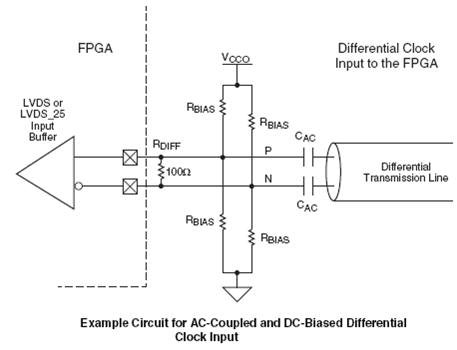

- The clocking architecture of 7 series devices is significantly simpler than that previously provided in the in Spartan-6 devices. Clocking in Spartan-6 has different buffer types which determined connections and connectivity, for example, BUFG, BUFH, and BUFIO2 or BUFPLL. Resource wise, the Spartan-6 FPGA provides the developer with Digital Clock Managers (DCM) and Phase Locked Loops (PLL) clocking resources.

- 7 series devices provide the user with a simpler clocking architecture which, along with flexibility, provides a significant improvement in performance. Within a 7 series Clock Management Tile (CMT), MMCM and PLLs are provided and associated with each I/O bank.

Memory Interfaces

- Both Spartan-6 and 7 series devices provide the user with the ability to achieve interface with high-performance external memories. However, the Spartan-6 implementation uses an integrated memory block whereas 7 series devices use a Soft IP core to implement the memory controller where only the memory 6 PHY is hardened. This provides 7 series devices with a more flexible approach to support DDR3, DDR3L, DDR2, and LPDDR2.

Transceivers and PCIe

- Spartan-6 LXT devices provide the developer with multi-gigabit transceivers in the GTP at a maximum speed of 3.2 Gb/s. 7 series devices which support transceivers can support higher data rates or up to 6/25 Gb/s. 7 series GTPs provide a quad implementation per tile compared to the dual-tile GTP in Spartan-6 architecture. 7 series devices support both PCIe Gen 1 and Gen 2 in the Artix-7 range. This allows the user to benefit from greater performance as bandwidth is significantly increased if desired since 30% faster performance than 45nm generation devices.

XADC

- The 7 series range also introduced new XADC. The XADC is a 1 MSPS ADC which enables the developer to observe the internal supply voltages and die temperature. This can be very useful when implementing self-test and anti-tamper features. Also is enhanced in the XADC the provision of AES256 CBC encryption and SHA-256 authentication.

Total Power Reduction

- In the Spartan-6 series it has Zero power with hibernate power-down mode, and 1.2V core voltage or 1.0V core voltage option.

- Instead, in the Spartan-7 series it has 50% lower total power than 45nm generation devices, and 1.0V core voltage or 0.95V core voltage option.

RTL Migration and MicroBlaze Migration

- We also need to address the change of development tool which comes with migrating from Spartan-6 to 7 Series devices. Vivado is a step change in capability from ISE, however, we are still able to bring across RTL and generate programming files. Exactly how much of the design can migrate depends upon the design itself. For example, a pure RTL design will provide a high level of migration, while a MicroBlaze solution may result in a re-architecting of the MicroBlaze solution, by leveraging IP integrator and pulling in specific RTL modules from the previous design.