The Arty-S7 resource page has an archive of the Out-of-Box (OoB) Vivado project that's loaded in the Flash of your new board. Each time you power it on, this design will be loaded. When you load your own bitfile to Flash, the OoB is overwritten. Here are the steps to recreate it. Valid for the board files in the Digilent github repo at the time of writing, tested with Vivado 2020.2.

There are two steps to do when upgrading: change te board file version in the create script, and update IPs.

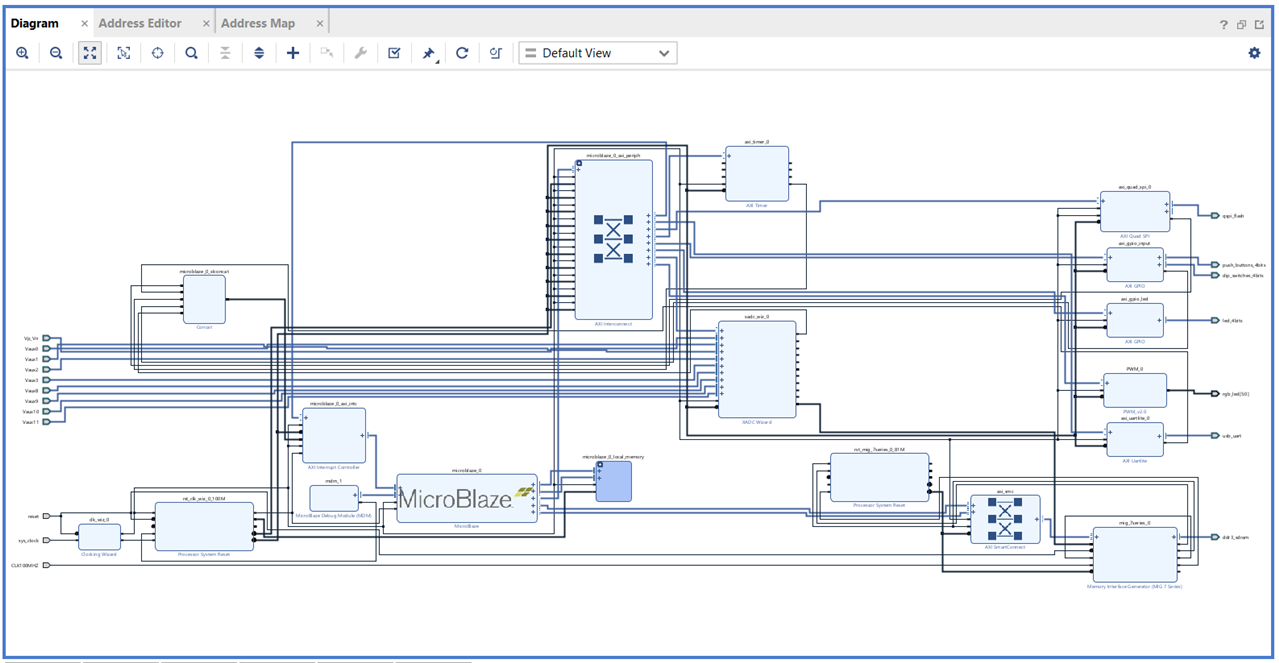

Once you completed these two steps, you have to rebuild the firmware for the MicroBlaze. I will review this in part 2. If you just want to re-load the full original OoB experience right away, without building it for source: the bitstream is available in the ZIP's OoB-Demo-2017.2.1-1/prebuilt subfolder.

Download and extract the OoB example

At the bottom of the reference page, you'll find a download link named Out-of-Box Demo source code (S7-50 variant). This will download the Vivado 2017.2.1-1 version of the project to your PC. Unzip this archive. Don't use a too deep path when working in Windows, because there's a max path of I believe) 255 characters, and Vivado creates some subdirectories.

Update the Board version

Check what Arty board version you installed on your development PC. The easiest way is to open the last project you made for the Arty, then check in the Project Manager view what version you're using.

Edit the file OoB-Demo-2017.2.1-1/source/Arty-S7-50-baser/proj, and save.

set part "xc7s50csga324-1" # set brd_part "digilentinc.com:arty-s7-50:part0:1.0" set brd_part "digilentinc.com:arty-s7-50:part0:1.1"

Generate the Vivado project

Open Vivado, and from the TCL console, navigate to the directory where you extracted the archive.

cd C:/Users/jancu/Documents/elektronica/digilent/arty/oob/OoB-Demo-2017.2.1-1/source/Arty-S7-50-base/proj

Execute the project creation script:

source ./create_project.tcl

This command will end with errors. This is expected, because several IPs that come with Vivado have a newer version.

Unable to generate top-level wrapper HDL for the block design 'system.bd' is locked. Locked reason(s):

* Block design contains locked IPs. Please run report_ip_status for more details and recommendations on how to fix this issue.

Upgrade IPs

After the creation script ends in error, the Vivado IDE shows a command to run the IP Status report, near the top of the block design. Click it. This will open a window with all the IPs that need to be updated. By default, all IPs that need attention are selected. And that's what you want.

Press the Update button, and Vivado will upgrade all the blocks.

Create Wrapper and Generate bitfile

Right click on the board design, and let Vivado create the wrapper for you. Voila, you can now generate the bitstream. In the next part, we'll rebuild the MicroBlaze firmware with Vivado.