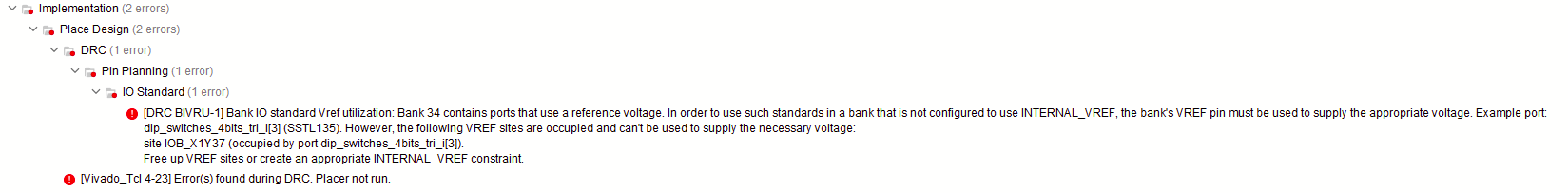

I'm using Vivado 2020.2 and I used the Digilent information to add its boards to Vivado. I implemented a small system but when I tried use the dip switches I got the following error.

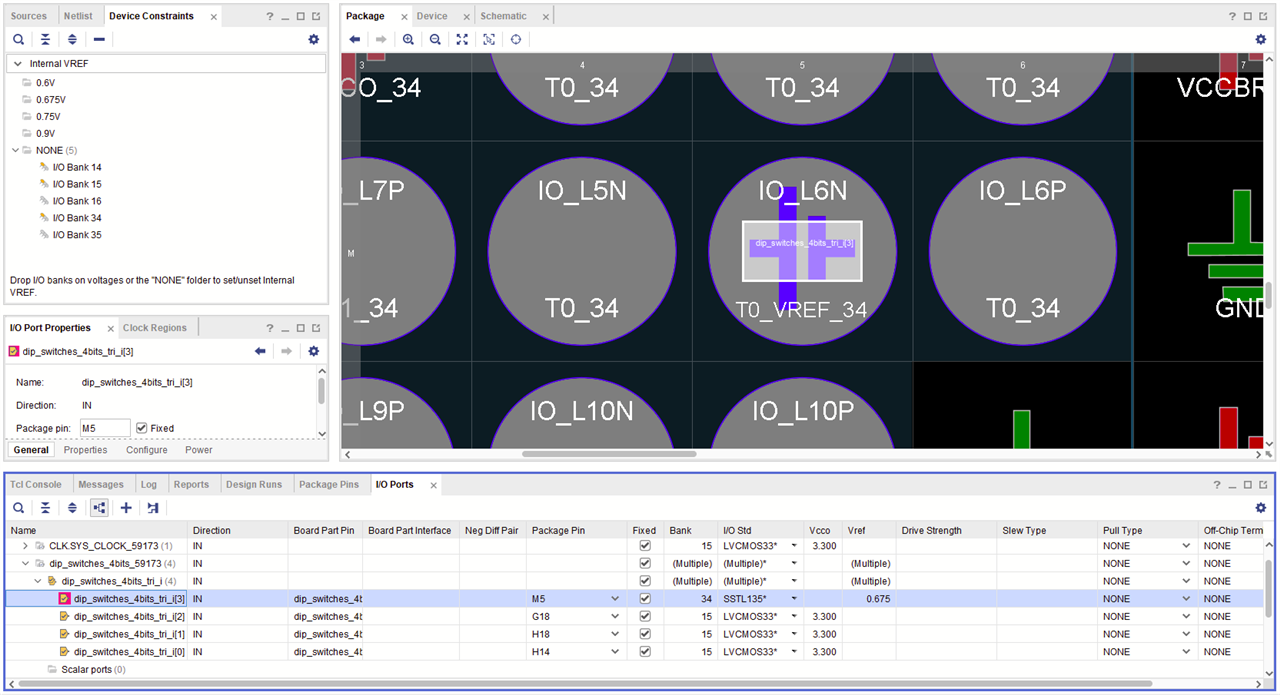

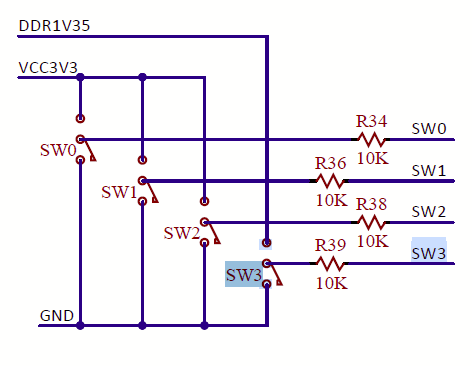

I checked the schematic and it shows dip_switches_4bits_tri_i[3] has 1V35 input, but I do not know how to solve this specific issue. The following illustrates the evidence