My initial idea for the last training blog on the "Path to Programmable 3" challenge was to dedicate it to write about my experiences tinkering with the WIFI and Bluetooth communication of the MiniZed dev board. The road soon went wrong.

There are only drivers for the Murata module for Linux and the documentation is not accessible or I can't find it. So I had to reset the schedule one more time and start the Petalinux training course.

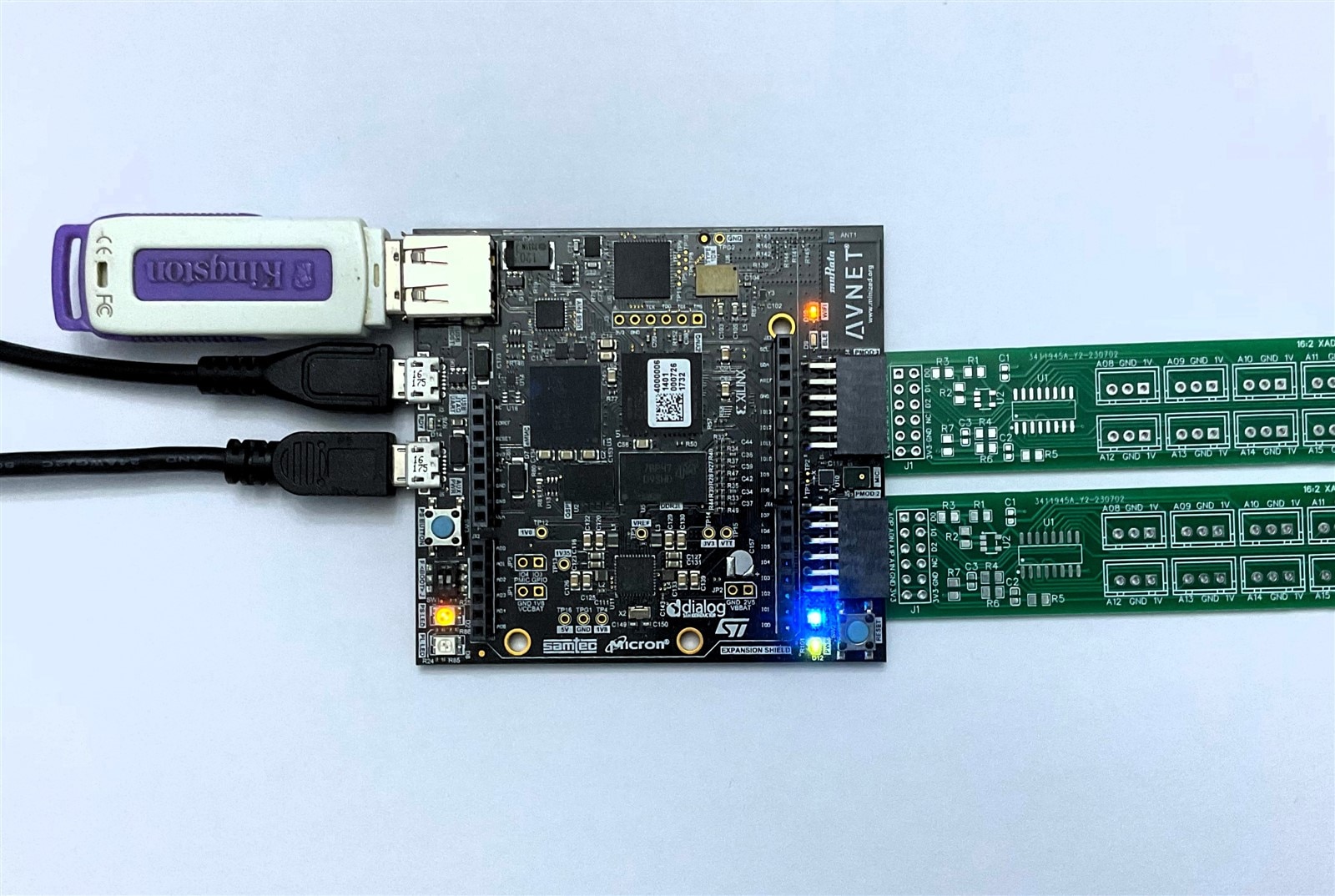

During all the experiments in this blog it is recommended to use the second USB power connector to power the USB Host interface of the Avnet MiniZed development board as in the image.

Table of Contents

- Murata LBEE5KL1DX wireless module

- MiniZed Wireless - Sensors Schematic

- Wireless module software support

- Zynq to wireless module interface

- Wireless Manager VHDL Adapter

- Going to Petalinux

- PetaLinux Project Structure

- Petalinux commands

- Creating and Installing Petalinux images

- Program Flash the PetaLinux image onto the MiniZed via QSPI

- Booting from Flash

- Installing Full Image of PetaLinux to eMMC

- Connect MiniZed to a LAN with Wi-Fi

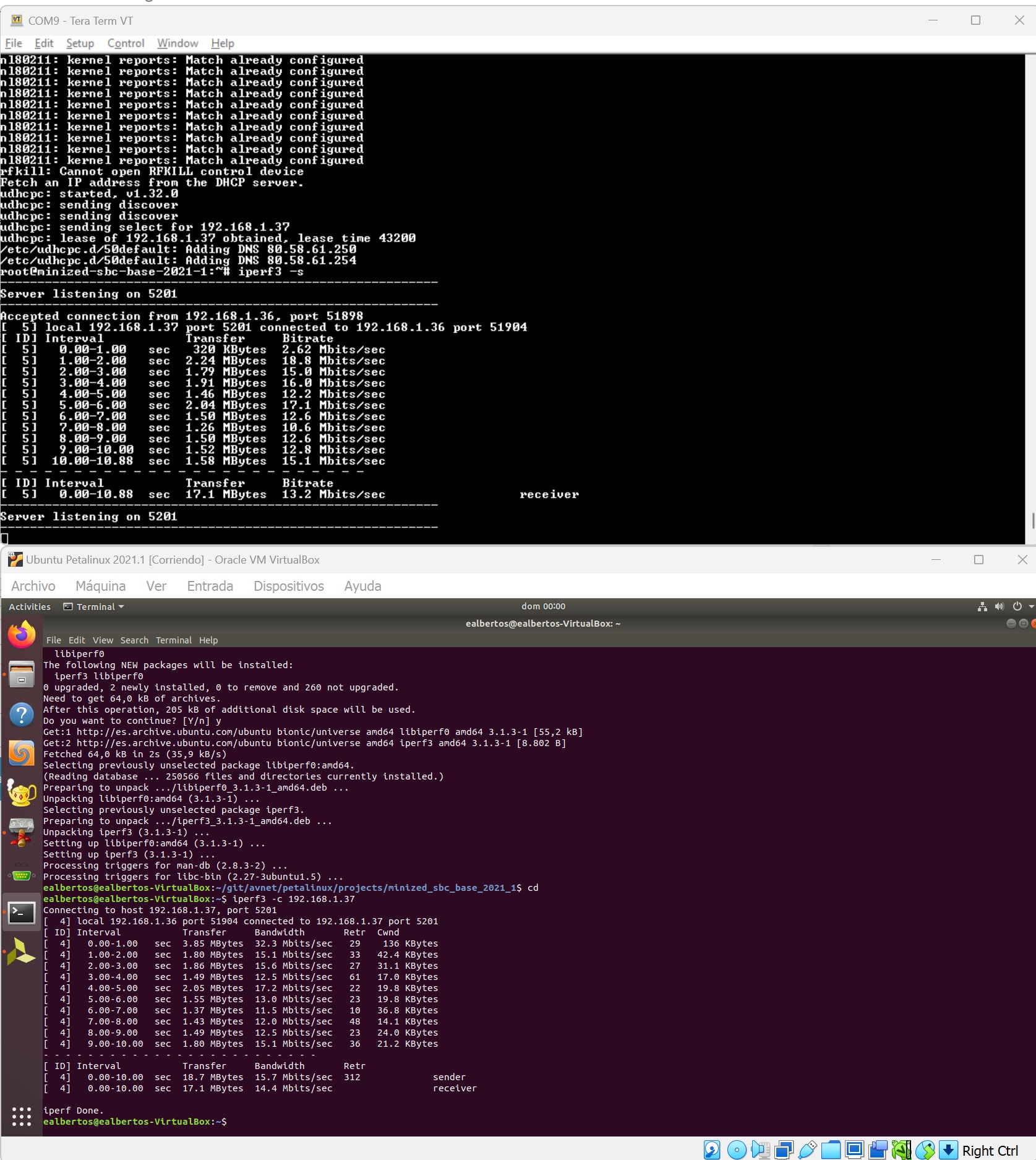

- Checking packets transfer with iperf3.

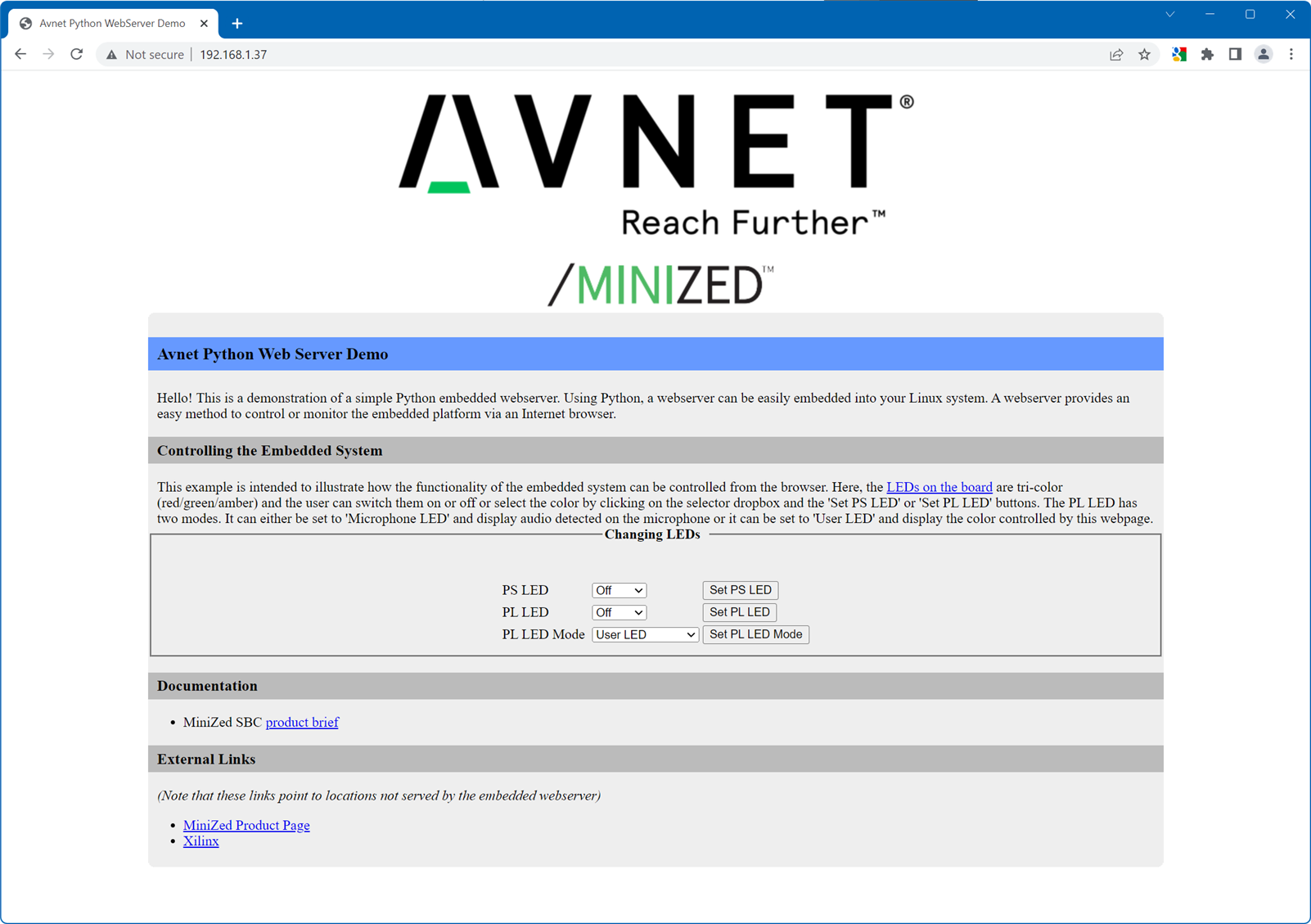

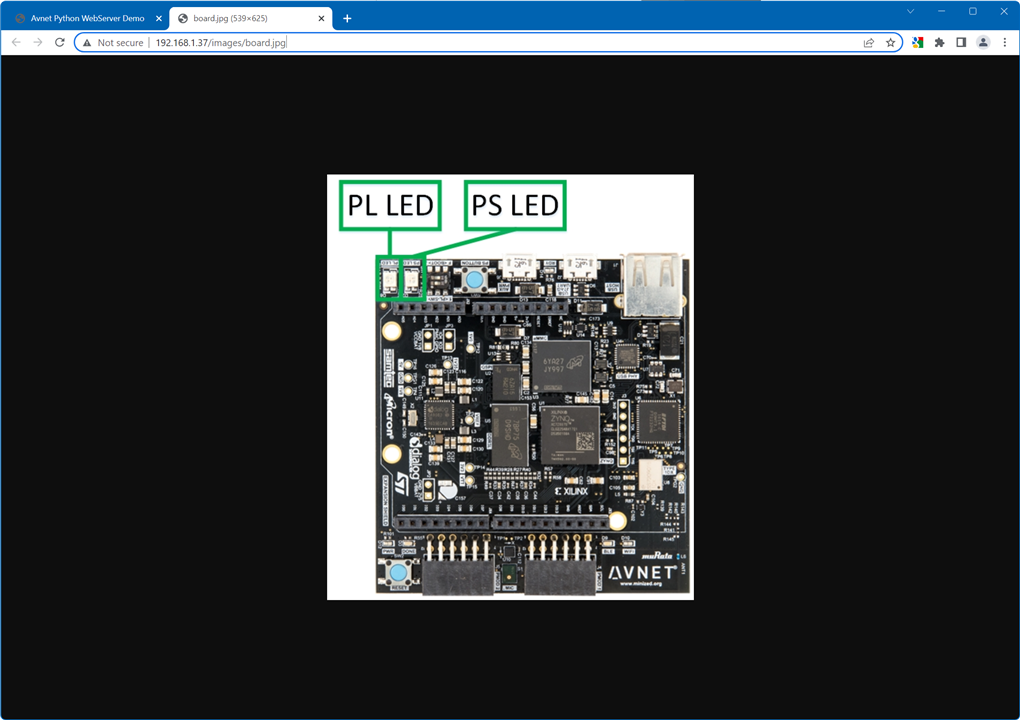

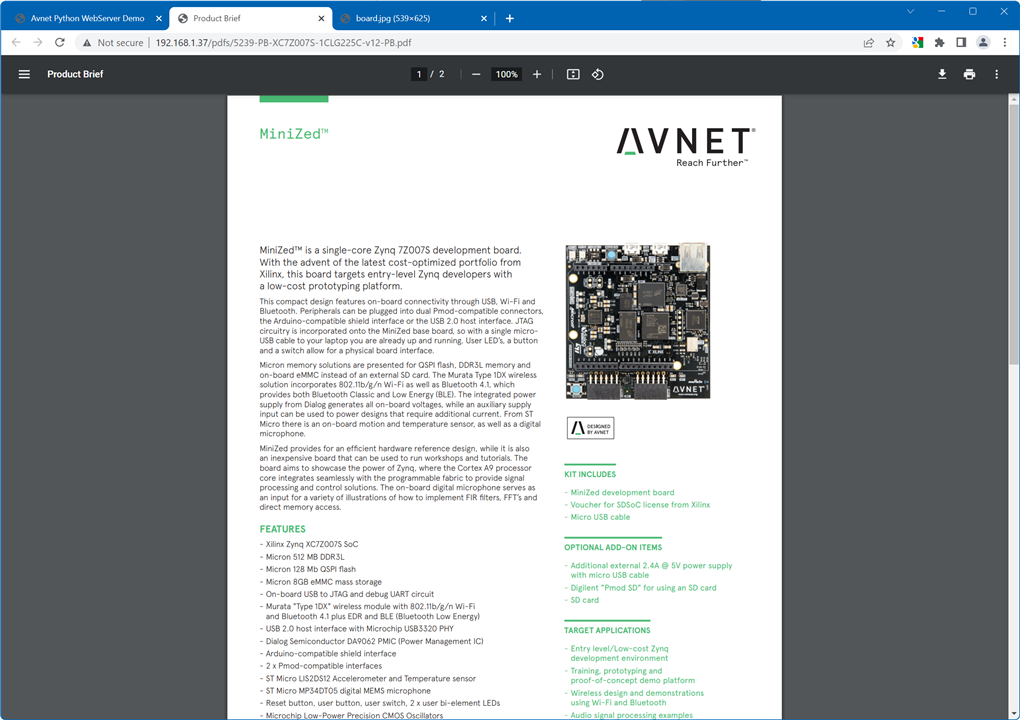

- Checking the Webserver Demo

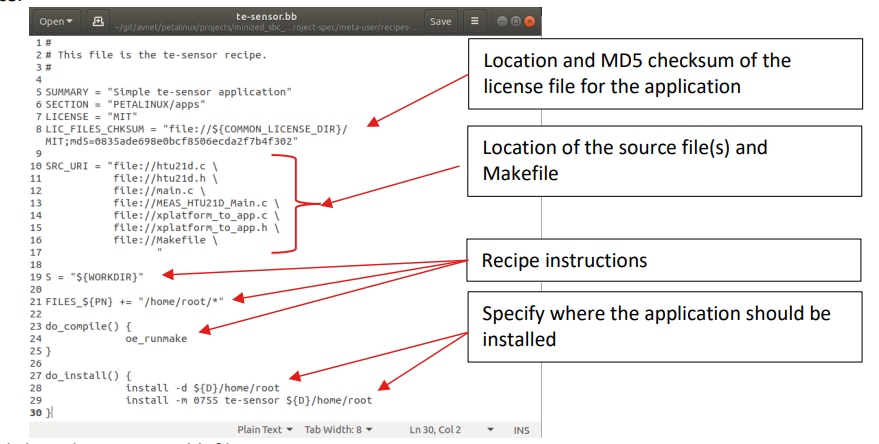

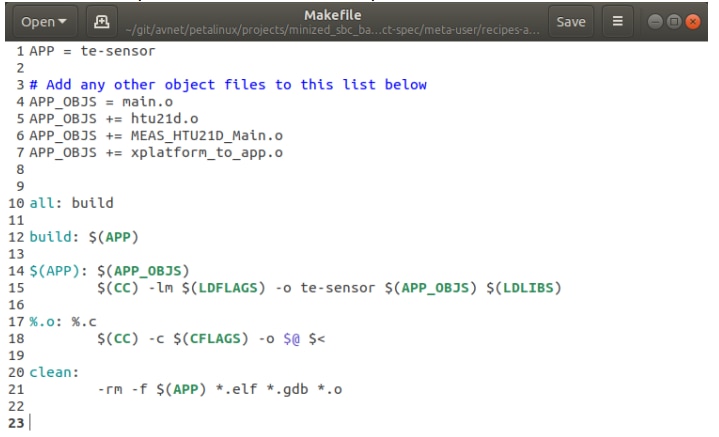

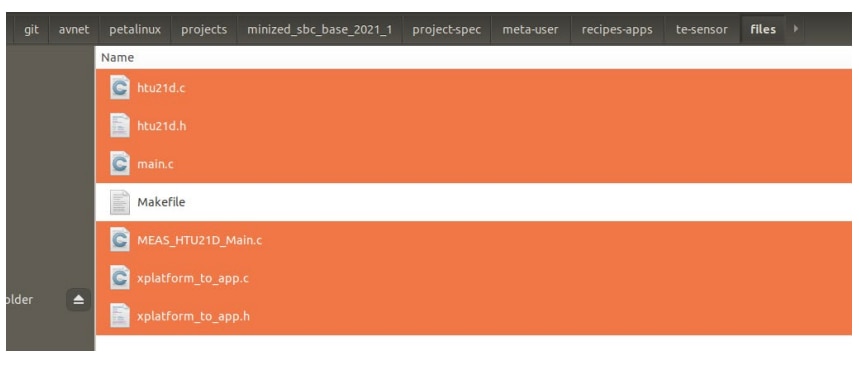

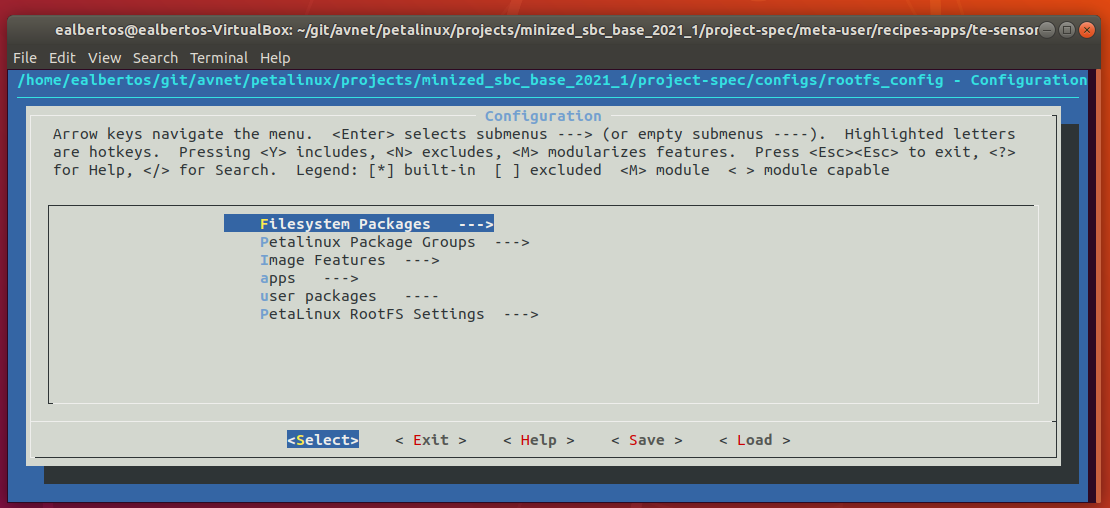

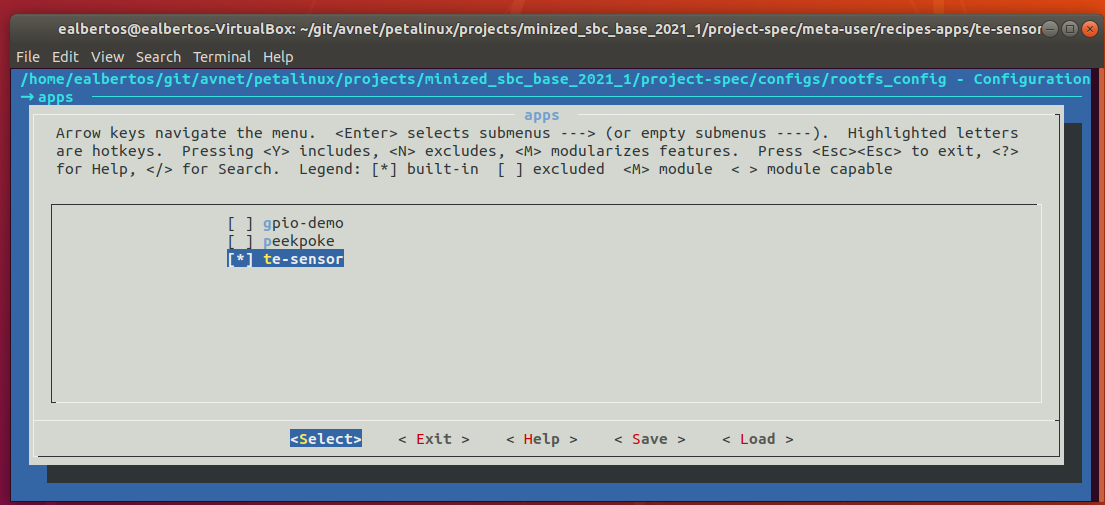

- Build a New PetaLinux Image including our own App

- Restoring MiniZed to the Factory State

- Programming the QSPI Flash Using XSCT

- Updates on my training path

- Conclusion

- Path to Programmable III Training Blog Series

Murata LBEE5KL1DX wireless module

I started by looking at the built-in Murata LBEE5KL1DX wireless module on the Avnet MiniZed development board. The Murata LBEE5KL1DX is a module that supports Wi-Fi 802.11b/g/n and Bluetooth 4.1/EDR.

References for the LBEE5KL1DX-883

- https://www.murata.com/en-us/products/connectivitymodule/wi-fi-bluetooth/overview/lineup/type1dx

- https://www.murata.com/products/productdata/8813651165214/type1dx.pdf

- CYW4343W Single-Chip 802.11 b/g/n MAC/Baseband/Radio with Bluetooth 4.1 (infineon.com)

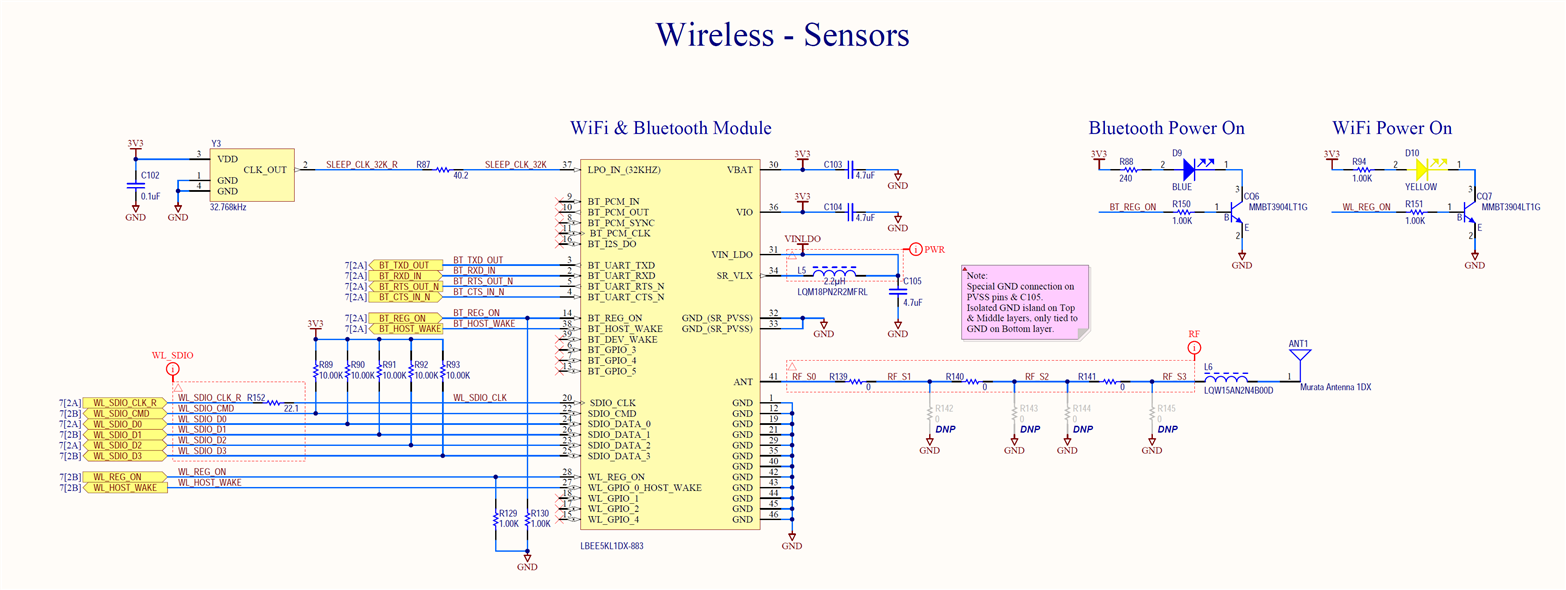

MiniZed Wireless - Sensors Schematic

Extract of the schematic of the Avnet Minized development board where we can locate the Murata wireless communications module.

Wireless module software support

As for software support, that's where my problems began. I was hoping that there would be a driver or enough information to communicate in bare metal with the module, but it is not. Unfortunately standalone Zynq projects are not supported, only Linux using either the bcmdhd or brcmfmac Broadcom drivers are supported.

I didn't want to get into Petalinux training yet as I knew it would be very tedious and I would have to switch from windows to Linux learning environment and from a powerful native windows machine to a snail-like virtual machine.

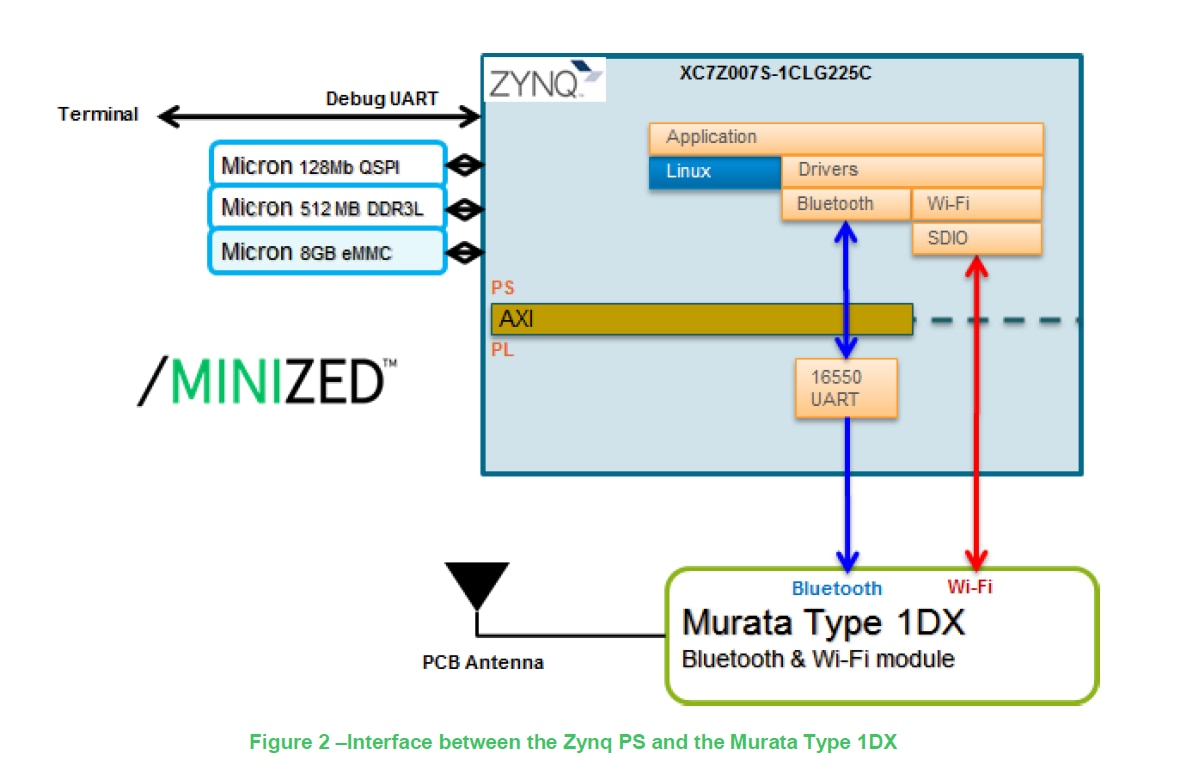

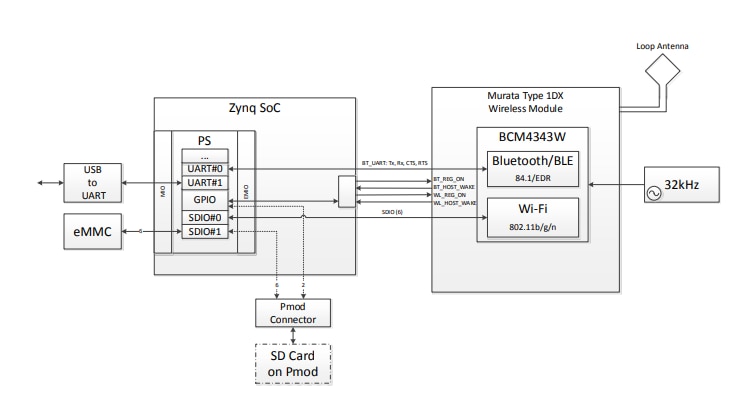

Zynq to wireless module interface

The diagram shows how the Zynq PS peripherals are connected to the 1DX module.

- All wireless I/O are connected via EMIO

- All 4 UART signals (Tx, Rx, CTS and RTS) are used for the Bluetooth/BLE interface

- All 6 SDIO signals are used for the Wi-Fi interface

- 4 of the 1DX GPIO signals are connected for handshaking

- BT_REG_ON

- BT_HOST_WAKE

- WL_REG_ON

- WL_HOST_WAKE

- The PCM interface is not connected. This is typically used for driving a Bluetooth speaker directly

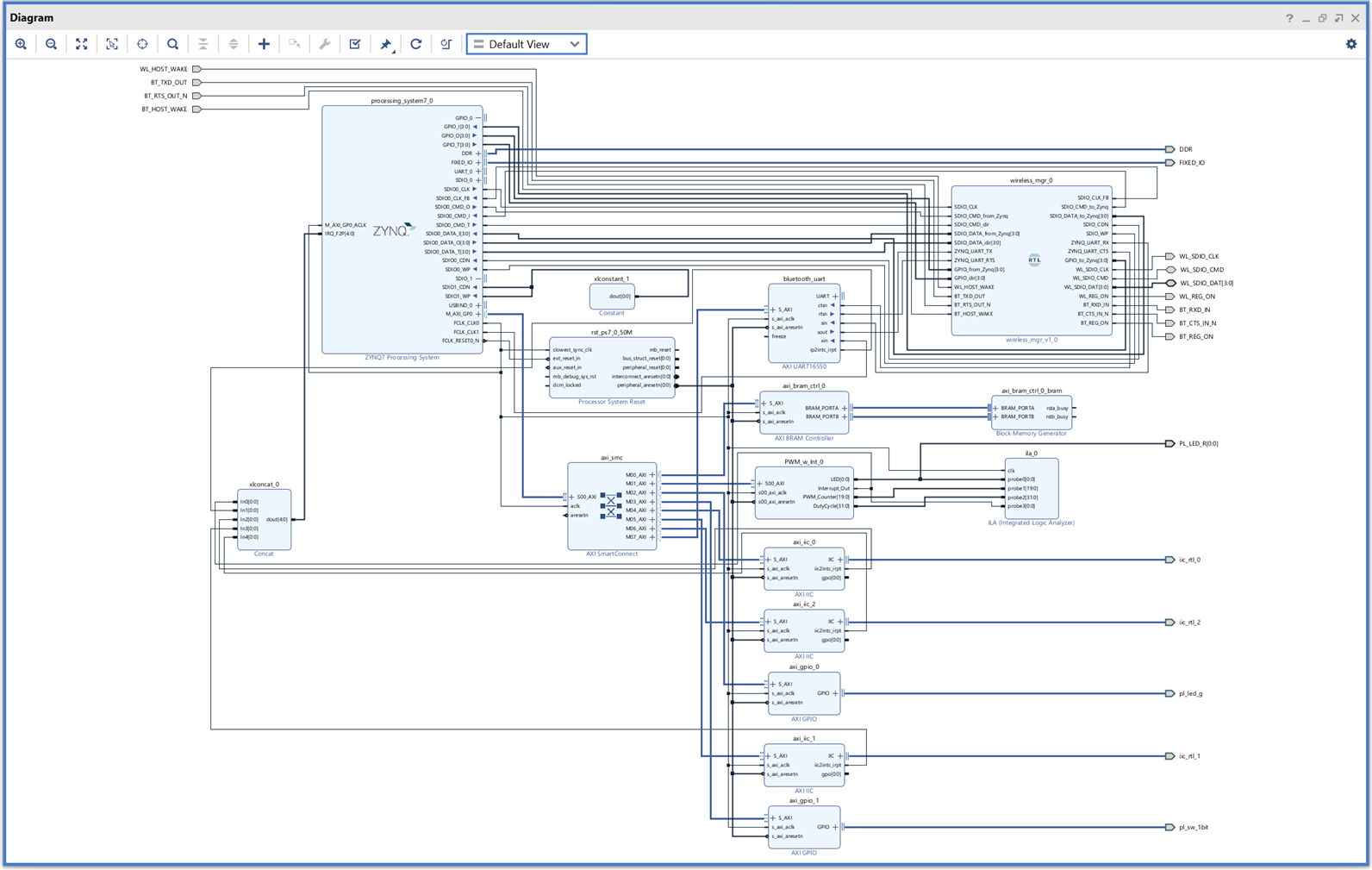

Wireless Manager VHDL Adapter

In order to easily incorporate wireless communications, Avnet provides us with a VHDL module that routes and acts as a buffer for the SDIO communications of the WIFI module and the UART of the Bluetooth module.

We can add, for example, to a block design or instantiate it directly from another module, it does not have any type of AXI control.

And a complete design created from scratch in Vivado version 2022.2 and 2022.1. With Vivado 2022.2 version Vivado generates an exception when generating the bitstream, but it works fine with Vivado 2022.1

There is no software support for bare metal applications (Zynq standalone), so we will go the way of Petalinux.

Going to Petalinux

I have followed the first two parts of the training, Software and Hardware, using AMD Vivado ML version 2022.2. It has been a very good experience and I have hardly had any problems that have been easily solved.

Since version 2022.2 has been very friendly to me, I thought about installing the same version of Petalinux in a virtual machine with Ubuntu. The Petalinux installation went well. My problems started with not finding Avnet support for Minized with this version of AMD Vivado ML tools. So after dozens of lost hours, I returned to the path marked out by the course and reinstalled version 2021.1 of Vivado.

PetaLinux Project Structure

A built Linux system is composed of the following components:

- Device tree

- First stage boot loader (optional)

- U-Boot

- Linux kernel

- The root file system is composed of the following components:

- Prebuilt packages

- Linux user applications (optional)

- User modules (optional)

A PetaLinux project directory contains configuration files of the project, the Linux subsystem, and the components of the subsystem. The petalinux-build command builds the project with those configuration files. You can run petalinux-config to modify them.

References:

- PetaLinux Tools for Embedded Linux Development (xilinx.com)

- PetaLinux Tools Documentation: Reference Guide (xilinx.com)

Petalinux commands

There are eight independent commands that make up the PetaLinux design flow. They are:

- petalinux-create:

- petalinux-create -t project workflow, the tool creates a new PetaLinux project directory structure.

- petalinux-create -t COMPONENT workflow, the tool creates a component within the specified project (apps, kernel modules)

- petalinux-config: allows you to customize the specified project or component with a menuconfig interface

- petalinux-build: builds either the entire embedded Linux system or a specified component of the Linux system

- petalinux-boot: boots MicroBlaze CPU, Zynq devices, Versal ACAP, and Zynq UltraScale+ MPSoC with PetaLinux images through JTAG/QEMU software emulator.

- petalinux-package: packages a PetaLinux project into a format suitable for deployment.

- petalinux-util: provides various support services to the other PetaLinux workflows: gdb, dfu-util, xsdb-connect, jtag-logbuf, find-xsa-bitstream

- petalinux-upgrade: To upgrade the workspace

- petalinux-devtool: uses the Yocto devtool to enable you to build, test, and package software.

Creating and Installing Petalinux images

We need to first install a minimum PetaLinux on the Minized using the QSPI Flash that loads from eMMC Flash memory. Then use PetaLinux to program additional larger PetaLinux images.

First step: configure and boot a minimal PetaLinux image.

We will setup and configure a minimal PetaLinux system using the PetaLinux tools. The minimal image will be loaded into the 16MB qspi memory which will be loaded onto the 512MB DDR3L.

It takes a long time to complete a new PetaLinux project. In my case it took about 8 hours. You also can work with the prebuilt images.

First clone the Avnet git repositories. There three repositories and it is recommended no to change the names of the directories.

- git clone https://github.com/avnet/bdf.git / master branch

- git clone https://github.com/avnet/hdl.git / 2021.1 branch

- git clone https://github.com/avnet/petalinux.git /2021.1 branch

It is important to check out the correct branch.

Then to create the BSP we have to execute the make_minized_sbc_base.sh script under petalinux/scripts.

PetaLinux environment set to '/tools/petalinux-v2021.1-final'

INFO: Checking free disk space

INFO: Checking installed tools

INFO: Checking installed development libraries

INFO: Checking network and other services

ealbertos@ealbertos-VirtualBox:~$ cd ~

ealbertos@ealbertos-VirtualBox:~$ mkdir -p git/avnet

ealbertos@ealbertos-VirtualBox:~$ cd git/avnet

ealbertos@ealbertos-VirtualBox:~/git/avnet$ git clone https://github.com/avnet/bdf.git

Cloning into 'bdf'...

remote: Enumerating objects: 654, done.

remote: Counting objects: 100% (58/58), done.

remote: Compressing objects: 100% (30/30), done.

remote: Total 654 (delta 35), reused 33 (delta 26), pack-reused 596

Receiving objects: 100% (654/654), 34.90 MiB | 5.60 MiB/s, done.

Resolving deltas: 100% (323/323), done.

ealbertos@ealbertos-VirtualBox:~/git/avnet$ git clone https://github.com/avnet/hdl.git

Cloning into 'hdl'...

remote: Enumerating objects: 6154, done.

remote: Counting objects: 100% (1817/1817), done.

remote: Compressing objects: 100% (551/551), done.

remote: Total 6154 (delta 1228), reused 1710 (delta 1168), pack-reused 4337

Receiving objects: 100% (6154/6154), 15.13 MiB | 6.90 MiB/s, done.

Resolving deltas: 100% (3792/3792), done.

Checking out files: 100% (1874/1874), done.

ealbertos@ealbertos-VirtualBox:~/git/avnet$ git clone https://github.com/avnet/petalinux.git

Cloning into 'petalinux'...

remote: Enumerating objects: 3880, done.

remote: Counting objects: 100% (809/809), done.

remote: Compressing objects: 100% (165/165), done.

remote: Total 3880 (delta 677), reused 700 (delta 622), pack-reused 3071

Receiving objects: 100% (3880/3880), 6.24 MiB | 7.69 MiB/s, done.

Resolving deltas: 100% (2282/2282), done.

ealbertos@ealbertos-VirtualBox:~/git/avnet$ cd bdf

ealbertos@ealbertos-VirtualBox:~/git/avnet/bdf$ git checkout master

Already on 'master'

Your branch is up to date with 'origin/master'.

ealbertos@ealbertos-VirtualBox:~/git/avnet/bdf$ cd ../hdl

ealbertos@ealbertos-VirtualBox:~/git/avnet/hdl$ git checkout 2021.1

Branch '2021.1' set up to track remote branch '2021.1' from 'origin'.

Switched to a new branch '2021.1'

ealbertos@ealbertos-VirtualBox:~/git/avnet/hdl$ cd ../petalinux/

ealbertos@ealbertos-VirtualBox:~/git/avnet/petalinux$ git checkout 2021.1

Branch '2021.1' set up to track remote branch '2021.1' from 'origin'.

Switched to a new branch '2021.1'

ealbertos@ealbertos-VirtualBox:~/git/avnet/petalinux$ cd ~/git/avnet/petalinux/scripts/

ealbertos@ealbertos-VirtualBox:~/git/avnet/petalinux/scripts$ source /tools/Xilinx/Vivado/2021.1/settings64.sh

ealbertos@ealbertos-VirtualBox:~/git/avnet/petalinux/scripts$ ./make_minized_sbc_base.sh

Verifying repositories ...

Checking Environment (Xilinx tools sourced) ...

Checking 'minized_sbc_base_2021_1' Vivado Project ...

No built Vivado HW project minized_sbc_base_2021_1 found.

Will build the hardware platform now.

****** Vivado v2021.1 (64-bit)

**** SW Build 3247384 on Thu Jun 10 19:36:07 MDT 2021

**** IP Build 3246043 on Fri Jun 11 00:30:35 MDT 2021

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

source make_minized_sbc_base.tcl -notrace

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*- -*

*- Welcome to the Avnet Project Builder -*

*- -*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Selected

BDF path /home/ealbertos/git/avnet/bdf

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Creating projects Folder

+------------------+------------------------------------+

| Setting | Configuration |

+------------------+------------------------------------+

| Board | minized_sbc |

+------------------+------------------------------------+

| Project | base |

+------------------+------------------------------------+

| SDK | no |

+------------------+------------------------------------+

| No Close Project | yes |

+------------------+------------------------------------+

| Device | zynq |

+------------------+------------------------------------+

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Vivado version 2021.1 acceptable,

continuing...

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Selected Board and Project as:

minized_sbc and base

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Not Requesting Tag

*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*-*

Setting Up Project minized_sbc_base...

***** Creating Vivado project...

create_project: Time (s): cpu = 00:00:02 ; elapsed = 00:00:06 . Memory (MB): peak = 2377.695 ; gain = 2.016 ; free physical = 3789 ; free virtual = 8166

***** Setting synthesis language for project to VHDL...

***** Importing constraints file(s)...

***** Assigning Vivado project board_part property to minized...

***** Generating IP...

***** Updating Vivado to include IP folder

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/home/ealbertos/git/avnet/hdl/ip'.

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository '/tools/Xilinx/Vivado/2021.1/data/ip'.

***** Creating block design...

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

create_bd_design: Time (s): cpu = 00:00:00.84 ; elapsed = 00:00:06 . Memory (MB): peak = 2446.016 ; gain = 25.062 ; free physical = 3713 ; free virtual = 8136

***** Adding RTL source Files to design...

***** Adding custom RTL IP blocks to block design...

Making wireless_mgr instance wireless_mgr_0 ...

INFO: [IP_Flow 19-5107] Inferred bus interface 'SDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from Xilinx Repository).

INFO: [IP_Flow 19-5107] Inferred bus interface 'WL_SDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from Xilinx Repository).

WARNING: [IP_Flow 19-5661] Bus Interface 'SDIO_CLK' does not have any bus interfaces associated with it.

WARNING: [IP_Flow 19-5661] Bus Interface 'WL_SDIO_CLK' does not have any bus interfaces associated with it.

CRITICAL WARNING: [IP_Flow 19-4751] Bus Interface 'WL_SDIO_CLK': FREQ_HZ bus parameter is missing for output clock interface.

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/home/ealbertos/git/avnet/hdl/ip'.

Making led_mgr instance led_mgr_0 ...

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/home/ealbertos/git/avnet/hdl/ip'.

Making microphone_mgr instance microphone_mgr_0 ...

INFO: [IP_Flow 19-5107] Inferred bus interface 'clk_in' of definition 'xilinx.com:signal:clock:1.0' (from X_INTERFACE_INFO parameter from HDL file).

INFO: [IP_Flow 19-5107] Inferred bus interface 'clk_in' of definition 'xilinx.com:signal:clock:1.0' (from 'X_INTERFACE_INFO' attribute).

INFO: [IP_Flow 19-5107] Inferred bus interface 'resetn_in' of definition 'xilinx.com:signal:reset:1.0' (from X_INTERFACE_INFO parameter from HDL file).

INFO: [IP_Flow 19-5107] Inferred bus interface 'resetn_in' of definition 'xilinx.com:signal:reset:1.0' (from 'X_INTERFACE_INFO' attribute).

INFO: [IP_Flow 19-5107] Inferred bus interface 'AUDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from X_INTERFACE_INFO parameter from HDL file).

INFO: [IP_Flow 19-5107] Inferred bus interface 'AUDIO_CLK' of definition 'xilinx.com:signal:clock:1.0' (from 'X_INTERFACE_INFO' attribute).

INFO: [IP_Flow 19-4728] Bus Interface 'clk_in': Added interface parameter 'ASSOCIATED_RESET' with value 'resetn_in'.

INFO: [IP_Flow 19-4728] Bus Interface 'clk_in': Added interface parameter 'FREQ_HZ' with value '160000000'.

INFO: [IP_Flow 19-4728] Bus Interface 'AUDIO_CLK': Added interface parameter 'FREQ_HZ' with value '2500000'.

INFO: [IP_Flow 19-7067] Note that bus interface 'clk_in' has a fixed FREQ_HZ of '160000000'. This value will be respected whenever this IP is instantiated in IP Integrator.

WARNING: [IP_Flow 19-5661] Bus Interface 'clk_in' does not have any bus interfaces associated with it.

INFO: [IP_Flow 19-7067] Note that bus interface 'AUDIO_CLK' has a fixed FREQ_HZ of '2500000'. This value will be respected whenever this IP is instantiated in IP Integrator.

WARNING: [IP_Flow 19-5661] Bus Interface 'AUDIO_CLK' does not have any bus interfaces associated with it.

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/home/ealbertos/git/avnet/hdl/ip'.

***** Adding processing system presets from board definition...

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

***** Adding defined IP blocks to block design...

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Device 21-403] Loading part xc7z007sclg225-1

create_bd_cell: Time (s): cpu = 00:00:03 ; elapsed = 00:00:19 . Memory (MB): peak = 2454.023 ; gain = 0.000 ; free physical = 3289 ; free virtual = 7773

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

INFO: [Ipptcl 7-1463] No Compatible Board Interface found. Board Tab not created in customize GUI

WARNING: [IP_Flow 19-3374] An attempt to modify the value of disabled parameter 'MMCM_CLKFBOUT_MULT_F' from '10.000' to '20.000' has been ignored for IP 'clk_wiz_0'

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/xin> is being overridden by the user with net <ps7_FCLK_CLK1>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_0/gpio_io_o> is being overridden by the user with net <axi_gpio_0_gpio_io_o>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_0/gpio2_io_o> is being overridden by the user with net <axi_gpio_0_gpio2_io_o>. This pin will not be connected as a part of interface connection <GPIO2>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_2/gpio_io_t> is being overridden by the user with net <axi_gpio_2_gpio_io_t>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_2/gpio_io_o> is being overridden by the user with net <axi_gpio_2_gpio_io_o>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </axi_gpio_2/gpio_io_i> is being overridden by the user with net <led_mgr_0_GPIO_to_Zynq>. This pin will not be connected as a part of interface connection <GPIO>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO1_CDN> is being overridden by the user with net <xlconstant_1_dout>. This pin will not be connected as a part of interface connection <SDIO_1>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO1_WP> is being overridden by the user with net <xlconstant_1_dout>. This pin will not be connected as a part of interface connection <SDIO_1>.

WARNING: [BD 41-1306] The connection to interface pin </axi_intc_0/irq> is being overridden by the user with net <axi_intc_0_irq>. This pin will not be connected as a part of interface connection <interrupt>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CLK> is being overridden by the user with net <ps7_SDIO0_CLK>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CLK_FB> is being overridden by the user with net <wireless_mgr_0_SDIO_CLK_FB>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CMD_O> is being overridden by the user with net <ps7_SDIO0_CMD_O>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CMD_I> is being overridden by the user with net <wireless_mgr_0_SDIO_CMD_to_Zynq>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CMD_T> is being overridden by the user with net <ps7_SDIO0_CMD_T>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_DATA_O> is being overridden by the user with net <ps7_SDIO0_DATA_O>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_DATA_I> is being overridden by the user with net <wireless_mgr_0_SDIO_DATA_to_Zynq>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_DATA_T> is being overridden by the user with net <ps7_SDIO0_DATA_T>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_WP> is being overridden by the user with net <wireless_mgr_0_SDIO_WP>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/SDIO0_CDN> is being overridden by the user with net <wireless_mgr_0_SDIO_CDN>. This pin will not be connected as a part of interface connection <SDIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/GPIO_O> is being overridden by the user with net <ps7_GPIO_O>. This pin will not be connected as a part of interface connection <GPIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/GPIO_I> is being overridden by the user with net <wireless_mgr_0_GPIO_to_Zynq>. This pin will not be connected as a part of interface connection <GPIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </ps7/GPIO_T> is being overridden by the user with net <ps7_GPIO_T>. This pin will not be connected as a part of interface connection <GPIO_0>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/sout> is being overridden by the user with net <bluetooth_uart_sout>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/sin> is being overridden by the user with net <wireless_mgr_0_ZYNQ_UART_RX>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/rtsn> is being overridden by the user with net <bluetooth_uart_rtsn>. This pin will not be connected as a part of interface connection <UART>.

WARNING: [BD 41-1306] The connection to interface pin </bluetooth_uart/ctsn> is being overridden by the user with net <wireless_mgr_0_ZYNQ_UART_CTS>. This pin will not be connected as a part of interface connection <UART>.

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

***** Assigning peripheral addresses...

Slave segment '/axi_gpio_0/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4120_0000 [ 64K ]>.

Slave segment '/axi_gpio_1/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4121_0000 [ 64K ]>.

Slave segment '/axi_gpio_2/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4122_0000 [ 64K ]>.

Slave segment '/axi_iic_0/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4160_0000 [ 64K ]>.

Slave segment '/axi_intc_0/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x4180_0000 [ 64K ]>.

Slave segment '/bluetooth_uart/S_AXI/Reg' is being assigned into address space '/ps7/Data' at <0x43C0_0000 [ 64K ]>.

Slave segment '/xadc_wiz_0/s_axi_lite/Reg' is being assigned into address space '/ps7/Data' at <0x43C1_0000 [ 64K ]>.

***** Validating the block design...

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-1348] Reset pin /microphone_mgr_0/resetn_in (associated clock /microphone_mgr_0/clk_in) is connected to asynchronous reset source /ps7/FCLK_RESET2_N.

This may prevent design from meeting timing. Please add Processor System Reset module to create a reset that is synchronous to the associated clock source /ps7/FCLK_CLK2.

WARNING: [xilinx.com:ip:axi_intc:4.1-13] /axi_intc_0: Interrupt output connection Bus is selected, but the interrupt bus interface is not connected to a matching interface. Please consider selecting Single instead.

INFO: [xilinx.com:ip:clk_wiz:6.0-1] /clk_wiz_0 clk_wiz propagate

CRITICAL WARNING: [BD 41-759] The input pins (listed below) are either not connected or do not have a source port, and they don't have a tie-off specified. These pins are tied-off to all 0's to avoid error in Implementation flow.

Please check your design and connect them as needed:

/axi_intc_0/intr

***** Validating IP licenses...

License Validation = Successful

***** Creating top level HDL wrapper for design and adding to project...

INFO: [BD 41-1662] The design 'minized_sbc_base.bd' is already validated. Therefore parameter propagation will not be re-run.

CRITICAL WARNING: [BD 41-759] The input pins (listed below) are either not connected or do not have a source port, and they don't have a tie-off specified. These pins are tied-off to all 0's to avoid error in Implementation flow.

Please check your design and connect them as needed:

/axi_intc_0/intr

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/synth/minized_sbc_base.vhd

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/sim/minized_sbc_base.vhd

VHDL Output written to : /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd

INFO: [Project 1-1716] Could not find the wrapper file /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd, checking in project .gen location instead.

INFO: [Vivado 12-12390] Found file /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd, adding it to Project

***** Adding Vitis directves to design...

update_compile_order: Time (s): cpu = 00:00:06 ; elapsed = 00:00:08 . Memory (MB): peak = 2454.039 ; gain = 0.016 ; free physical = 3206 ; free virtual = 7716

INFO: [filemgmt 20-334] All file(s) are already imported in fileset: 'constrs_1'

INFO: [filemgmt 20-348] Importing the appropriate files for fileset: 'constrs_1'

INFO: [filemgmt 20-348] Importing the appropriate files for fileset: 'sources_1'

***** Building binary...

update_compile_order: Time (s): cpu = 00:00:05 ; elapsed = 00:00:05 . Memory (MB): peak = 2454.039 ; gain = 0.000 ; free physical = 3206 ; free virtual = 7716

update_compile_order: Time (s): cpu = 00:00:06 ; elapsed = 00:00:07 . Memory (MB): peak = 2454.039 ; gain = 0.000 ; free physical = 3205 ; free virtual = 7716

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-1348] Reset pin /microphone_mgr_0/resetn_in (associated clock /microphone_mgr_0/clk_in) is connected to asynchronous reset source /ps7/FCLK_RESET2_N.

This may prevent design from meeting timing. Please add Processor System Reset module to create a reset that is synchronous to the associated clock source /ps7/FCLK_CLK2.

WARNING: [xilinx.com:ip:axi_intc:4.1-13] /axi_intc_0: Interrupt output connection Bus is selected, but the interrupt bus interface is not connected to a matching interface. Please consider selecting Single instead.

INFO: [xilinx.com:ip:clk_wiz:6.0-1] /clk_wiz_0 clk_wiz propagate

INFO: [xilinx.com:ip:clk_wiz:6.0-1] /clk_wiz_0 clk_wiz propagate

CRITICAL WARNING: [BD 41-759] The input pins (listed below) are either not connected or do not have a source port, and they don't have a tie-off specified. These pins are tied-off to all 0's to avoid error in Implementation flow.

Please check your design and connect them as needed:

/axi_intc_0/intr

Wrote : </home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/sources_1/bd/minized_sbc_base/minized_sbc_base.bd>

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/synth/minized_sbc_base.vhd

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_from_Zynq'(4) to pin '/ps7/GPIO_O'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/ps7/GPIO_I'(16) to pin '/wireless_mgr_0/GPIO_to_Zynq'(4) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

CRITICAL WARNING: [BD 41-2383] Width mismatch when connecting input pin '/wireless_mgr_0/GPIO_dir'(4) to pin '/ps7/GPIO_T'(16) - Only lower order bits will be connected, and other input bits of this pin will be left unconnected.

VHDL Output written to : /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/sim/minized_sbc_base.vhd

VHDL Output written to : /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hdl/minized_sbc_base_wrapper.vhd

INFO: [BD 41-1029] Generation completed for the IP Integrator block wireless_mgr_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block led_mgr_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block microphone_mgr_0 .

INFO: [IP_Flow 19-5611] Unable to find an associated reset port for the interface 'M_AXI_GP0'. A default connection has been created.

INFO: [BD 41-1029] Generation completed for the IP Integrator block ps7 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block ps7_axi_periph/xbar .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_gpio_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_gpio_1 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_gpio_2 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_iic_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block bluetooth_uart .

INFO: [BD 41-1029] Generation completed for the IP Integrator block xlconcat_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block xlconstant_1 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block axi_intc_0 .

false

INFO: [IP_Flow 19-3422] Upgraded pdm_filt_fir_compiler_v7_2_i0 (FIR Compiler 7.2) from revision 8 to revision 16

false

INFO: [IP_Flow 19-3422] Upgraded pdm_filt_fir_compiler_v7_2_i1 (FIR Compiler 7.2) from revision 8 to revision 16

INFO: [BD 41-1029] Generation completed for the IP Integrator block pdm_filt_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block xadc_wiz_0 .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_100MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_142MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_166MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_200MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_41MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block proc_sys_reset_50MHz .

INFO: [BD 41-1029] Generation completed for the IP Integrator block clk_wiz_0 .

WARNING: [IP_Flow 19-4994] Overwriting existing constraint file '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_auto_pc_0/minized_sbc_base_auto_pc_0_ooc.xdc'

INFO: [BD 41-1029] Generation completed for the IP Integrator block ps7_axi_periph/s00_couplers/auto_pc .

Exporting to file /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hw_handoff/minized_sbc_base.hwh

Generated Block Design Tcl file /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/hw_handoff/minized_sbc_base_bd.tcl

Generated Hardware Definition File /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/synth/minized_sbc_base.hwdef

[Fri Jul 14 18:19:35 2023] Launched minized_sbc_base_xbar_0_synth_1, minized_sbc_base_ps7_0_synth_1, minized_sbc_base_microphone_mgr_0_0_synth_1, minized_sbc_base_led_mgr_0_0_synth_1, minized_sbc_base_wireless_mgr_0_0_synth_1, minized_sbc_base_xadc_wiz_0_0_synth_1, minized_sbc_base_pdm_filt_0_0_synth_1, minized_sbc_base_axi_gpio_0_0_synth_1, minized_sbc_base_axi_gpio_1_0_synth_1, minized_sbc_base_axi_gpio_2_0_synth_1, minized_sbc_base_axi_iic_0_0_synth_1, minized_sbc_base_axi_uart16550_0_0_synth_1, minized_sbc_base_axi_intc_0_0_synth_1, minized_sbc_base_auto_pc_0_synth_1, minized_sbc_base_proc_sys_reset_100MHz_0_synth_1, minized_sbc_base_proc_sys_reset_142MHz_0_synth_1, minized_sbc_base_proc_sys_reset_166MHz_0_synth_1, minized_sbc_base_proc_sys_reset_200MHz_0_synth_1, minized_sbc_base_proc_sys_reset_41MHz_0_synth_1, minized_sbc_base_proc_sys_reset_50MHz_0_synth_1, minized_sbc_base_clk_wiz_0_0_synth_1, synth_1...

Run output will be captured here:

minized_sbc_base_xbar_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_xbar_0_synth_1/runme.log

minized_sbc_base_ps7_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_ps7_0_synth_1/runme.log

minized_sbc_base_microphone_mgr_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_microphone_mgr_0_0_synth_1/runme.log

minized_sbc_base_led_mgr_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_led_mgr_0_0_synth_1/runme.log

minized_sbc_base_wireless_mgr_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_wireless_mgr_0_0_synth_1/runme.log

minized_sbc_base_xadc_wiz_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_xadc_wiz_0_0_synth_1/runme.log

minized_sbc_base_pdm_filt_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_pdm_filt_0_0_synth_1/runme.log

minized_sbc_base_axi_gpio_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_axi_gpio_0_0_synth_1/runme.log

minized_sbc_base_axi_gpio_1_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_axi_gpio_1_0_synth_1/runme.log

minized_sbc_base_axi_gpio_2_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_axi_gpio_2_0_synth_1/runme.log

minized_sbc_base_axi_iic_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_axi_iic_0_0_synth_1/runme.log

minized_sbc_base_axi_uart16550_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_axi_uart16550_0_0_synth_1/runme.log

minized_sbc_base_axi_intc_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_axi_intc_0_0_synth_1/runme.log

minized_sbc_base_auto_pc_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_auto_pc_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_100MHz_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_100MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_142MHz_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_142MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_166MHz_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_166MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_200MHz_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_200MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_41MHz_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_41MHz_0_synth_1/runme.log

minized_sbc_base_proc_sys_reset_50MHz_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_proc_sys_reset_50MHz_0_synth_1/runme.log

minized_sbc_base_clk_wiz_0_0_synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/minized_sbc_base_clk_wiz_0_0_synth_1/runme.log

synth_1: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/synth_1/runme.log

[Fri Jul 14 18:19:35 2023] Launched impl_1...

Run output will be captured here: /home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.runs/impl_1/runme.log

launch_runs: Time (s): cpu = 00:00:52 ; elapsed = 00:01:00 . Memory (MB): peak = 2637.051 ; gain = 183.012 ; free physical = 3009 ; free virtual = 7617

***** Wait for bitstream to be written...

[Fri Jul 14 18:19:35 2023] Waiting for impl_1 to finish...

*** Running vivado

with args -log minized_sbc_base_wrapper.vdi -applog -m64 -product Vivado -messageDb vivado.pb -mode batch -source minized_sbc_base_wrapper.tcl -notrace

****** Vivado v2021.1 (64-bit)

**** SW Build 3247384 on Thu Jun 10 19:36:07 MDT 2021

**** IP Build 3246043 on Fri Jun 11 00:30:35 MDT 2021

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

source minized_sbc_base_wrapper.tcl -notrace

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1700] Loaded user IP repository '/home/ealbertos/git/avnet/hdl/ip'.

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository '/tools/Xilinx/Vivado/2021.1/data/ip'.

add_files: Time (s): cpu = 00:00:06 ; elapsed = 00:00:07 . Memory (MB): peak = 2599.250 ; gain = 16.027 ; free physical = 5719 ; free virtual = 7315

Command: link_design -top minized_sbc_base_wrapper -part xc7z007sclg225-1

Design is defaulting to srcset: sources_1

Design is defaulting to constrset: constrs_1

INFO: [Device 21-403] Loading part xc7z007sclg225-1

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0.dcp' for cell 'minized_sbc_base_i/axi_gpio_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0.dcp' for cell 'minized_sbc_base_i/axi_gpio_1'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0.dcp' for cell 'minized_sbc_base_i/axi_gpio_2'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_iic_0_0/minized_sbc_base_axi_iic_0_0.dcp' for cell 'minized_sbc_base_i/axi_iic_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_intc_0_0/minized_sbc_base_axi_intc_0_0.dcp' for cell 'minized_sbc_base_i/axi_intc_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0.dcp' for cell 'minized_sbc_base_i/bluetooth_uart'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.dcp' for cell 'minized_sbc_base_i/clk_wiz_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_led_mgr_0_0/minized_sbc_base_led_mgr_0_0.dcp' for cell 'minized_sbc_base_i/led_mgr_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_microphone_mgr_0_0/minized_sbc_base_microphone_mgr_0_0.dcp' for cell 'minized_sbc_base_i/microphone_mgr_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/minized_sbc_base_pdm_filt_0_0.dcp' for cell 'minized_sbc_base_i/pdm_filt_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_100MHz'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_142MHz'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_166MHz'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_200MHz'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_41MHz'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0.dcp' for cell 'minized_sbc_base_i/proc_sys_reset_50MHz'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.dcp' for cell 'minized_sbc_base_i/ps7'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_wireless_mgr_0_0/minized_sbc_base_wireless_mgr_0_0.dcp' for cell 'minized_sbc_base_i/wireless_mgr_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xadc_wiz_0_0/minized_sbc_base_xadc_wiz_0_0.dcp' for cell 'minized_sbc_base_i/xadc_wiz_0'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xbar_0/minized_sbc_base_xbar_0.dcp' for cell 'minized_sbc_base_i/ps7_axi_periph/xbar'

INFO: [Project 1-454] Reading design checkpoint '/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_auto_pc_0/minized_sbc_base_auto_pc_0.dcp' for cell 'minized_sbc_base_i/ps7_axi_periph/s00_couplers/auto_pc'

Netlist sorting complete. Time (s): cpu = 00:00:00.05 ; elapsed = 00:00:00 . Memory (MB): peak = 2599.324 ; gain = 0.000 ; free physical = 5435 ; free virtual = 7031

INFO: [Netlist 29-17] Analyzing 80 Unisim elements for replacement

INFO: [Netlist 29-28] Unisim Transformation completed in 0 CPU seconds

INFO: [Project 1-479] Netlist was created with Vivado 2021.1

INFO: [Project 1-570] Preparing netlist for logic optimization

WARNING: [Opt 31-32] Removing redundant IBUF since it is not being driven by a top-level port. minized_sbc_base_i/clk_wiz_0/inst/clkin1_ibufg

Resolution: The tool has removed redundant IBUF. To resolve this warning, check for redundant IBUF in the input design.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/clk_wiz_0/clk_in1' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_dir' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_dir' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_dir' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_from_Zynq' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_from_Zynq' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_from_Zynq' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_to_Zynq' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_to_Zynq' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_CMD_to_Zynq' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[0]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[0]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[0]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[1]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[1]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[1]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[2]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[2]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[2]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[3]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[3]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_dir[3]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_from_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[0]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[1]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[2]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'SLEW' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for SLEW but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'DRIVE' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for DRIVE but preserved for implementation.

WARNING: [Constraints 18-550] Could not create 'IBUF_LOW_PWR' constraint because net 'minized_sbc_base_i/wireless_mgr_0/SDIO_DATA_to_Zynq[3]' is not directly connected to top level port. Synthesis is ignored for IBUF_LOW_PWR but preserved for implementation.

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xadc_wiz_0_0/minized_sbc_base_xadc_wiz_0_0.xdc] for cell 'minized_sbc_base_i/xadc_wiz_0/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_xadc_wiz_0_0/minized_sbc_base_xadc_wiz_0_0.xdc] for cell 'minized_sbc_base_i/xadc_wiz_0/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

INFO: [Timing 38-35] Done setting XDC timing constraints. [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc:57]

INFO: [Timing 38-2] Deriving generated clocks [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc:57]

get_clocks: Time (s): cpu = 00:00:05 ; elapsed = 00:00:07 . Memory (MB): peak = 2766.062 ; gain = 158.828 ; free physical = 4932 ; free virtual = 6543

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0_board.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_clk_wiz_0_0/minized_sbc_base_clk_wiz_0_0_board.xdc] for cell 'minized_sbc_base_i/clk_wiz_0/inst'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_50MHz_0/minized_sbc_base_proc_sys_reset_50MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_50MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_41MHz_0/minized_sbc_base_proc_sys_reset_41MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_41MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_200MHz_0/minized_sbc_base_proc_sys_reset_200MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_200MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_166MHz_0/minized_sbc_base_proc_sys_reset_166MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_166MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_142MHz_0/minized_sbc_base_proc_sys_reset_142MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_142MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_proc_sys_reset_100MHz_0/minized_sbc_base_proc_sys_reset_100MHz_0_board.xdc] for cell 'minized_sbc_base_i/proc_sys_reset_100MHz/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc] for cell 'minized_sbc_base_i/ps7/inst'

WARNING: [Vivado 12-2489] -input_jitter contains time 0.187500 which will be rounded to 0.188 to ensure it is an integer multiple of 1 picosecond [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc:21]

WARNING: [Vivado 12-2489] -input_jitter contains time 0.618750 which will be rounded to 0.619 to ensure it is an integer multiple of 1 picosecond [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc:27]

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_ps7_0/minized_sbc_base_ps7_0.xdc] for cell 'minized_sbc_base_i/ps7/inst'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/constrs/pdm_filt.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/constrs/pdm_filt.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i0/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2/pdm_filt_fir_compiler_v7_2_i0_instance/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i0/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2/pdm_filt_fir_compiler_v7_2_i0_instance/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i1/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2_1/pdm_filt_fir_compiler_v7_2_i1_instance/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_pdm_filt_0_0/pdm_filt_fir_compiler_v7_2_i1/constraints/fir_compiler_v7_2.xdc] for cell 'minized_sbc_base_i/pdm_filt_0/U0/pdm_filt_struct/fir_7_2_1/pdm_filt_fir_compiler_v7_2_i1_instance/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_intc_0_0/minized_sbc_base_axi_intc_0_0.xdc] for cell 'minized_sbc_base_i/axi_intc_0/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_intc_0_0/minized_sbc_base_axi_intc_0_0.xdc] for cell 'minized_sbc_base_i/axi_intc_0/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0_board.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_uart16550_0_0/minized_sbc_base_axi_uart16550_0_0_board.xdc] for cell 'minized_sbc_base_i/bluetooth_uart/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_iic_0_0/minized_sbc_base_axi_iic_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_iic_0/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_iic_0_0/minized_sbc_base_axi_iic_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_iic_0/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_2_0/minized_sbc_base_axi_gpio_2_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_2/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_1_0/minized_sbc_base_axi_gpio_1_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_1/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Finished Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.gen/sources_1/bd/minized_sbc_base/ip/minized_sbc_base_axi_gpio_0_0/minized_sbc_base_axi_gpio_0_0_board.xdc] for cell 'minized_sbc_base_i/axi_gpio_0/U0'

Parsing XDC File [/home/ealbertos/git/avnet/hdl/projects/minized_sbc_base_2021_1/minized_sbc_base.srcs/constrs_1/imports/base/minized_sbc_base.xdc]