Table of Contents

- Project Introduction

- Getting Started

- Calibrating the MPX2050DP Pressure Sensor

- Calculations and Noise Reduction

- Using Vivado and Testing the System

- Project Report Updated

**********************************************************************************************************************

Project Getting Started

In this chapter I am going to try my first steps with the Vivado software.

To install Vivado I followed the instructions shown in the following tutorial: Installing Vivado, Xilinx SDK, and Digilent Board Files

In my case, I installed Vivado 2019.1 (Windows 10 version), which took me 3 hours to download it and 1 hour to install it. Its necessary to register on the official Xilinx site: https://www.xilinx.com/

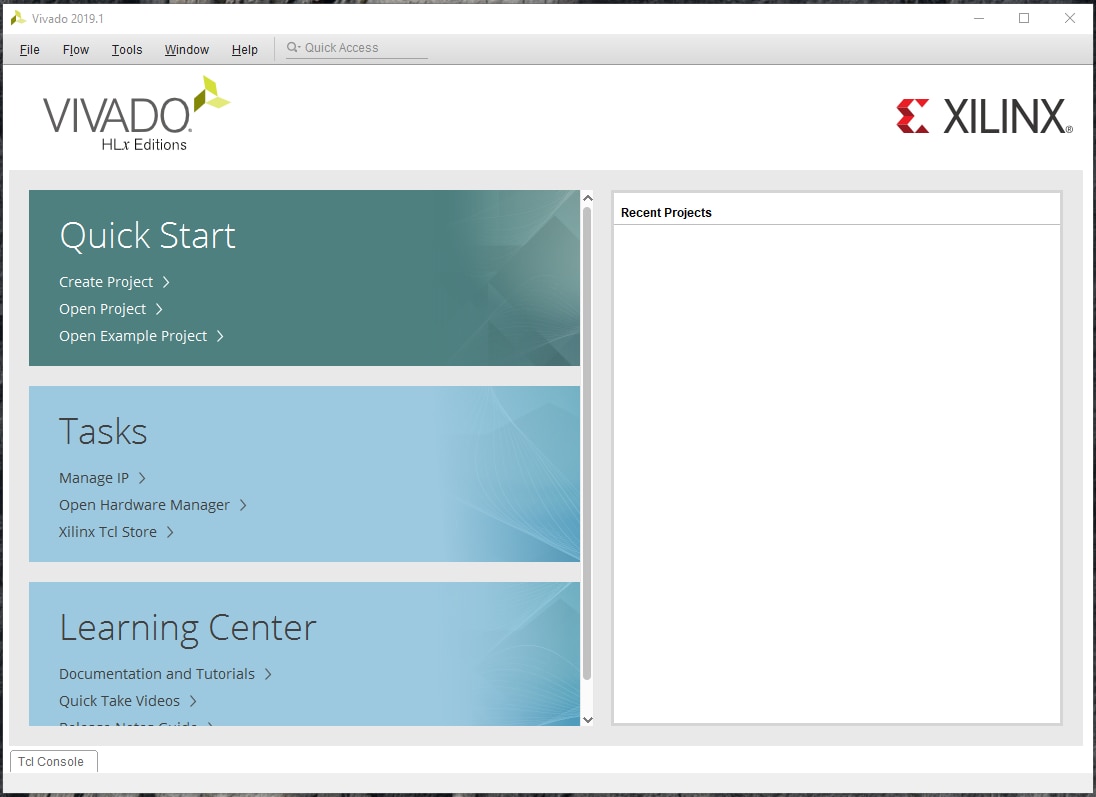

We run Vivado and see this:

Example Blinky

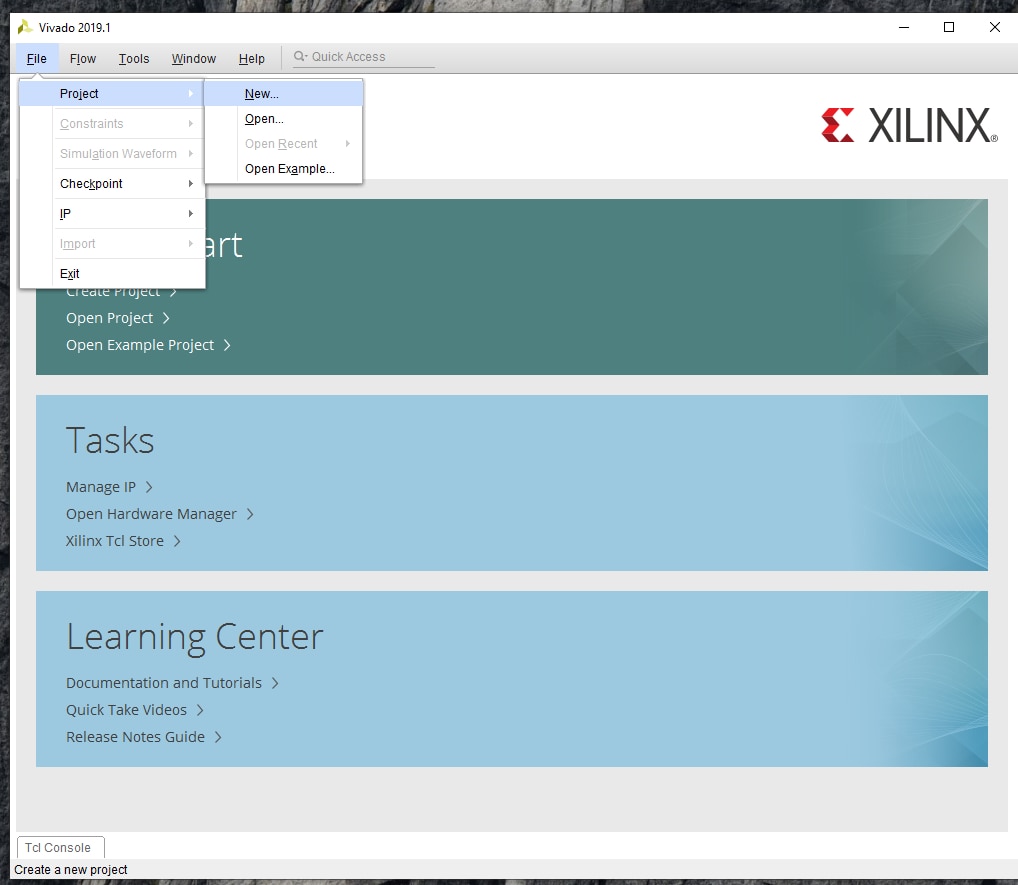

Click on File > Project > New

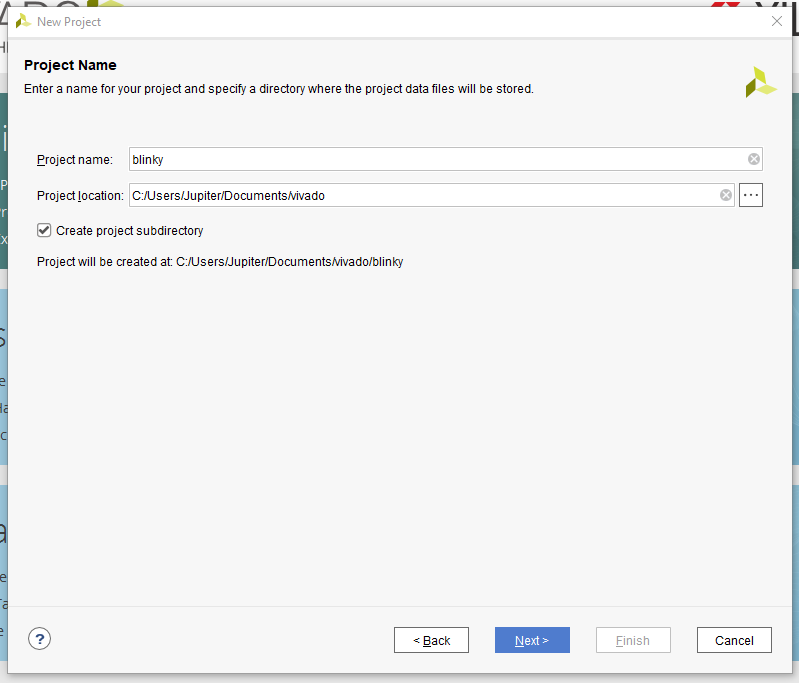

Click next to continue, Now, we set the name of the project: blinky

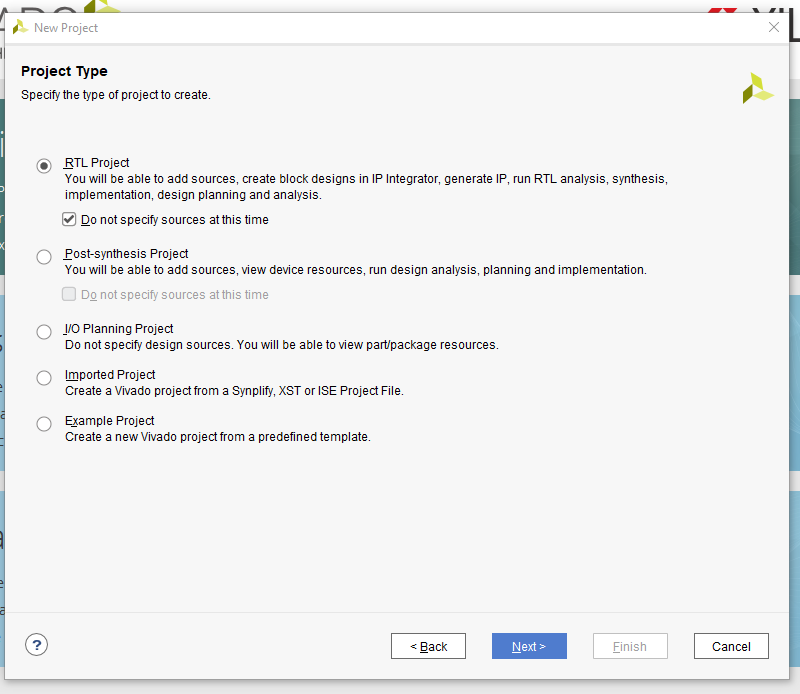

On the project type menu, select "RTL Project" and click next:

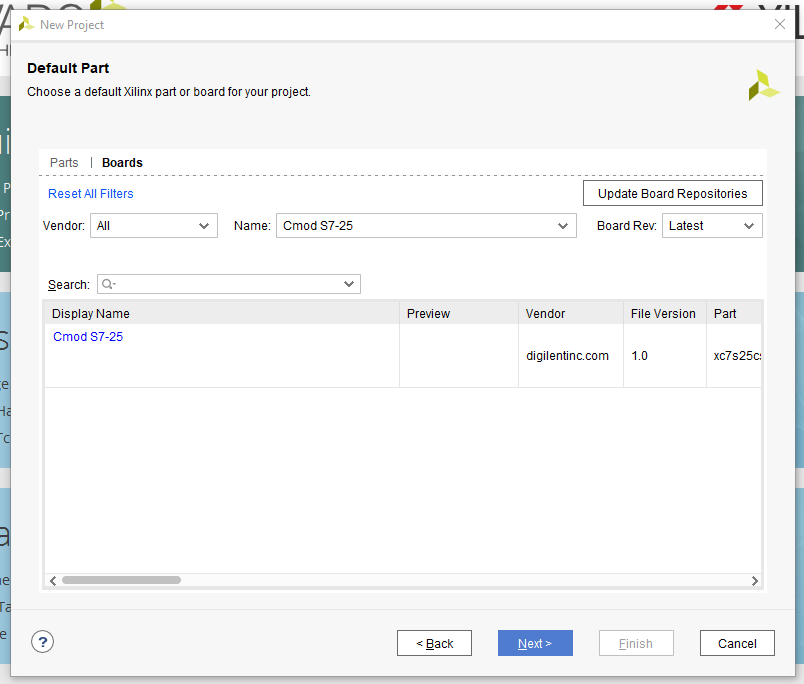

Its time to select the target device, in my case is Cmod S7-25 board. Click next to continue

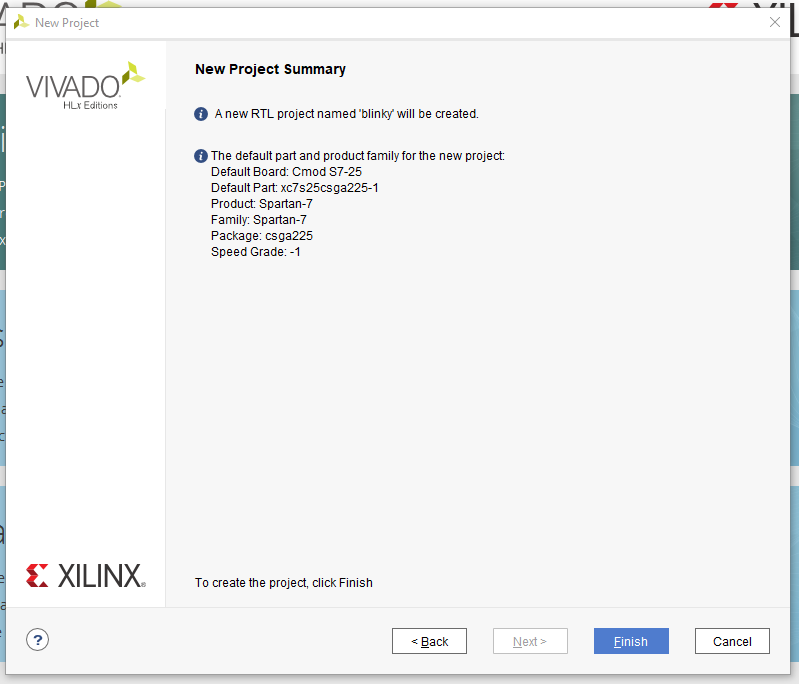

Finally we see a summary, verify and click finish.

Adding a Constraint file

Digilent has produced a Xilinx Design Constraint (XDC) file for each board. Download digilent-xdc-master.zip, then extract it in a location you will remember.

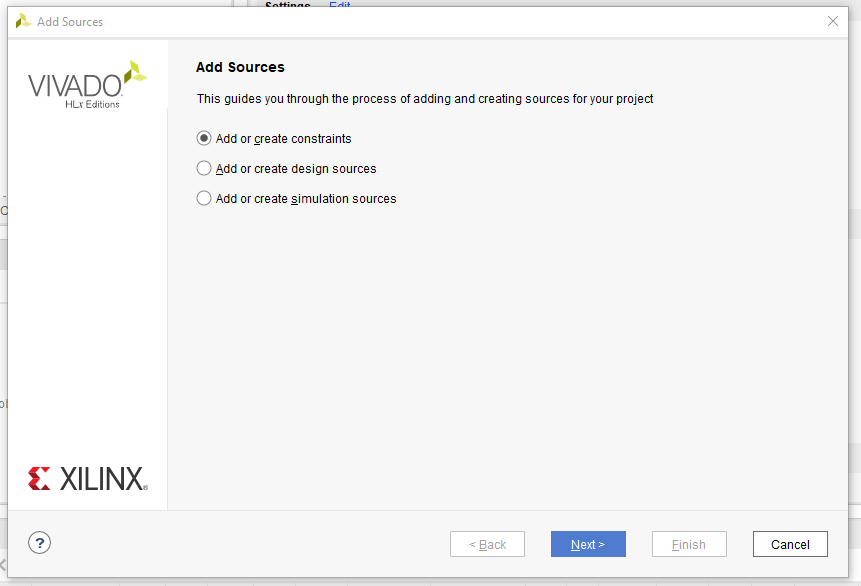

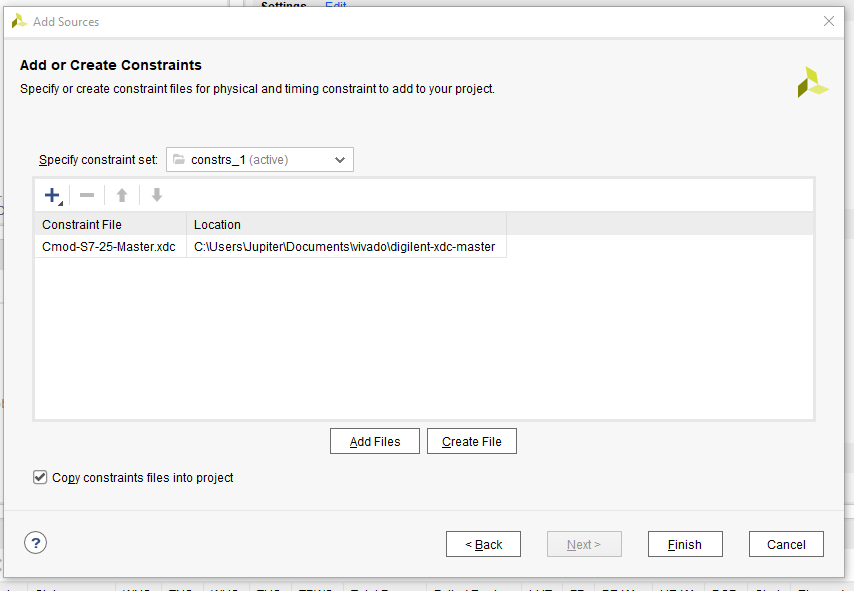

In the Project Manager section, click the Add Sources button. Select add or create constraints and click next.

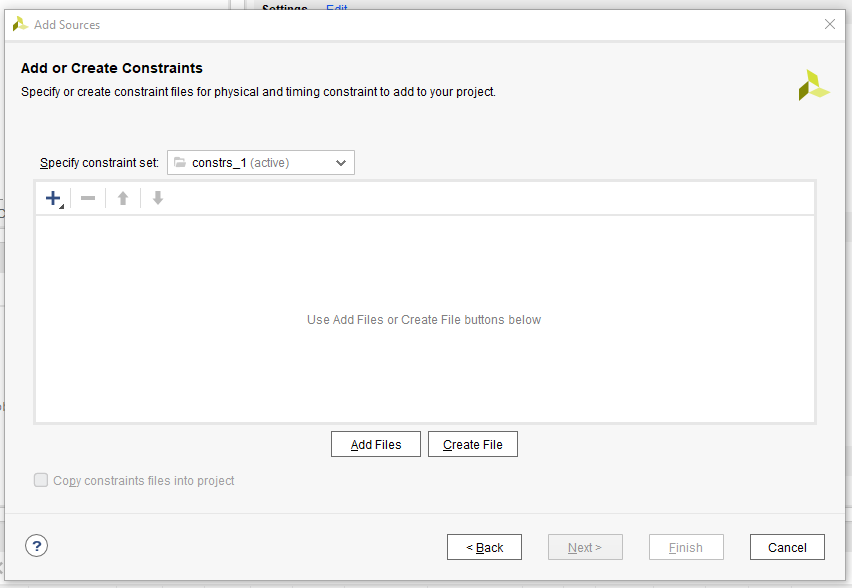

Click on Add Files:

Then click on the file for your board and click OK to continue. Once the file was added click on Finish.

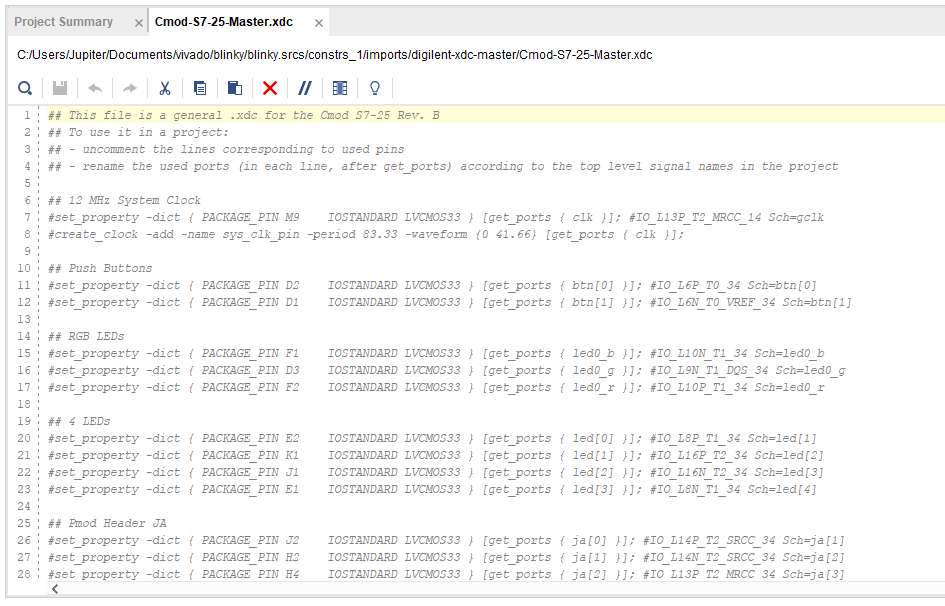

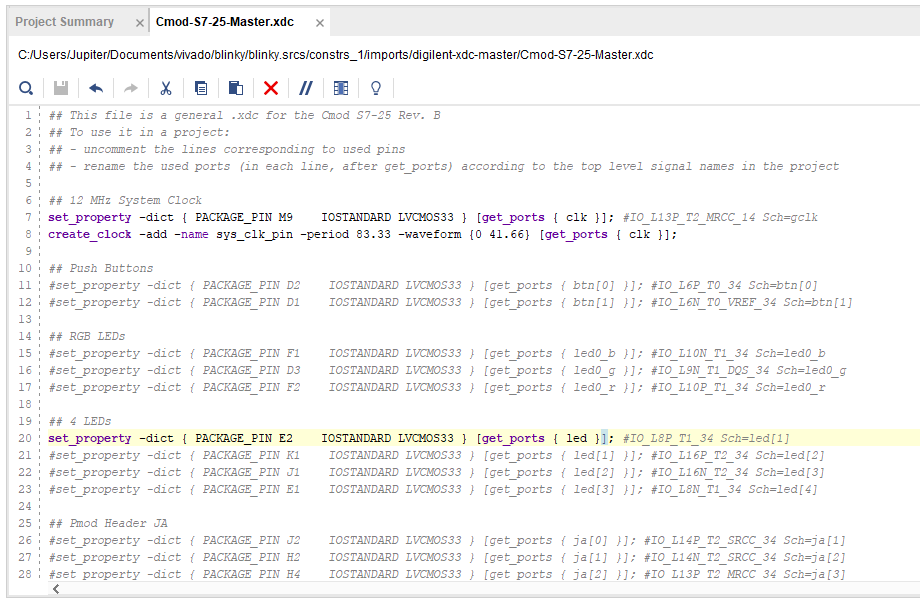

Double ckick on the you just added: Cmod-s7-25-Master.xdc

On this file, uncomment next lines ant type "led" instead "led[o]"

Creatong a Verilog source file

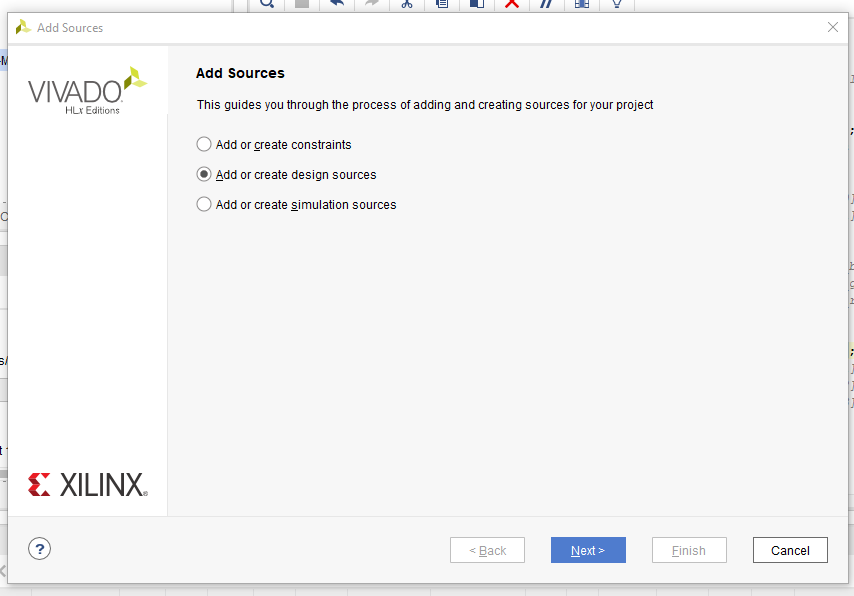

In the Project Manager section, click the Add Sources button. Select Add or create design sources and click next

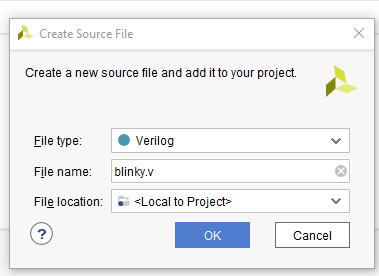

Click Create file, and type File type: verilog & File name: blinky.v

Click OK

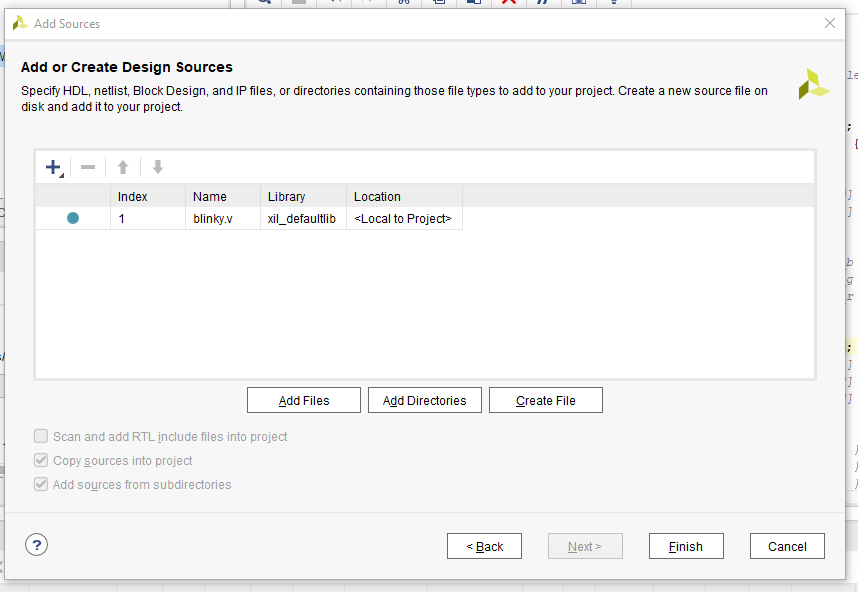

Ckeck that the new Verilog source file has been added into the list of sources, then click Finish

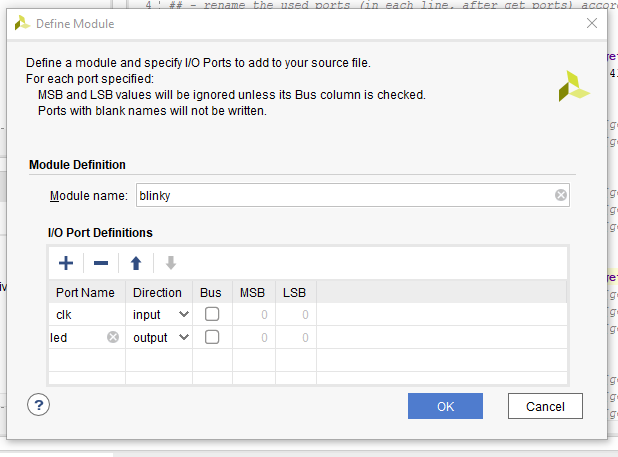

Check and and add next information on the "Define Module". Click OK

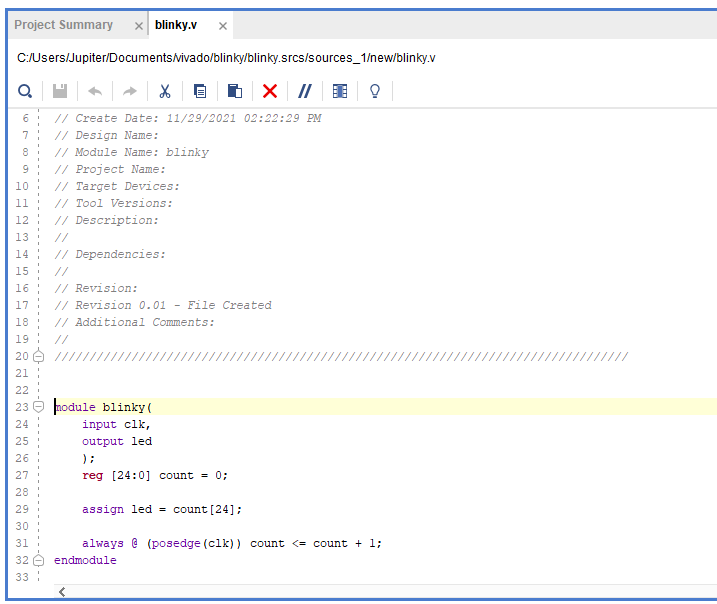

Open the new source file and add next code:

Synthesis, Implementation, and Bitstream Generation

Synthesis turns HDL files into a transistor level description based on timing and I/O constraints. To run Synthesis click in the Flow Navigator.

Implementation has several steps. The steps that are always run are Opt Design, Place Design, and Route Design. To run Implementation click in the Flow Navigator.

The Bitstream Generator generates the final outputs needed for programming the FPGA. To run Bitstream Generation click either in the Flow Navigator. With no settings changed, the generator will create a '.bit' file.

Open New Hardware Target

The Hardware Manager is used for programming the target device.

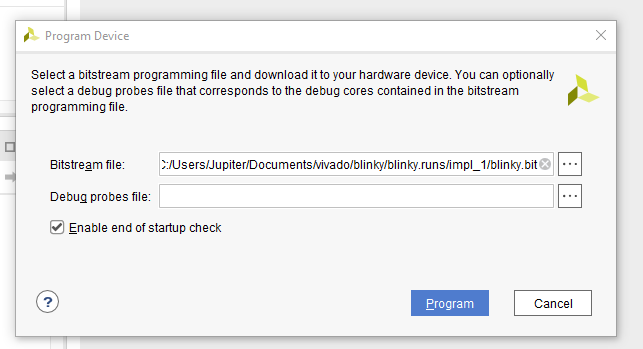

To program the device with the bit file generated earlier, either click the program device button in the ardware Manager. Select the Bitstream File field should be automatically filled in with the bit file generated earlier and select the bit file. Now click Program..

Reference: Getting Started with Vivado

Note: I have made few changes, due to the version of Vivado that I have used, but in the end everything works.