In this project we will port the PYNQ framework to the ZC702 development board.

Introduction

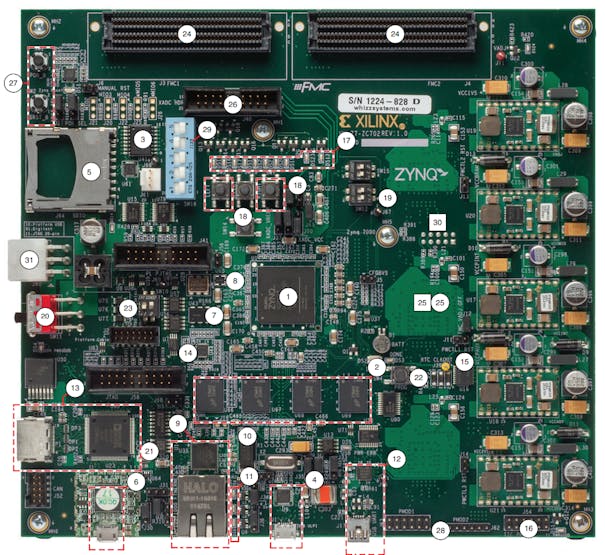

The ZC702 is an official development board from Xilinx. This board sports a ZC7020 ZYNQ FPGA SoC. It comes with a number of peripherals including HDMI, CAN Bus, UART, embedded Digilent JTAG Programmer, Ethernet , SD card, USB host , I2C bus expander and a number of SMBUS enabled PMIC for monitoring the SoC rails.

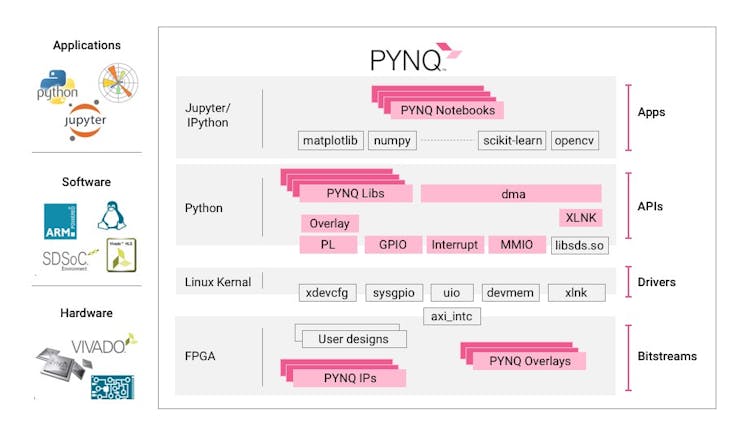

PYNQ is a project by Xilinx that brings Python level productivity to FPGA's. It allows a designer to import hardare designs called overlays in PYNQ parlance and write Python code to address and configure the cores.

This makes designs much easier compared to writing low level C code on the SDK everytime the device needs to be configured.

This speeds up development by an order of magnitude compared to bare metal designs. As of 2020 PYNQ V2.5 uses a Petalinux Kernels with a UBUNTU 28.04 Rootfs.

The ZC702 development board is not supported by the official PYNQ framework so I decided to try and port part of it to this board in order to use it for different projects.

The official way to port PYNQ to a new board is to download the framework from Git create a custom board file that uses the custo board BSP and the board parameters.

Here we are going to take a shortcut that involves reusing the official image and generate a kernel from scratch using Petalinux.

PYNQ uses a Petalinux kernel coupled with a Ubuntu rootfs.

Porting PYQN the easy way.

Download the PYNQ image 2.5 and burn it to an SD CARD. This will partition the SD card with a FATFS partition that holds the kernel and device tree and an ext4 partition that holds the rootfs which in PYNQ's case is a UBUNTU 18.0 root file system.

To boot the board on the ZC702 we have to customize the default kernel of the PYNQ V2.5 image which targets the 400 pin version of ZC7020 to the 484 pin SOC on the ZC702.

Step #1

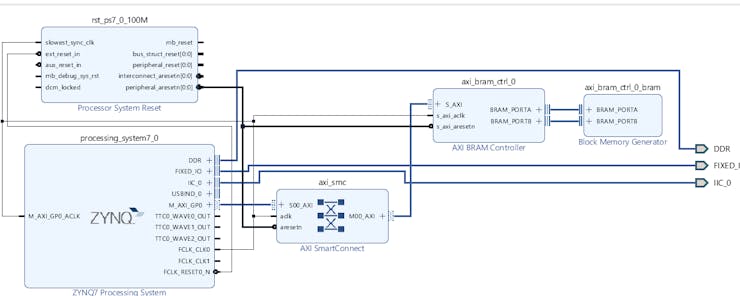

Create a basic Vivado design. I created a custom Vivado design targeting the ZC702 with a BRAM, 1 GPIO targeting the built in LEDS's and switches and an AXI IIC core deployed on the PL that shares the same I2C pins located on the FMC.

In this project we will read and write to the BRAM IP from the PS side..

Step #2

Compile the design and export it. Also create an FSBL and a hello world test app on the SDK folder. In addition create a folder called PYQN_ZC702 and export there the bistream and the .tcl file. We shall use this in the future to prove that the PYNQ framework works OK.

Step #3

Install Virtual Box, install Ubuntu 18.0 and then install Vivado 2019.1 as well as Petalinux 2019.1. Then copy the complete Vivado project folder on the Ubuntu VM.

Step #4

Make sure that both Vivado and Petalinux are in the user path. Then , from the project directory create a Petalinux project and read the exported hdf project file from the SDK folder.

Step #5

Build a custom kernel for the ZC702. Change the rootfs boot setting so that the kernel boots from the SD card. Then disable the net boot. Additionally enable common utilities such as i2cdetect.

Once all the settings are correct issue:

petalinux-build

Step#6

After the kernel is build create the custom kernel boot.img file by issuing the following

petalinux-package --boot --fsbl --fpga --u-boot

Finally use the SD card with the PYNQ image before and overwrite the boot image file as well as device tree with the new files generated from the Petalinix kernel compilation stage.

The steps above complete the process of porting PYNQ to the ZC702. Place the SD card on the ZC702 and change the position of the boot switches to all HIGH so that the SoC boots from the SD card.

Connecting the USB serial port shows that PYNQ boots correctly. You will get a login console.

Connect an Ethernet cable from a host computer to the ZC702.

You may needs to modify the uboot settings so that the uboot can read the rootfs from the second partition of the SD card.

Once PYNQ boots up we can connect from the host side. Then open a web browser and navigate to pynq:9090. This will bring the default page shown below. The default password for PYNQ is xilinx.

Now that we have booted PYNQ the next step is to test how it operates on the ZC702. Using WinSCP transfer the two files we created earlier on the PYNQ folder.

Testing PYNQ

To test the PYNQ framework a custom Vivado HW will be designed. The block diagram below shows the BRAM connected to the AXI interconnect.

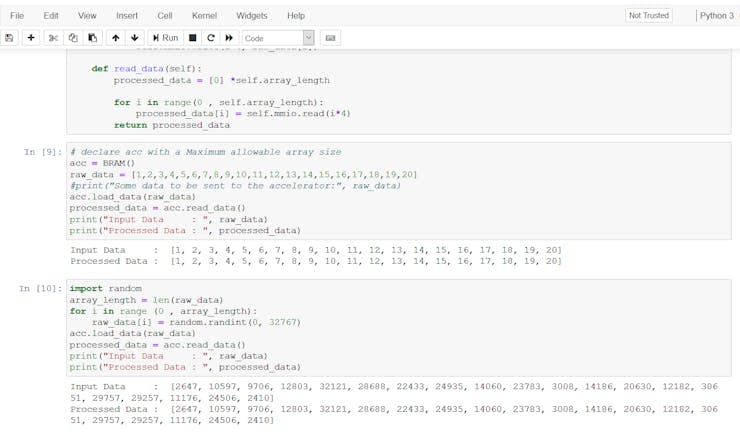

To test the PYQN framework we will build test setup with a BRAM IP an test it. First the bitstream is loaded.

The data is then printed on the Notebook.

This completes the demonstration. In this project we showed how to create a custom PYNQ distribution the easy way by avoiding the complete recompilation of the rootfs.

The framework was tested by reading and writing data to a BRAM IP block.

-

mayermakes

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

-

dimiterk

in reply to mayermakes

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Comment-

dimiterk

in reply to mayermakes

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Children