The Single Rate Half-Band FIR Decimator

A decimating filter will reduce the sample rate of a signal, while preventing aliasing. Decimation by a factor of 2x is achieved by simply throwing out every second input sample. For this to work the input data must be first filtered and the upper half of the frequency spectrum attenuated to a point where it will not affect the desired signal after decimation. The half-band FIR is ideally suited for this task. We start again with the same single rate half-band FIR prototype filter, again illustrated here for the case where the filter order is N=11:

Like we did in the previous post, we start by separating the single rate half-band prototype filter into two branches, one even and one odd:

Like we did in the previous post, we start by separating the single rate half-band prototype filter into two branches, one even and one odd:

Since we plan to drop every second output sample, we only need to consider even input samples going through the first branch and odd input samples through the second branch, which contribute to the even output samples that we will keep. There is no need to consider odd input samples through the first branch and even input samples through the second branch because these only contribute to odd output samples, which do not need to be calculated. Also, every pair of delays in both branches is replaced with a single delay:

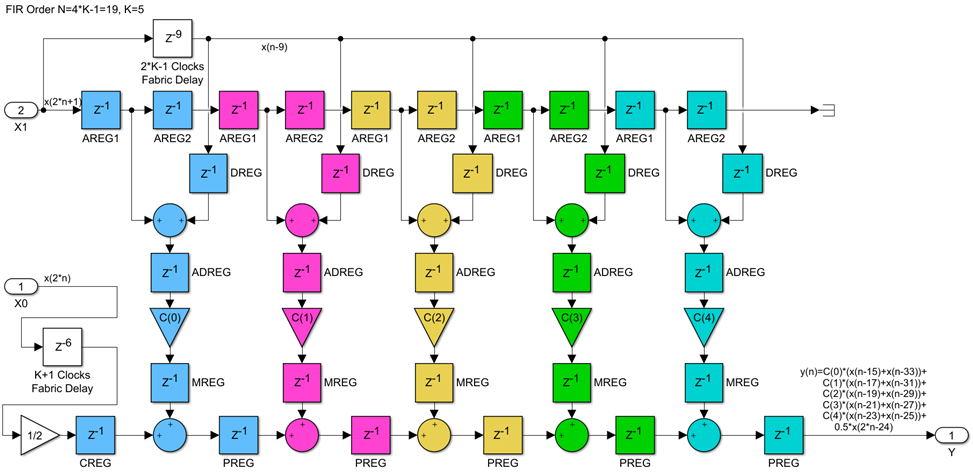

We can recognize again the same structure we have seen in the interpolator case, just connected in a slightly different way. We still have two filter branches, one a pure delay and the other one an even-symmetric single rate FIR. We already have efficient implementations for the later, so this is how a direct half-band decimator would look like for the case when N=19:

We can recognize again the same structure we have seen in the interpolator case, just connected in a slightly different way. We still have two filter branches, one a pure delay and the other one an even-symmetric single rate FIR. We already have efficient implementations for the later, so this is how a direct half-band decimator would look like for the case when N=19:

Note that there is no need for a final fabric post-adder, we achieve the same result by injecting the even input samples at the entry point of the adder chain, with a proper delay. A transposed implementation is of course also possible:

The transpose version is more efficient, with lower latency but limited scalability beyond about 20 taps. This problem can always be addressed by inserting extra pipeline registers.

Like it was the case with the half-band interpolating FIR, a half-band decimator is 8x more efficient in terms of multiplications per output sample than the direct, naïve implementation of the mathematical algorithm. We get a 2x improvement if we take advantage of the prototype filter symmetry and another 2x factor for not computing multiplications with coefficients that are zero. Finally, since we do not need to compute output samples that we will then throw away through decimation, we have another 2x efficiency factor.

Next we will go back to single rate FIRs, where the input sample rate is equal to the output sample rate, but will consider the case when this sample rate is different from the hardware clock frequency.

Back to the top: The Art of FPGA Design Season 2

Top Comments