In HDL languages, you can define generics. These are values that are assumed by default, but can be overridden. In VHDL, this may look like this:

ENTITY spi_master IS

GENERIC(

data_length : INTEGER := 16); --data length in bits

PORT(

-- ...................

tx : IN STD_LOGIC_VECTOR(data_length-1 DOWNTO 0); --data to transmit

rx : OUT STD_LOGIC_VECTOR(data_length-1 DOWNTO 0)); --data received

END spi_master;

We're looking at a reusable SPI Master IP in VHDL. The data length of a SPI interface is defaulting to 16 bits. When you drop this IP on the block design, you see:

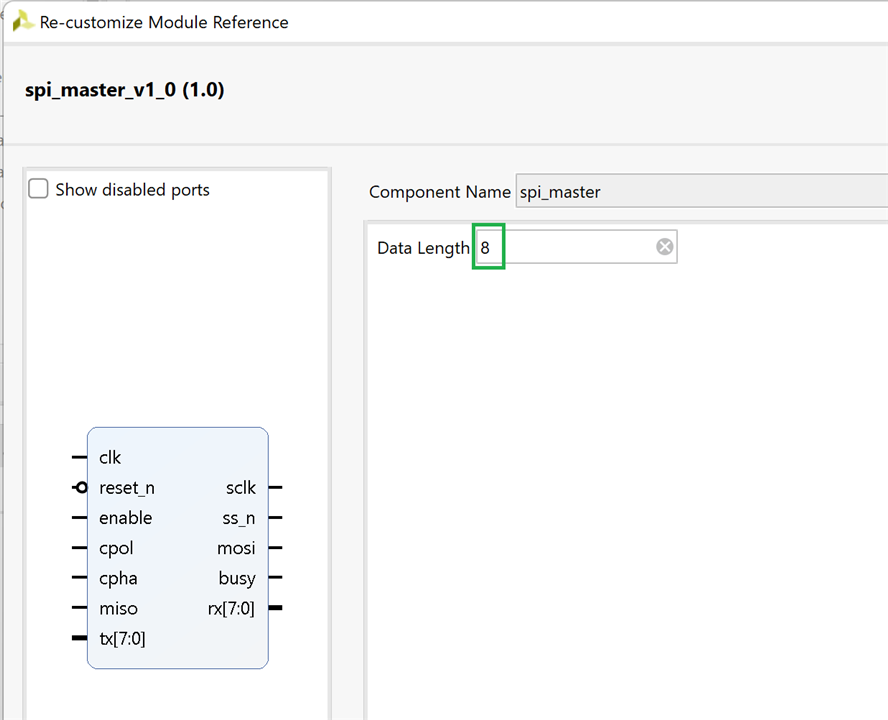

Both tx and rx have assumed the default 16 bit length. In my design, the SPI data length is 8 bits. In ISE, where there's no block design, I would override the default value in my VHDL code, when creating the SPI module. In Vivado, where you drop the module on the block diagram, you can override the value by selecting Customise Block (it initially shows 16, the default value from the IP's design):

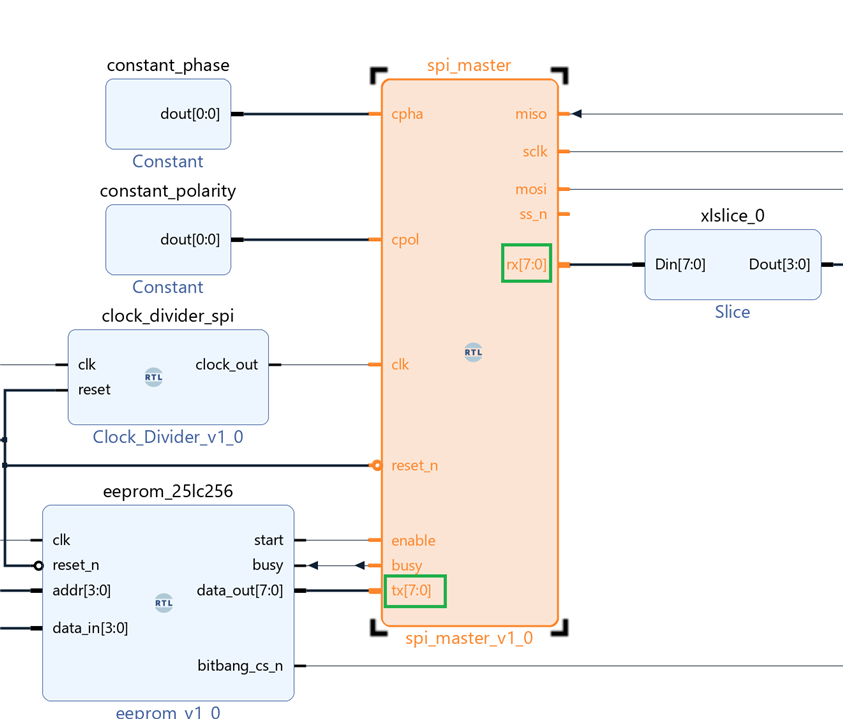

Once done, the block design (and your design) adapts to the override: