This is part 2 of the instructions to build the Arty-S7 Out-of-box experience from source. In part 1, I showed how to get the Vivado project created, and regenerate the FPGA design. That exercise delivers the full hardware design, but not the firmware to be loaded to the soft controller. In this post, we'll migrate the firmware from the 2017 SDK to Vitis.

Export Hardware and Create Vitis Platform project.

I'm not going to migrate the SDK project. I'm creating a new Vitis project, based on the Vivado design. To do that, I exported the hardware definition of the Vivado project from part 1. I included the bitfile, so that I can (re)load that to the FPGA from Vitis. In Vitis, I created a fresh workspace, and created a new Platform project based on the exported hardware definition. I chose standalone (bare metal). I built that project.

|

There's a bug in my version of Vitis, 2020.2. The make file for the PWM driver creates errors in the MicroBlaze version of the GNU archiver.. Error: mb-ar.EXE: *.o: Invalid argument |

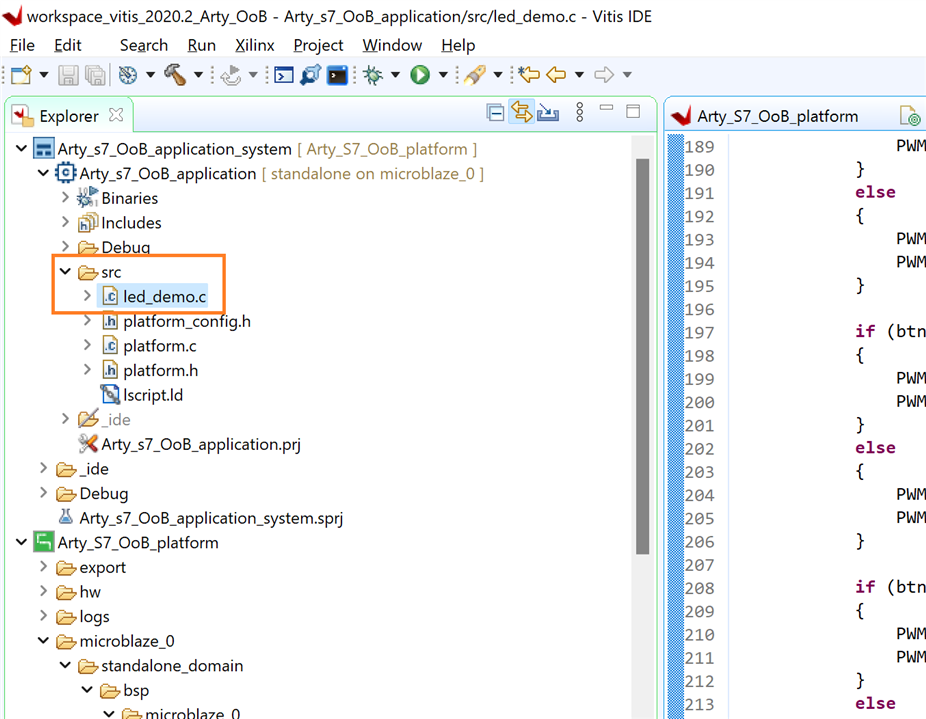

Create Application project

Then, I created an Application project for that MicroBlaze. I based it on the Vitis HelloWorld example. After checking that it compiles, I deleted helloworld.c, and copied OoB-Demo-2017.2.1-1/source/Arty-S7-50-base/sdk/oob_demo/src/led_demo.c into the project's source folder. I rebuilt the project.

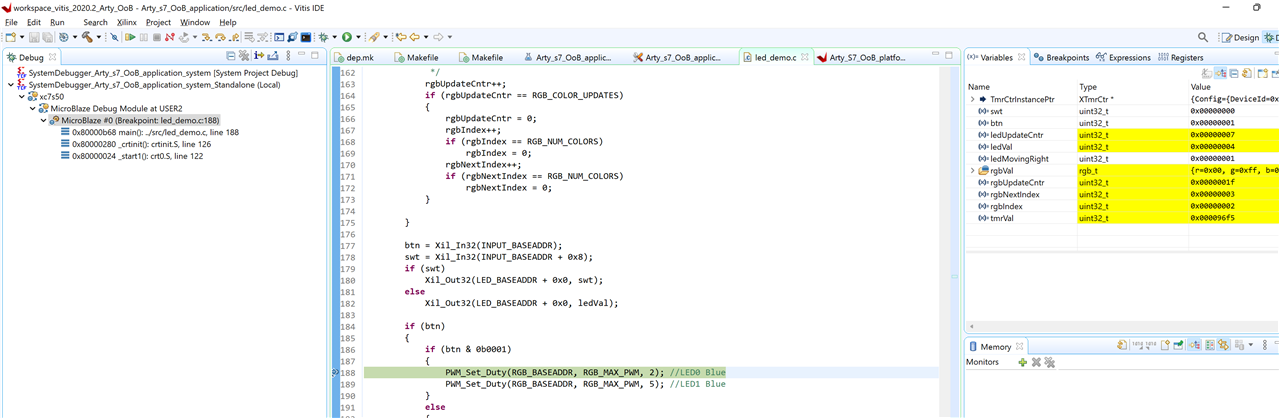

Test Firmware with Vitis Debugger

You can directly "Flash" the firmware to the microblaze from Vitis. If the Vivado bitstream is not loaded to the board yet, you can first do that from Vitis, via the Xilinx -> Program device menu option.

Then load the firmware. You can do this via Debug As -> Launch Hardware. This will load the debugger. Click start to run the firmware. You can set breakpoints, to verify if it's really your code that's running:

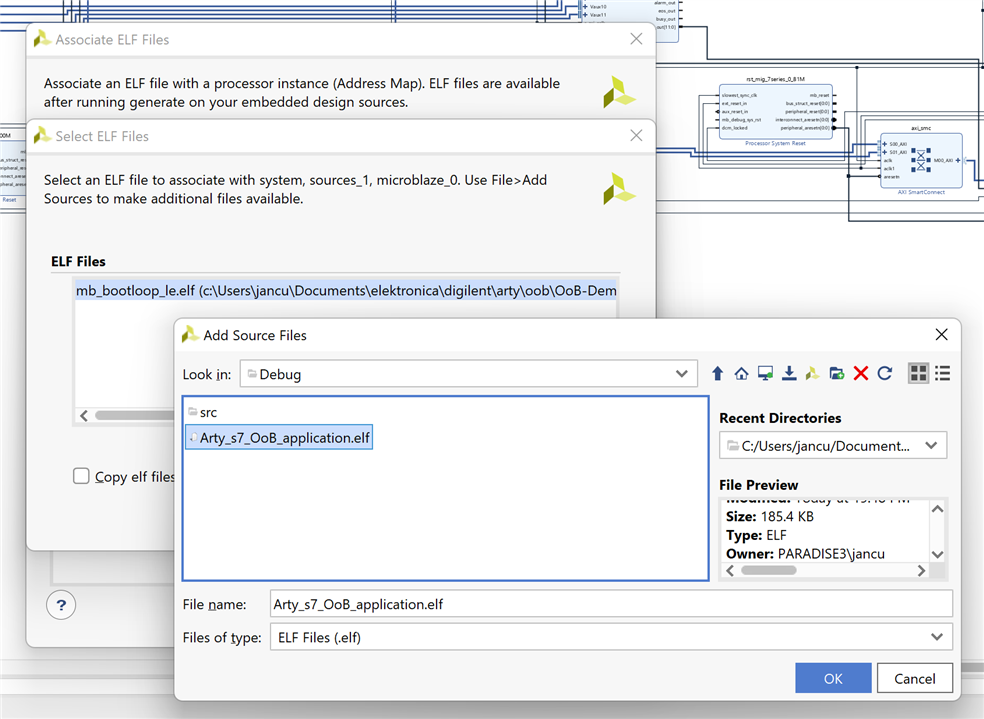

Associate Firmware with Microblaze

The last step is done in Vivado. We tell the MicroBlaze that it has to load the firmware we just generated.

Go to the block diagram, and right-click on the MicroBlaze block. Then select Associate ELF files...

Regenerate bitstream and load the OoB design including firmware

In Vivado, you can now regenerate the bitstream and send it to the FPGA via the hardware manager. If you want to load it to Flash again, check javagoza's instructions: How to Store MicroBlaze Program in the Quad-SPI Flash from Vivado.

-

javagoza

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

-

Jan Cumps

in reply to javagoza

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

-

javagoza

in reply to Jan Cumps

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Comment-

javagoza

in reply to Jan Cumps

-

Cancel

-

Vote Up

0

Vote Down

-

-

Sign in to reply

-

More

-

Cancel

Children