This blog would let the newbies learn about Spartan FPGAs, the boards available in the market, and their differences. Now let's get this straight. In reading the resource guide, the challenges and mitigation strategies that can be implemented when migrating from a Xilinx Spartan-6 FPGA to a Xilinx 7 series were given in detail.

Let's start with the history first.

- Year 2009 -> Spartan-6 Family

- Introduced in the year 2010 -> 7 Series set of 5 families (Virtex®-7, Kintex®-7, Artix®-7, Zynq®-7000, and Spartan®-7)

Spartan-6 - Highest I/O per Logic Cell

The Spartan-6 family is made of:

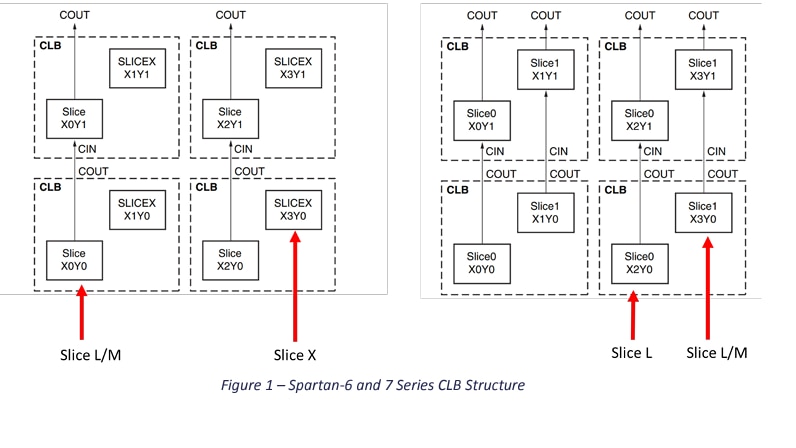

- CLBs (configurable logic blocks) with :

- SLICEs now come in three types: SLICEX, SLICEL, and SLICEM; SLICEX is a bare-bones version of SLICEL (wide LUT multiplexers and carry chain have been removed, only LUTs and flip-flops remain)

- every CLB contains two SLICEs: either one SLICEX + one SLICEL, or one SLICEX + one SLICEM; around 50% of the CLBs contain a SLICEM

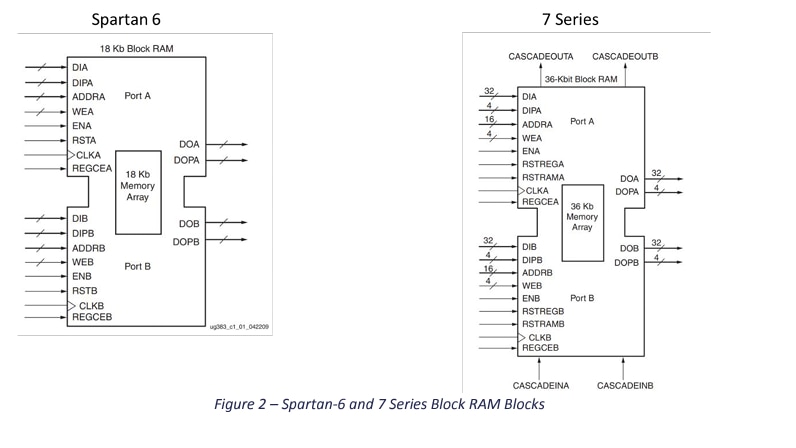

- 18kbit true dual-port block RAMs, with :

- the full 18kbit block RAM can be split into two 9kbit halves, with available configurations of 8192×1, 4096×2, 2048×4, 1024×9, 512×18

- in split mode, the half-block RAMs additionally support a simple dual-port mode in 256×36 configuration

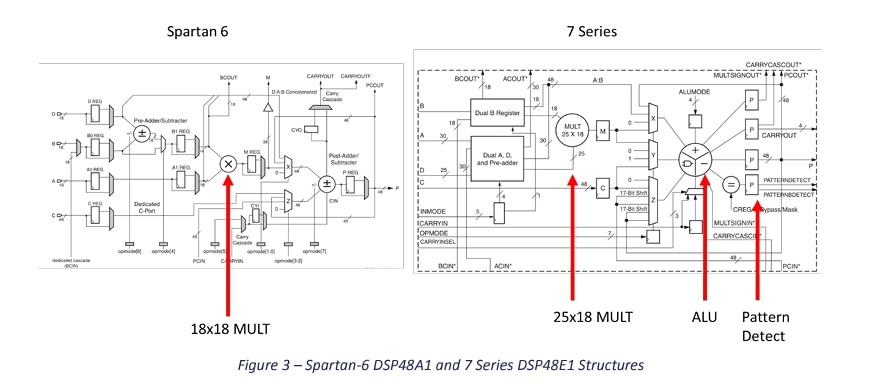

- DSP48A1 blocks

- IOBs (I/O blocks, one per user pin):

- there is no DCI support, but the user can select an uncalibrated I/O impedance from several settings

- Virtex-6-like ISERDES and OSERDES blocks are present with associated fast I/O block buffers

- the I/O bank arrangement is similar to Spartan-3A devices, but with a minor change: small devices have 4 banks (one for each device edge), while large devices have 6 banks (with the left and right edges split into two banks

- MCBs (memory controller blocks) hard memory controllers supporting DDR, DDR2, DDR3, and LPDDR memory

- CMTs (clock management tiles), each of which has:

- two DCMs, similar to Spartan-3A DCMs, but with a new clock generator mode and dynamic reconfiguration capabilities

- one PLL, similar to Virtex-5 PLLs

- 16 global clock buffers

- multiple clock regions, with 16 regional clock buffers each, which can replace the corresponding global clock buffer output for that region

- Miscellaneous configuration logic: like Spartan-3A, plus circuitry performing live configuration memory scanning with CRC error detection (but no correction)

- (SXT devices only) GTP multi-gigabit transceivers with speed ranges of 614 Mb/s to 810 Mb/s, 1.22 Gb/s to 1.62 Gb/s, and 2.45 Gb/s to 3.125 Gb/s, 8b/10b encoder and decoder, and parallel width of 8, 16, or 32 bits (10, 20, or 40 bits in 8b/10b bypass mode)

- (SXT devices only) embedded PCI Express cores capable of Gen1.1 ×1 operation

7 Series: Spartan 7 (I/O Optimization with the Highest Performance-Per-Watt)

The 7 series devices are made of:

- CLBs (configurable logic blocks)

- 36kbit splittable true dual-port block RAM

- DSP48E1 blocks

- IOBs (I/O blocks, one per user pin)

- the IOBs now come in two kinds

- HR (high range) I/O, which once again supports I/O voltage up to 3.3V, but has no DCI support

- HP (high performance) I/O, which supports I/O voltage up to 1.8V, with DCI support

- the I/O banks now have 50 I/O pins each, as follows:

- 24 differential I/O pairs split into 4 "byte groups" of 6 I/O pairs (or 12 I/O pins)

- 2 single I/O pins without differential pair

- the CMTs (clock management tiles) are now tightly coupled with I/O banks: there is one CMT for every I/O bank, and it contains:

- one MMCM,

- one PLL,

- four input and four output asynchronous FIFOs, designed for memory controller usage, but available for any application

- undocumented phaser circuitry used only by the Xilinx memory controller IPs

- the IOBs now come in two kinds

- global clock buffers (usually 32 of them, but some devices have only 16, and 3D devices have 32 for every die)

- multiple clock regions, with 4 regional clock buffers per region

- (not on the smallest Spartan devices) a single XADC analog-to-digital converter, which is an improved and renamed version of the Virtex-6 system monitor

- Miscellaneous configuration logic: like Virtex-6

- Depending on the exact device family, devices may also contain some special blocks: GTP multi-gigabit transceivers with a speed range of 500 Mb/s to 6.6 Gb/s and parallel width of 8 or 16 bits.

Comparision of Spartan-6 & Spartan-7 series

While Slice_M and Slice_L are identical between the Spartan-6 and 7 series devices, Spartan-6 devices also have a Slice_X. Slice_X is the most basic logical structure of the three slice configurations. Functions that were implemented using a Slice_X can be easily accommodated within Slice_L, which are available within the 7 series. Of course, retargeting of Slice_X to Slice_L is automatic in synthesis. As Slice_X provides only the most basic logic functionality, migration to Slice_L in 7 series devices can result in performance improvement.

Block RAM: Spartan-6 block RAMs are arranged as 18Kb blocks which can be configured as two 9Kb memories. In comparison, 7 series devices provide 36Kb blocks which can be configured as two 18Kb memories.

DSP: In the Spartan-6, the developer is provided with a DSP48A1 which provides 18x18 signed multiplication while 7 series devices play DSP48E1 which implements a 25x18 signed multiply. Architecturally, the DSP48E1 provided in 7 series devices also enables the implementation of an Algorithmic Logic Unit (ALU) and enables support of Single Instruction Multiple Data (SIMD) mode which allows increased throughput.

Clock – The clocking architecture of 7 series devices is significantly simpler than that previously provided in the Spartan-6 devices

Memory Interface - The Spartan-6 implementation uses an integrated memory block whereas 7 series devices use a Soft IP core to implement the memory controller where only the memory 6 PHY is hardened. This provides 7 series devices with a more flexible approach to I/O allocation and design which can be critical when working with complex PCB designs. 7 series Memory Interface Controller can support DDR3, DDR3L, DDR2, and LPDDR2 providing maximum flexibility in selecting the memory.

Transceivers and PCIe – Spartan-6 LXT devices provide the developer with multi-gigabit transceivers in the GTP at a maximum speed of 3.2 Gb/s. 7 series devices that support transceivers can support higher data rates or up to 6/25 Gb/s. 7 series GTPs provide a quad implementation per tile compared to the dual-tile GTP in Spartan-6 architecture. The GTP clock has also evolved in 7 series devices, enabling TX and RX to be independently clocked from any PLL. This is different than in the Spartan-6 GTP dual tile where the TX and RX must use the same clock. 7 series GTPs also provide new capabilities such as Continuous Time Linear Equalization (CTLE) with auto adaptation and post-equalization eye scan. When it comes to implementing PCIe, 7 series devices support both PCIe Gen 1 and Gen 2 in the Artix-7 range. This allows the user to benefit from greater performance as bandwidth is significantly increased if desired.

Well, that was a lot of technical specifications about the Spartan-6 devices and the 7 Series families. Quick summary of the Spartan-6 & Spartan-7 families.

| Title | Spartan-6 | Spartan-7 |

| Programmable System Integration | High pin-count to the logic ratio for I/O connectivity | |

| MicroBlaze processor soft IP | Over 40 I/O standards for simplified system design | |

| Integrated security and monitoring | PCI Express® with integrated endpoint block | |

| Increased System Performance | 30% faster performance than 45nm generation devices | Up to 8 low power 3.2Gb/s serial transceivers |

| Up to 1.25Gb/s LVDS | 800Mb/s DDR3 with integrated memory controller | |

| 25.6Gb/s peak DDR3-800 memory bandwidth with flexible, soft memory controller | ||

| BOM Cost Reduction | Cost-optimized for system I/O expansion | |

| XADC and SYSMON for integrating discrete analog and monitoring circuitry | MicroBlaze processor soft IP to eliminate external processor or MCU components | |

| Total Power Reduction | 1.0V core voltage or 0.95V core voltage option | 1.2V core voltage or 1.0V core voltage option |

| 50% lower total power than 45nm generation devices | Zero power with hibernate power-down mode | |

| Accelerated Design Productivity | Enabled by Vivado® HLx Design Suite WebPack | Enabled by ISE® Design Suite—a no-cost, front-to-back |

| Correct-by-construction block-level design with Vivado IP Integrator | The FPGA design solution for Linux and Windows | |

| Scalable optimized architecture, comprehensive tools, and IP reuse | Fast design closure using integrated wizards | |

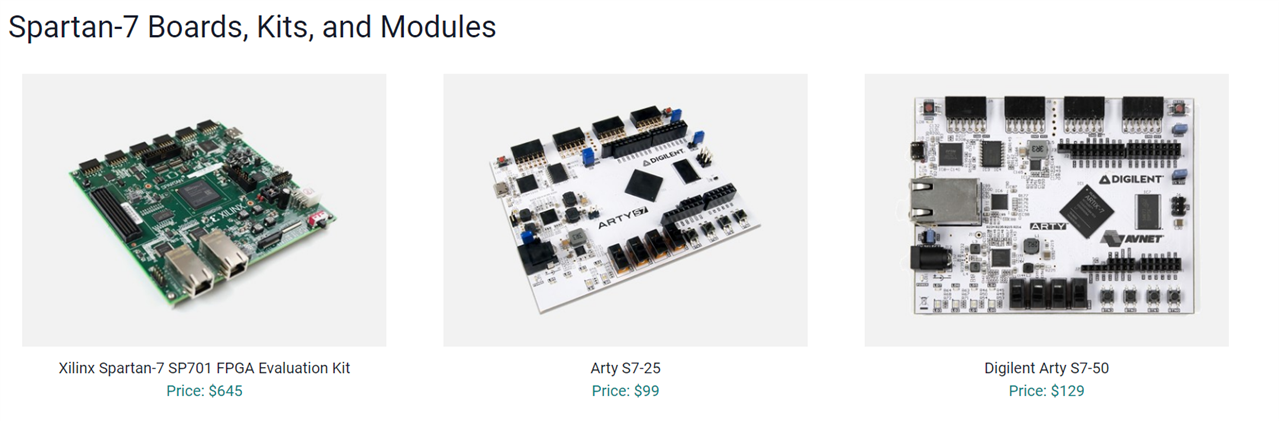

List of Spartan-7 boards and modules available in the market:

- Spartan-7 SP701 FPGA Evaluation Kit - $774.00

- ALINX AX7050: Spartan-7 XC7S50 FPGA Development board

- ALINX SoM AC7050: Spartan-7 XC7S50 Industrial Grade Module - $199.00

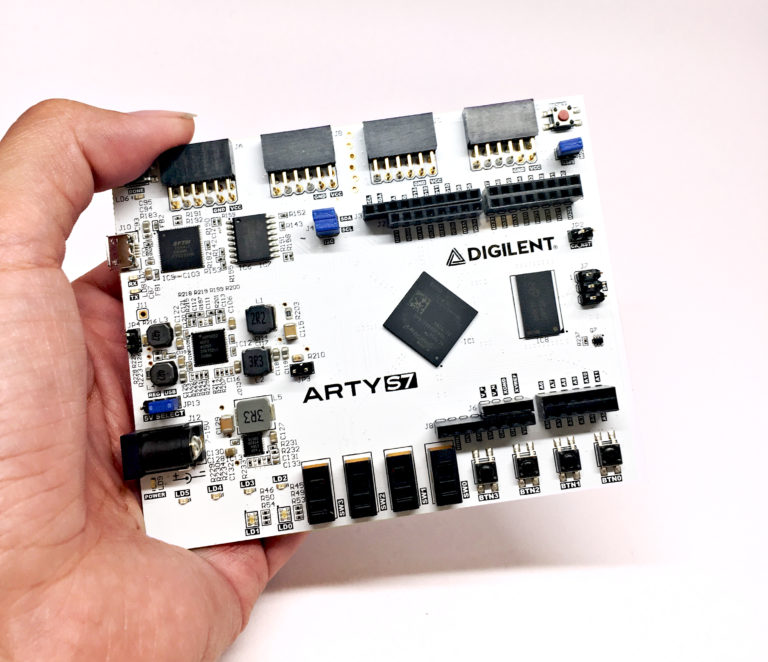

- Arty S7-25: Spartan-7 FPGA for Makers and Hobbyists - $99.00

- Arty S7-50: Spartan-7 FPGA for Makers and Hobbyists - $129.00

- Cmod S7: Breadboardable Spartan-7 FPGA Module - $69.00

- S7 Mini - $45.00

- XEM7305 - $300.00

Say hello to the Arty S7- Spartan-7 FPGA Dev Board. We will be using this on the upcoming blog. Suggest me project in the comment, that you want me to experiment with

.

You can visit these sites to know more about the Spartan families and other boards from Xilinx.

- https://www.xilinx.com/products/silicon-devices/fpga/spartan-7.html#productAdvantages

- https://www.xilinx.com/products/silicon-devices/fpga/spartan-6.html#productAdvantages

- https://www.xilinx.com/content/dam/xilinx/support/documents/sw_manuals/xilinx2017_2/ug911-vivado-migration.pdf

- https://www.xilinx.com/products/design-tools/vivado.html#video

Top Comments