This is a supporting post for Part 2: Add the Accelerated IP to a Vivado design.

I'm untangling the different data streams.

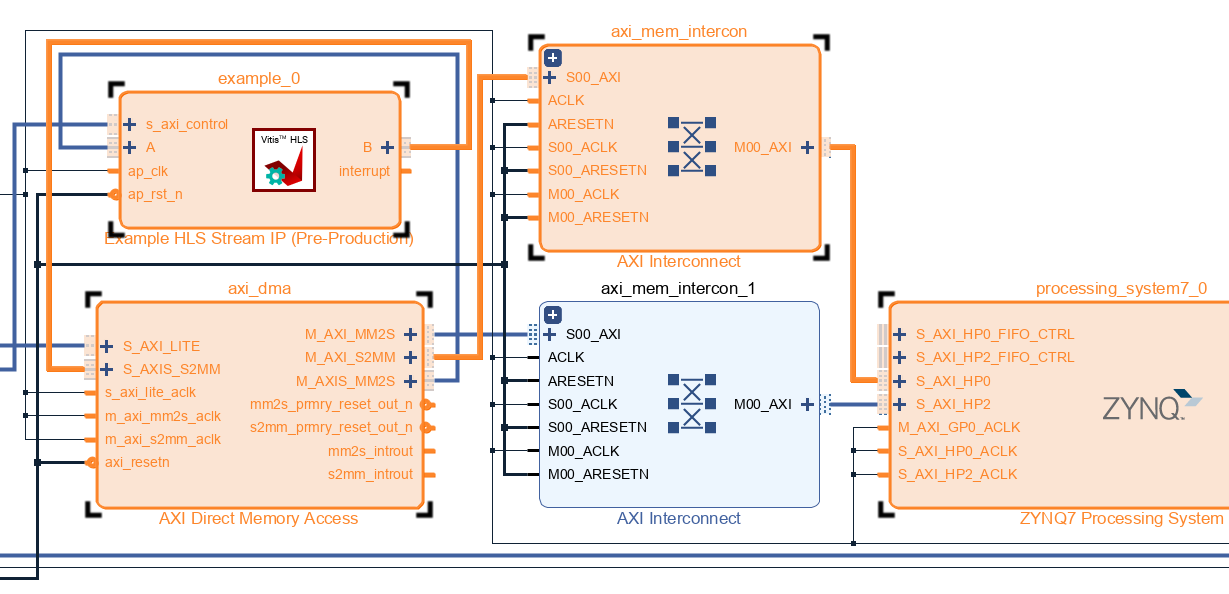

There are 3 types of data exchanged between the FPGA and ARM parts of the Zynq:

- "Business Data": the inputs and outputs to the hardware accelerated logic function. Focus on speed and throughput.

- "Control Data": the signals used to interact, enable, control, configure the exchange of that business data.

- "Other signals": reset, clock. I will not discuss those in this post.

Control Data

The DMA and Accelerated IP blocks use normal speed, AXI Lite, signals to interact with the ARM.

These blocks, signals and busses handle anything that is not related to the fast input/output.

They are supported by a dedicated AXI Interconnect block.

All blocks implement the AXI protocol and know how to work together. For the designer, the only task is to put them on the block design and configure them.

In our case, this AXI Interconnect needs two master channels, because it 'll control both DMA IP and Accelerator IP.

Business Data

The input and output data streams have to be as efficient as possible. They use the High Performance AXI channels of the ARM/ZYNQ. And DMA.

The AXI DMA block will be the in-between for bi-directional traffix between ARM DRAM and Accelerator IP.

I can show the flows in two ways. DMA-IP and DMA-ARM, or Input and Output. Im going for the lather.

When you look at each of the flows below, you'll see that there's a linear flow both times.

From DRAM to Accelerated IP

This is the input flow to the accelerated function. Data flows from DRAM to the IP block.

The AXI DMA block is the orchestrator, It will use a AXI Interconnect to retrieve a memory block from DRAM, and stream it to the Accelerator IP.

This becomes the input data for the logic implemented inside that IP.

What happens is: data will stream from the ARM's high performance channel S_AXI_HP2 to the IP, with the two AXI blocks managing that flow.

From Accelerated IP to DRAM

This is the other way round. The data that's been transformed inside the Accelerator IP (output data) is streamed to the ARM's DRAM.

The AXI DMA again manages the fast flow. Data streams from the IP to the ARM's high performance channel S_AXI_HP0.