I'm following the 3-part using a HLS stream IP with DMA training on the PYNQ community. This blog will not repeat the steps. The goal is to document the experience.

Register the IP and Use it in Vivado

In part 1, we made the hardware accelerated function example(stream &in, stream &out). Our next step is to build a Vivado hardware design.

It will include this accelerated IP, and the FPGA blocks before and after it to interface between the ARM controllers and the IP via AXI, memory maps and DMA.

If you follow the tutorial step by step, it's not hard.

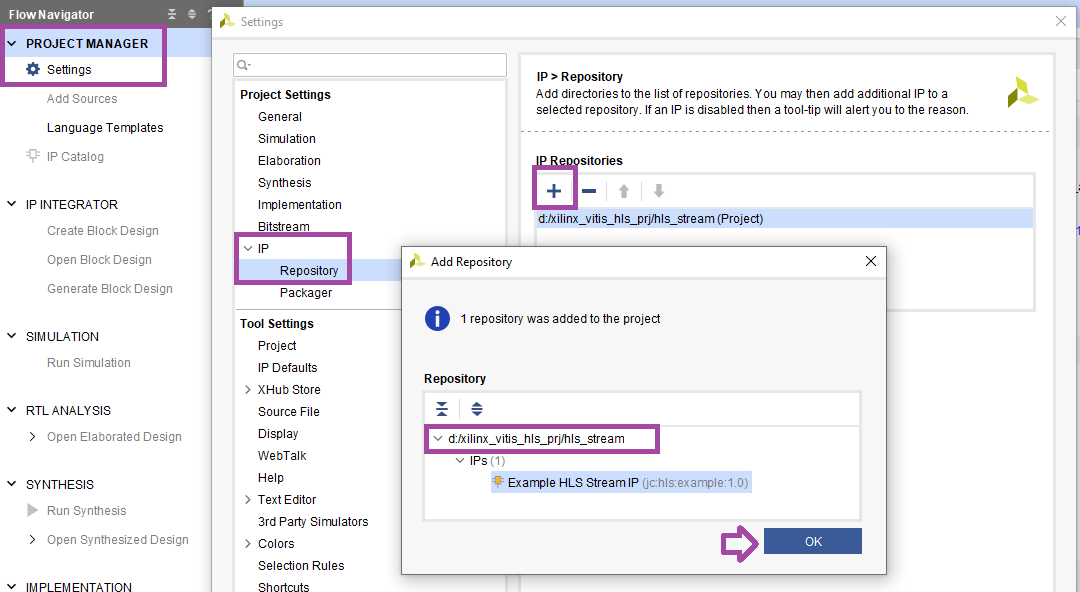

image: add the accelerator example IP to the project's IP repository

Once you create the project, you can register the IP. You can then add it to your block design.

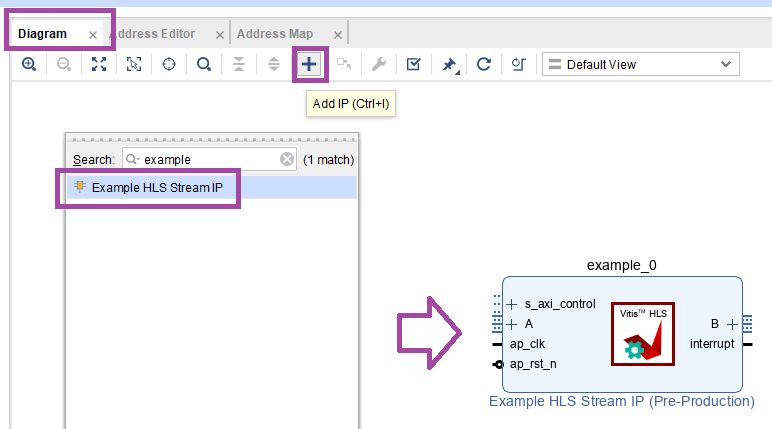

image: add the IP to your block design

The remainder of the exercise is to add the ARM block, reset, interrupt handler, DMA harness.

Most of these have been reviewed in the blog series. I'll show the DMA part.

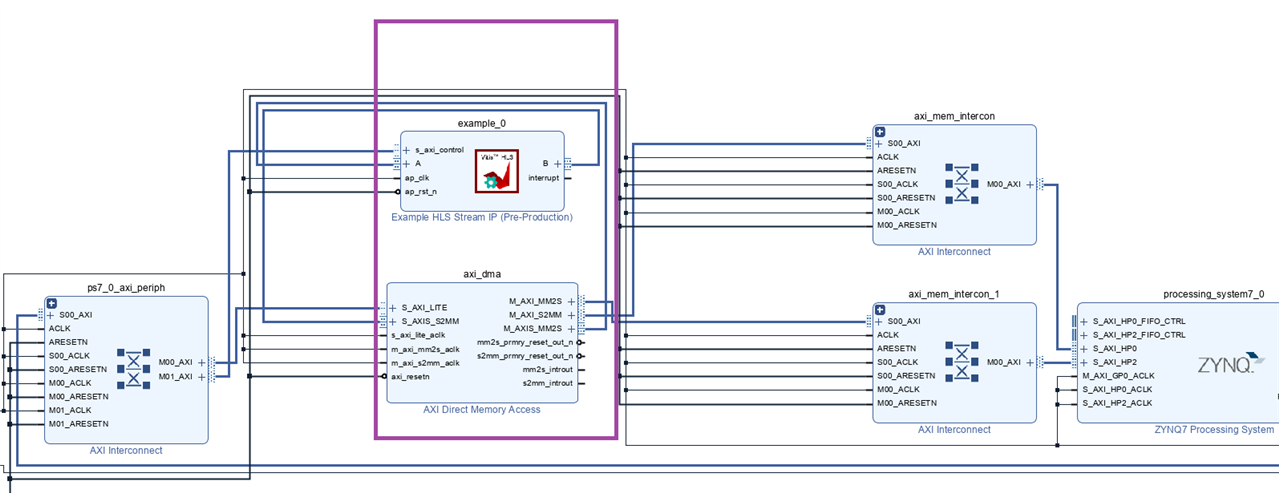

image: block design with the accelerator IP surrounded by DMA and memory map blocks

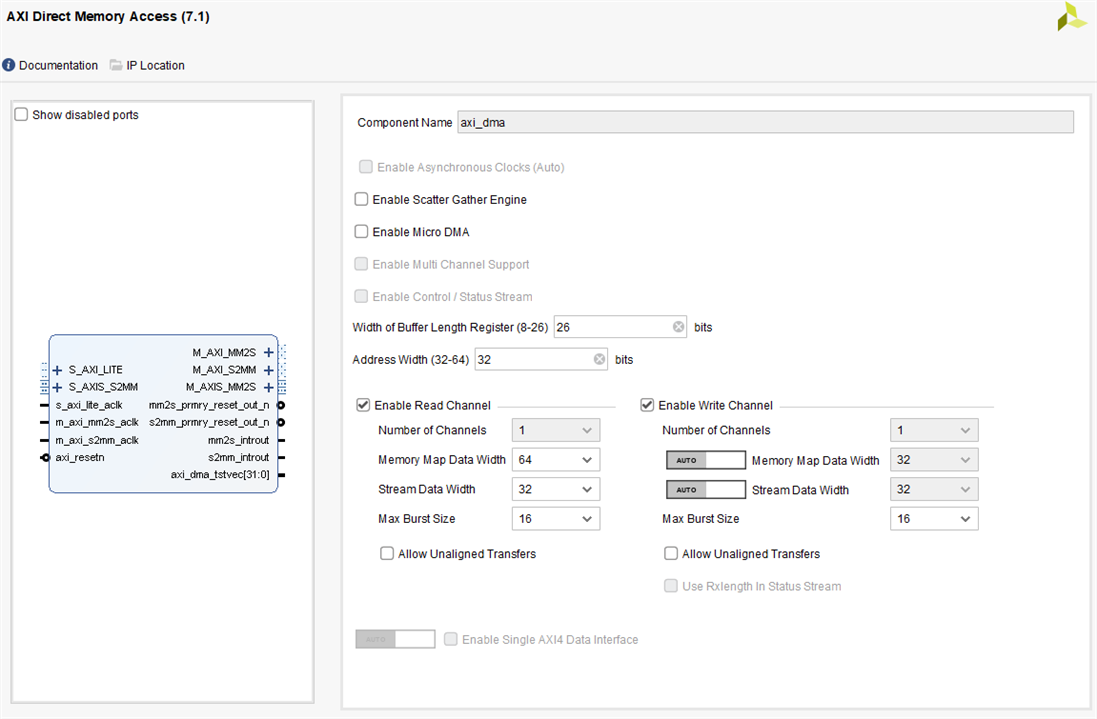

The DMA data width to and from the IP is set to 32 bits.

image: DMA settings

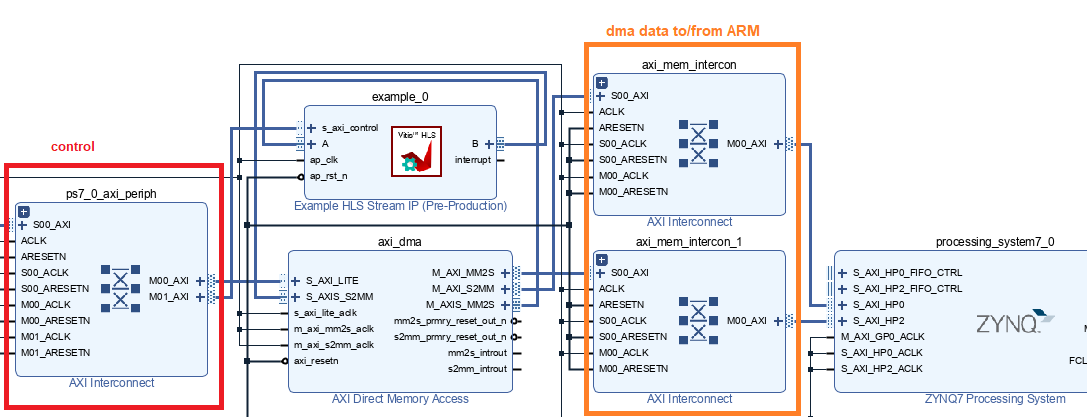

You'll see three AXI Interconnect blocks. One at the left and two at the right side.

The left one is an AXI Lite block, where non-DMA control messages are exchanged with the ARM. This is for any info, except the input- and output data streams.

The IP streams are connected to the DMA block's streaming pipelines. The other sides of the DMA pipelines are connected via the remaining two AXI Interconnects to and from the ARM memory.

image: AXI Lite control of the accelerator IP (red) and the high-speed DMA input and output streams (orange)

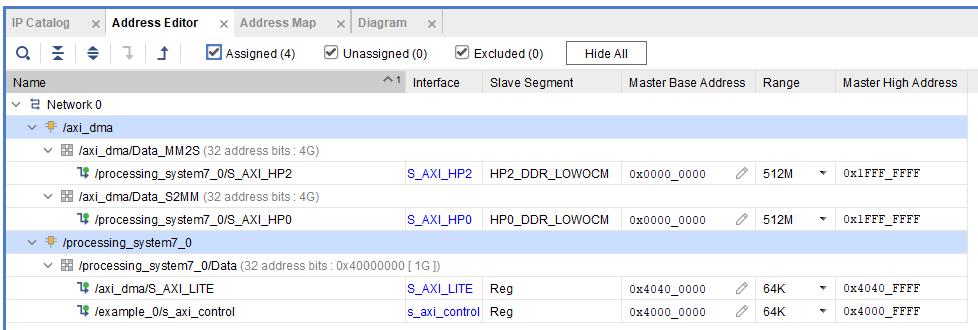

Memory Map Addresses

The DMA section shows the memory area for input and output data, using high performance channels.

The section underneath that shows the normal performance channels used for controlling DMA and Accelerator IP.

You can collect the design implementation files that need to be uploaded to the PYNQ board using the script I created for that.

Next post, this design gets loaded and we'll execute the hardware accelerated function from software.